前言:

最近看到群里面有些萌新在進行討論數(shù)字電路中的復(fù)位邏輯,所以專門寫一篇討論復(fù)位的文章,希望能幫助大家理解復(fù)位。

引言:

在IC設(shè)計中,把復(fù)位和時鐘電路稱為最重要的兩個電路一點也不為過。前者復(fù)位電路把IC設(shè)計的電路引導(dǎo)到一個已知的狀態(tài),后者時鐘電路給IC設(shè)計的電路提供澎湃的心跳動力。同時,這兩者主要作用于電路中的時序元件。對于時序元件,不可避免地會有一些信號時間上額外的要求。

正文:

復(fù)位電路的作用:

(1)在仿真時:使仿真的電路進入規(guī)定的初始化狀態(tài)或者其他預(yù)知的狀態(tài),基于此狀態(tài)下,電路進行狀態(tài)變換。如果仿真中時序元件沒有復(fù)位電路,從波形圖上只能看到時序單元周圍邏輯都是X標(biāo)紅的狀態(tài)。

(2)在IC設(shè)計中:復(fù)位信號可以讓設(shè)計的硬件電路進入一個穩(wěn)定且狀態(tài)確定的狀態(tài),避免因為上電后電路進入到隨機的狀態(tài)而硬件死機。如果用示波器捕捉內(nèi)部時序單元的信號狀態(tài),信號為高低電平之一,只是高低電平的信號可能不符合設(shè)計的預(yù)期。

PS:對于仿真時候的信號未知X狀態(tài)和IC設(shè)計中的高低電平。可以得出結(jié)論:在Verilog語法中,用仿真X狀態(tài)表示物理時序單元電路當(dāng)前狀態(tài)未知,信號可能為高或低電平。

PS:由上,是否電路中所有的單元都需要復(fù)位信號?

答:不是,首先組合邏輯電路是不需要復(fù)位信號的。其次不需要立刻進入明確狀態(tài)的電路:數(shù)據(jù)流水線寄存器、數(shù)據(jù)移位寄存器等也不需要復(fù)位信號。

復(fù)位電路的分類:

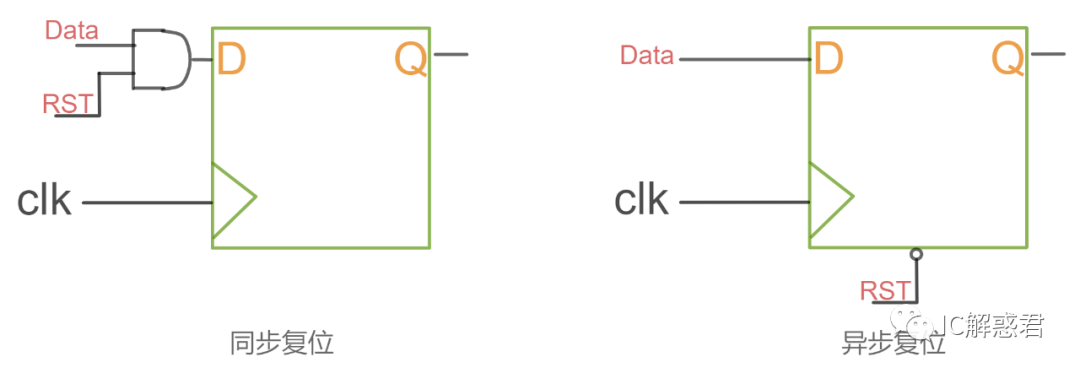

對于電路中的時序元件,把復(fù)位信號受到時鐘的控制和復(fù)位信號不受時鐘的控制兩種電路分別稱為同步復(fù)位電路和異步復(fù)位電路。如下圖:

同步復(fù)位:

在同步復(fù)位的電路中,只有當(dāng)時鐘到來時才會把復(fù)位或者數(shù)據(jù)信息傳輸?shù)郊拇嫫鲀?nèi)部,影響寄存器內(nèi)部的狀態(tài)變換。如上圖所示,在同步復(fù)位電路中,復(fù)位信號本質(zhì)上其實就是一組數(shù)據(jù)信號。復(fù)位和數(shù)據(jù)信號都需要在時鐘的驅(qū)動下進行傳輸。所以此處的同步復(fù)位電路默認(rèn)就有了優(yōu)先級(時鐘>復(fù)位>數(shù)據(jù))。

同步復(fù)位的優(yōu)點:

(1)在同步復(fù)位電路下,復(fù)位和數(shù)據(jù)信號都受到時鐘信號的控制,所以同步復(fù)位一般可以確保電路是一個同步電路(漫談IC亞穩(wěn)態(tài))。

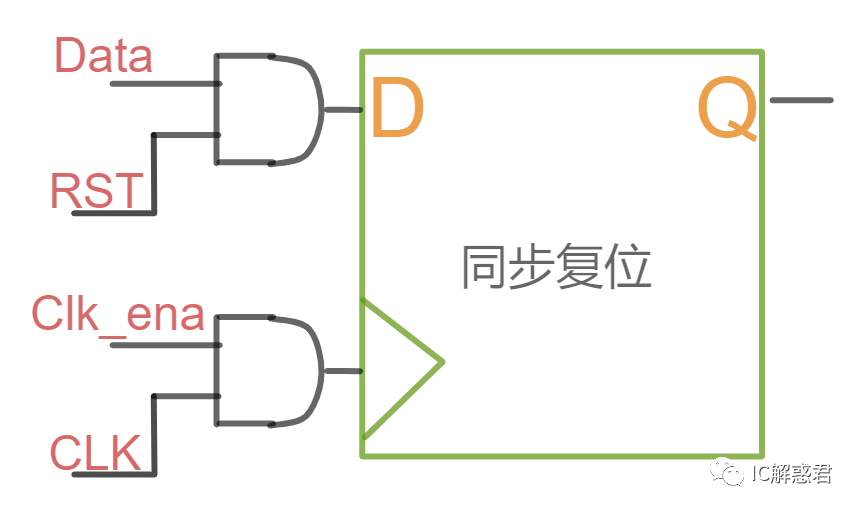

(2)在ASIC設(shè)計中,同步電路一般可以綜合為更小的同步觸發(fā)器(因為觸發(fā)器沒有包含復(fù)位邏輯),但是在FPGA設(shè)計中并不如此,一般FPGA的時序元件為帶異步復(fù)位的觸發(fā)器(也有同步觸發(fā)器,視廠家而定)。如果在FPGA設(shè)計中使用同步復(fù)位,其消耗的資源相對較多。

(3)由于觸發(fā)器的跳轉(zhuǎn)只在時鐘的邊沿,所以觸發(fā)器可以在一定程度上過濾電路毛刺。進而如果復(fù)位由電路內(nèi)部的邏輯控制,在這種情況下可以在設(shè)計中使用同步復(fù)位:通過可以在一定程度上過濾電路毛刺的特性,過濾掉內(nèi)部電路邏輯產(chǎn)生的毛刺,使設(shè)計更魯棒。

同步復(fù)位的缺點:

(1)同步復(fù)位需要較長的保持復(fù)位狀態(tài)時間(最小也要大于時鐘周期),保證同步復(fù)位信號可以到達(dá)每一個寄存器并且要在有效時鐘沿之前到達(dá)(在真正設(shè)計使用的時候還需要考慮時鐘偏斜、組合邏輯延時、復(fù)位延時等,即:同步復(fù)位信號時長> 時鐘周期 + 時鐘偏斜 + 組合邏輯延時)。

(2)在低功耗設(shè)計中,同步復(fù)位一般不能用于門控時鐘控制的電路。因為同步復(fù)位電路中,主要靠時鐘驅(qū)動復(fù)位和數(shù)據(jù)。當(dāng)復(fù)位發(fā)出時,有可能時序電路此時并沒有時鐘驅(qū)動,那么此時的復(fù)位就不能完成。

異步復(fù)位:

擁有異步復(fù)位的寄存器在設(shè)計的時候就已經(jīng)多了一個復(fù)位引腳。通過觸發(fā)該引腳的狀態(tài)可以在任何時候進行異步復(fù)位電路中寄存器。此時異步復(fù)位電路的默認(rèn)優(yōu)先級為:(復(fù)位>時鐘>數(shù)據(jù))(如上上圖)。

異步復(fù)位的優(yōu)點:

(1)異步復(fù)位的復(fù)位邏輯和數(shù)據(jù)邏輯沒有任何關(guān)系,所以相比同步復(fù)位,能夠使數(shù)據(jù)路徑更好地收斂。(上上圖對比)

(2)不用在時鐘的控制下進行復(fù)位,所以對于剛才所提到的低功耗設(shè)計中,可以達(dá)到無時鐘復(fù)位的效果[注意:寄存器復(fù)位后的正常狀態(tài)恢復(fù)需要時鐘參與]。

異步復(fù)位的缺點:

(1)因為異步復(fù)位不受時鐘的控制,所以當(dāng)電路復(fù)位引腳有毛刺的時候,會引起電路的異常復(fù)位。

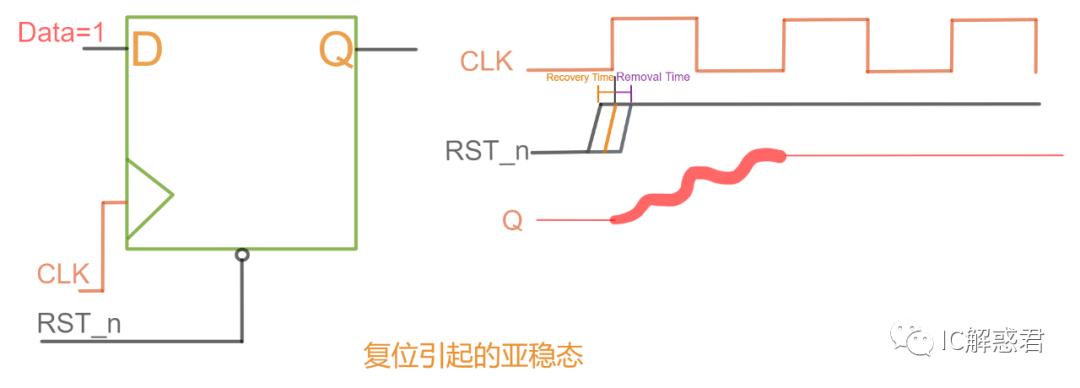

(2)在異步復(fù)位的時候,如果釋放復(fù)位信號在時鐘有效邊沿周圍。那么可能會引起時序單元的輸出出現(xiàn)亞穩(wěn)態(tài),導(dǎo)致電路亞穩(wěn)態(tài)傳播。如下圖:

如圖所示:

復(fù)位信號在時鐘有效沿之前Recovery Time時間內(nèi)釋放可能會引起觸發(fā)器輸出亞穩(wěn)態(tài)。

復(fù)位信號在時鐘有效沿之后RemovalTime時間內(nèi)釋放也可能會引起觸發(fā)器輸出亞穩(wěn)態(tài)。

對比set up time&hold time和此處的Recovery time &Removaltime,可以發(fā)現(xiàn)對于觸發(fā)器來說,輸入信號(Data 和 RST_n)都需要對于時鐘信號沿保持穩(wěn)定的一個時間窗口,否則觸發(fā)器可能會導(dǎo)致亞穩(wěn)態(tài)的輸出。為了避免觸發(fā)器的亞穩(wěn)態(tài),就需要保證不要在觸發(fā)器的這幾個時間窗內(nèi)信號有變化。(漫談STA-setup/hold time)

結(jié)合同步復(fù)位和異步復(fù)位的優(yōu)點可以得到:

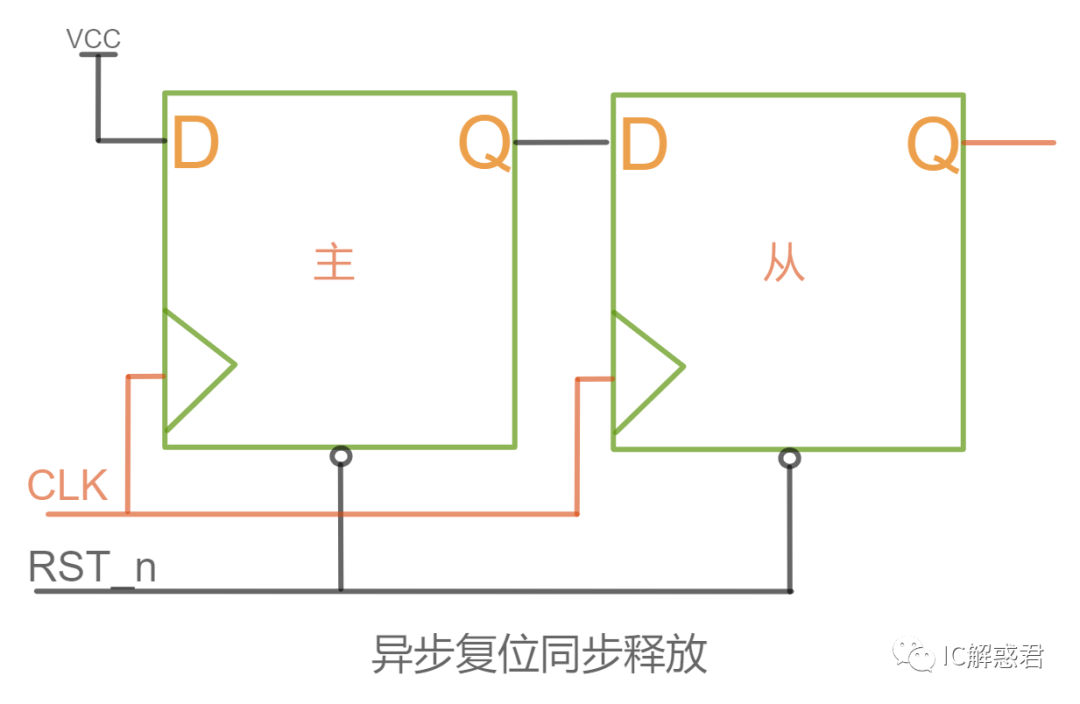

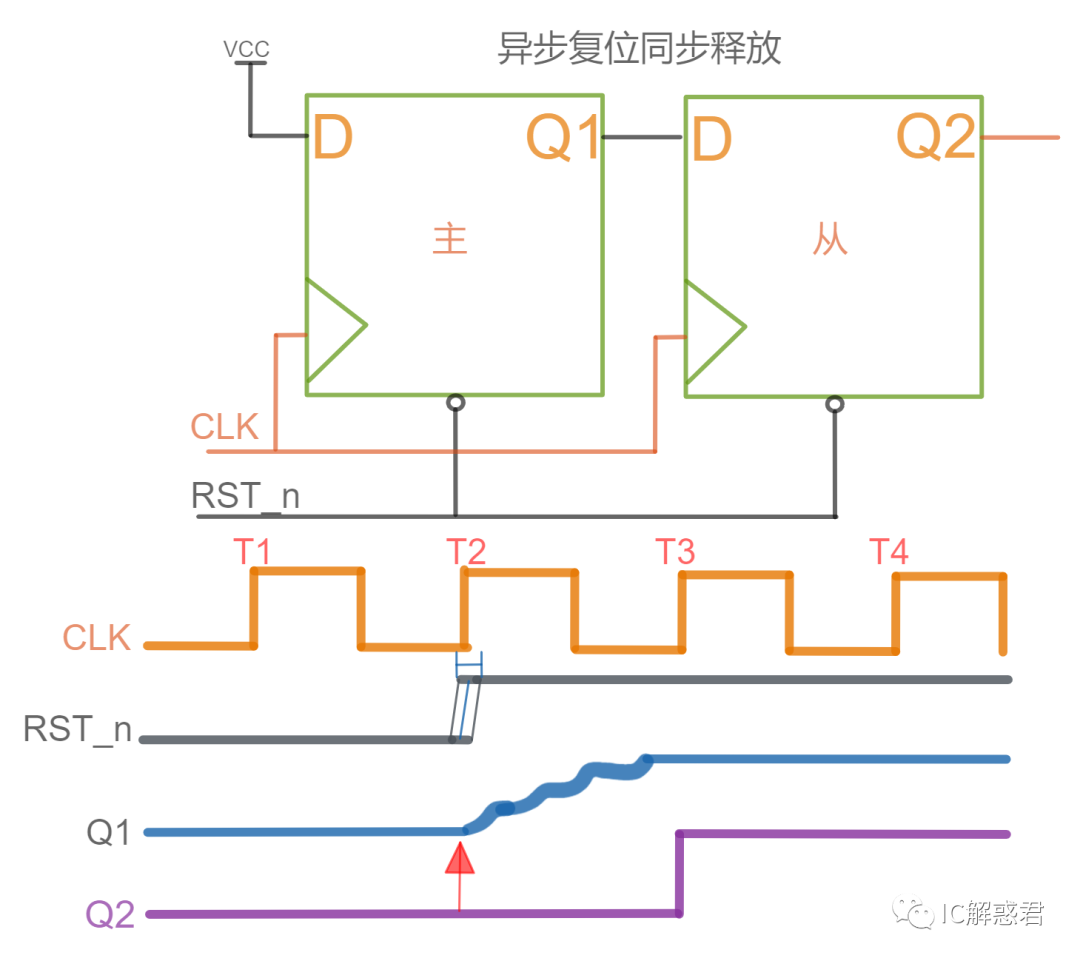

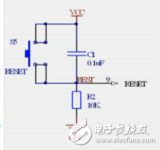

異步復(fù)位同步釋放電路:如下圖

RST_n信號同時復(fù)位這兩個觸發(fā)器,這一對觸發(fā)器的輸出信號傳輸并驅(qū)動電路中的其他時序元件完成復(fù)位,最后使整個相連接的設(shè)計進行復(fù)位。

很明顯可以看出這兩個觸發(fā)器就是所謂的同步器邏輯。在進行數(shù)據(jù)跨時鐘處理的時候可以通過該同步器邏輯將一個時鐘域的信號傳輸?shù)搅硪粋€時鐘域。

如上圖所示:

當(dāng)復(fù)位信號被撤銷時:RST_n [0->1],此時數(shù)據(jù)VCC將在時鐘的控制下進入主觸發(fā)器。如果此時復(fù)位信號被撤銷時候恰好碰到時鐘的有效沿引起主觸發(fā)器的亞穩(wěn)態(tài)。但是此時從觸發(fā)器在時鐘控制下,輸入的是主觸發(fā)器輸出的復(fù)位穩(wěn)定值。

如下圖:雖然主觸發(fā)器在T2時刻違背了復(fù)位時間窗口,輸出了Q1亞穩(wěn)態(tài)的搖擺電平。但是從觸發(fā)器此時的數(shù)據(jù)輸入接收的還是主觸發(fā)器輸出的Q1穩(wěn)態(tài)的復(fù)位狀態(tài)0。所以從觸發(fā)器Q2的輸出是穩(wěn)定的復(fù)位狀態(tài)0。在T3時刻主觸發(fā)器已經(jīng)從亞穩(wěn)態(tài)狀態(tài)恢復(fù),輸出的是穩(wěn)定的工作狀態(tài)電平了(Q1=1)。T3時刻從觸發(fā)器采樣的是穩(wěn)定的工作狀態(tài)電平,輸出也是穩(wěn)定的工作狀態(tài)電平,復(fù)位完成。

PS:有同學(xué)可能會問,RST_n既然對主觸發(fā)器違反復(fù)位時間窗口,對從觸發(fā)器來說,也一樣違反了時間窗口。那從觸發(fā)器為什么就沒有進入亞穩(wěn)態(tài)呢?

答:對于從觸發(fā)器來說,RST_n跳變在其復(fù)位時鐘窗口內(nèi),所以違反了從觸發(fā)器的復(fù)位時間窗口,但是從上圖可以觀察到,從觸發(fā)器在T2時刻時鐘沿的輸入為Q1=0,在T1時刻時鐘沿的輸出為Q2=0,對于從觸發(fā)器來說,復(fù)位前的狀態(tài)和復(fù)位后的狀態(tài)是一樣的。寄存器內(nèi)部的鎖存器不需要跳變來更新自己的狀態(tài)。所以也就不會因為內(nèi)部鎖存器的電平跳變從而導(dǎo)致亞穩(wěn)態(tài)的發(fā)生。

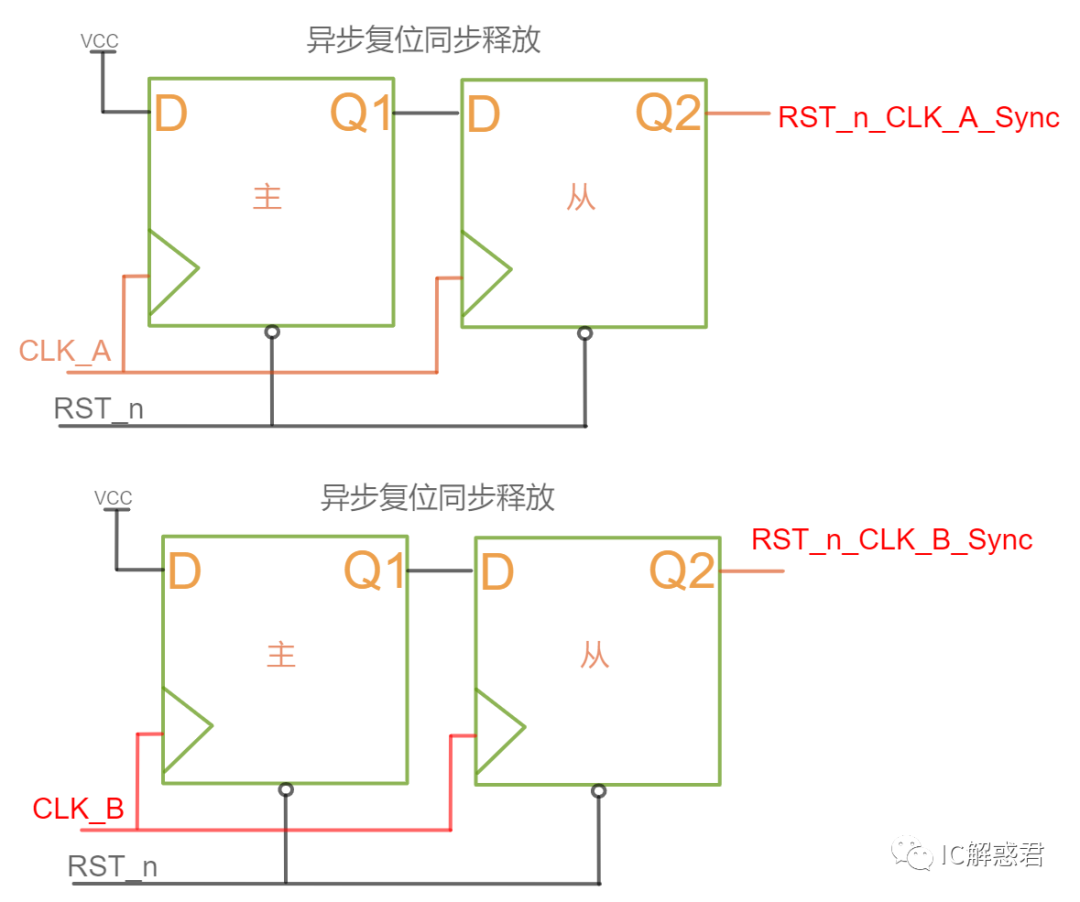

一般來說,完整的一顆SOC芯片內(nèi)部不止有一個時鐘,一般會有多個時鐘。所以此時對每一個時鐘域下的Reset_n信號都有一套異步復(fù)位同步釋放邏輯。來保證在自己的時鐘域下,復(fù)位釋放和時鐘具有同步的關(guān)系,來驅(qū)動該時鐘域下相關(guān)的邏輯和狀態(tài)的變換等操作。如下圖:

結(jié)論:

為了避免在復(fù)位釋放的時候引起電路亞穩(wěn)態(tài),通常采用異步復(fù)位同步釋放的電路。有效的復(fù)位信號可以快速復(fù)位相關(guān)聯(lián)的邏輯且不用等待時鐘的驅(qū)動。同時復(fù)位信號經(jīng)過異步復(fù)位同步釋放的電路之后,復(fù)位信號受到時鐘信號的控制(復(fù)位信號釋放不會在時鐘沿的任意點),有效避免了因異步復(fù)位信號的移除而引起的電路亞穩(wěn)態(tài)情況的出現(xiàn)。

審核編輯:劉清

-

IC設(shè)計

+關(guān)注

關(guān)注

38文章

1354瀏覽量

105501 -

時序電路

+關(guān)注

關(guān)注

1文章

114瀏覽量

21918 -

移位寄存器

+關(guān)注

關(guān)注

3文章

287瀏覽量

22689 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2034瀏覽量

62022 -

時鐘電路

+關(guān)注

關(guān)注

10文章

243瀏覽量

51320

原文標(biāo)題:漫談--復(fù)位reset

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

什么是復(fù)位同步電路 reset synchronizer?

HT66Fx0系列MCU的Reset復(fù)位電路應(yīng)用介紹

復(fù)位穩(wěn)定放大器:The Reset Stabilized A

上電復(fù)位和按鍵復(fù)位區(qū)別

上電時實現(xiàn)延時系統(tǒng)復(fù)位的IC,reset IC

STM32下載后無法自動復(fù)位,需手動復(fù)位 下載程序時,勾選reset and run后仍不可自動復(fù)位

為什么需要復(fù)位電路?漫談復(fù)位reset

為什么需要復(fù)位電路?漫談復(fù)位reset

評論