今天給大俠帶來Intel altera opencl 入門,話不多說,上貨。

概述

Intel altera 的 OpenCL 主要面向信號(hào)處理類應(yīng)用的客戶,是用C語言開發(fā)FPGA的利器,開放計(jì)算語言(OpenCL)聯(lián)盟著名的公司有 FPGA巨頭Intel altera、兩大顯卡GPU巨頭AMD和英偉達(dá)、CPU巨頭Intel、軟件和服務(wù)器巨頭IBM以及全世界最大的公司Apple(蘋果)等等。不過AMD和英偉達(dá)是用GPU實(shí)現(xiàn)的OpenCL并行運(yùn)算,Intel altera是用FPGA實(shí)現(xiàn)并行運(yùn)算。

1. 系統(tǒng)要求

? Microsoft 64-bit Windows 7專業(yè)版或者更高。

? 對(duì)于Windows操作系統(tǒng), 要安裝微軟公司的Visual Studio 2010或者2012專業(yè)版(推薦)。

或者:

? Red Hat Enterprise 64-bit Linux (RHEL) 5或者6。

? 對(duì)于Linux操作系統(tǒng), 安裝操作系統(tǒng)過程中要把C編譯器包括GCC勾選上。

2.安裝Altera的軟件和搭建OpenCL環(huán)境(以Windows為例,Linux也類似):

?安裝Quartus II 13.1 Update4(或者14.0)

?安裝Altera OpenCL 13.1 Update4(AOCLSetup-13.1.4.182.exe)(或者14.0)

設(shè)置環(huán)境變量(基于默認(rèn)的安裝路徑):

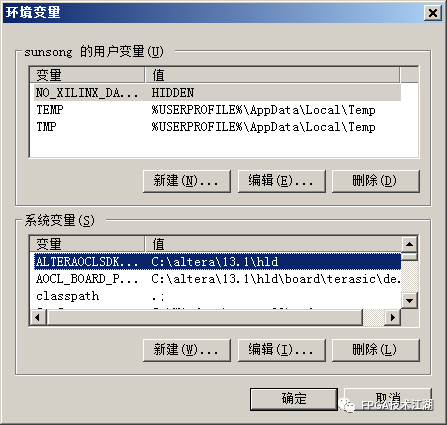

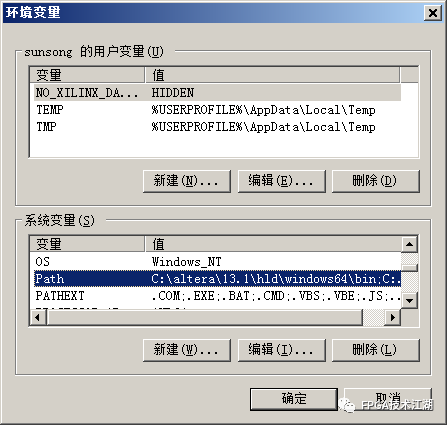

變量和值如下:

ALTERAOCLSDKROOT和C:altera13.1hld(或者C:altera14.0hld)

PATH和C:altera13.1hldwindows64in(或者C:altera14.0hldin;C:altera14.0hldhostwindows64in)

LM_LICENSE_FILE和c:alteralicense.dat

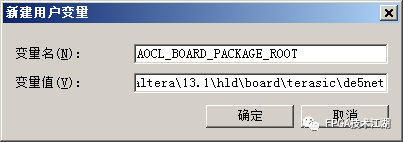

參考下圖:

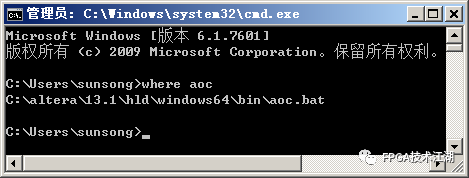

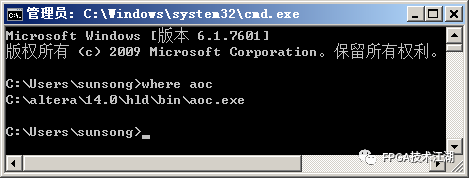

然后在命令行里面運(yùn)行where aoc,測(cè)試一下軟件是否安裝正確以及環(huán)境變量是否設(shè)置正確,如果正確,如下圖;如果不正確,修改錯(cuò)誤再來。

或者(14.0)

3.開發(fā)板環(huán)境的安裝和測(cè)試(以臺(tái)灣友晶的DE5-Net開發(fā)板為例,不過沒有開發(fā)板也可以,開發(fā)板不是必需的):

1)。 準(zhǔn)備工作:下載DE5-Net開發(fā)板的全套軟件安裝包,http://www.terasic.com/downloads 。.. 5NET_openCL_BSP.zip 136MB,把里面的terasic文件夾解壓縮到C:altera13.1hldoard下。

設(shè)置DE5-Net開發(fā)板的環(huán)境變量:

變量和值如下:

AOCL_BOARD_PACKAGE_ROOT和C:altera13.1hldoard erasicde5net

參考下圖:

然后在命令行里面運(yùn)行aocl install來安裝開發(fā)板驅(qū)動(dòng)。

關(guān)閉你的PC,安裝和連接開發(fā)板硬件后,重新開機(jī),在命令行里面運(yùn)行aoc --list-boards,如果硬件安裝連接成功,會(huì)顯示開發(fā)板名字de5net_a7,如果開發(fā)板不存在,顯示none found。

2)。 測(cè)試開發(fā)板:

在命令行里面運(yùn)行 cd C:altera13.1hldoard erasic estslank,運(yùn)行aocl program blank.aocx,如果開發(fā)板已經(jīng)安裝連接好,aocx里面的sof文件會(huì)通過PCI-E接口下載,并且會(huì)返回成功的信息,如果開發(fā)板不存在或者沒有安裝連接好,會(huì)自動(dòng)解壓縮出reprogram_temp.sof,用戶可以通過USB下載電纜去下載。

備注:沒有開發(fā)板的客戶可以在設(shè)置環(huán)境變量后跳過后面的步驟,繼續(xù)。

4.編譯和測(cè)試OpenCL工程:

1)。 編譯OpenCL工程:

在命令行里面運(yùn)行cd C:altera13.1hldoard erasic estsoardtest進(jìn)入工程文件夾,運(yùn)行aoc boardtest.cl --sw-dimm-partition開始編譯,編譯時(shí)間大約1個(gè)小時(shí),最終產(chǎn)生的boardtest.aocx里面包含了sof文件,可以給開發(fā)板編程進(jìn)去。

2)。 測(cè)試OpenCL工程(通過開發(fā)板):

在命令行里面運(yùn)行 cd C:altera13.1hldoard erasic estslank,運(yùn)行aocl program boardtest.aocx,如果開發(fā)板已經(jīng)安裝連接好,aocx里面的sof文件會(huì)通過PCI-E接口下載,并且會(huì)返回成功的信息,如果開發(fā)板不存在或者沒有安裝連接好,會(huì)自動(dòng)解壓縮出reprogram_temp.sof,用戶可以通過USB下載電纜去下載。

提示:沒有開發(fā)板的客戶可以跳過上面的步驟,直接編譯下面不需要開發(fā)板的例子,有開發(fā)板的客戶可以直接到第五步:

下面完全脫離真實(shí)的開發(fā)板來運(yùn)行Cytech_C5SOC.zip:

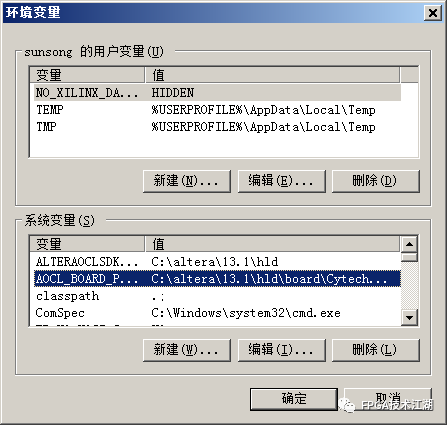

設(shè)置“虛擬”板的環(huán)境變量(替換原來的環(huán)境變量):

變量和值如下:

AOCL_BOARD_PACKAGE_ROOT和 C:altera13.1hldoardCytech_C5SOC

參考下圖:

解壓縮Cytech_C5SOC.zip里面的內(nèi)容到C:altera13.1hldoard(也可以是其它文件夾),把例子exm_opencl_hello_world_windows64.zip里面的hello_world.cl也復(fù)制到這個(gè)文件夾下,在命令行里面運(yùn)行cd C:altera13.1hldoard,運(yùn)行aoc hello_world.cl開始編譯。----因?yàn)镃yclone V SOC的5CSXFC6容量比Stratix V的5SGSMD5小幾倍,所以編譯時(shí)間只有20分鐘左右,最終產(chǎn)生的hello_world.aocx里面包含了sof文件,同時(shí)也產(chǎn)生了轉(zhuǎn)換后的.V源碼和整個(gè)編譯后的Quartus II完整工程,包括大量的底層配套的各種IP源碼。

再演示3個(gè)不同的例子,分別是vector_add、matrix_mult和FFT,也是完全脫離真實(shí)的開發(fā)板來運(yùn)行:

不改變上面“虛擬”板的環(huán)境變量,目的是繼續(xù)使用Cyclone V SOC的5CSXFC6,可以產(chǎn)生為這個(gè)系列優(yōu)化的源碼。

分別解壓縮3個(gè)zip例子到C:altera13.1hldoard(也可以是其它目錄),然后分別在在命令行里面:

1.運(yùn)行cd C:altera13.1hldoardvector_adddevice,然后運(yùn)行aoc vectorAdd.cl開始編譯。

2.運(yùn)行cd C:altera13.1hldoardmatrix_multdevice,然后運(yùn)行aoc matrix_mult.cl開始編譯。

3.運(yùn)行cd C:altera13.1hldoardfft1ddevice,然后運(yùn)行aoc fft1d.cl開始編譯。

3個(gè)例子之間沒有任何聯(lián)系,可以單獨(dú)運(yùn)行,如果你的PC內(nèi)存足夠大,可以一起運(yùn)行。

在產(chǎn)生的不同Quartus II工程中,可以找到matrix_mult.v、vectorAdd.v和fft1d.v這些轉(zhuǎn)換出的源碼。特別注意的是,這些最終的源碼是acl_kernel_interface接口,這種接口比較簡(jiǎn)單,和FIFO差不多,只不過多了幾個(gè)啟動(dòng)結(jié)束控制線,如start,valid等等。

備注:大家可以把這些源碼復(fù)制到自己的工程中和自己寫的其它邏輯模塊連接起來即可。如果想產(chǎn)生基于Stratix V器件優(yōu)化的源碼,可以在環(huán)境變量的路徑中把臺(tái)灣友晶的DE5-Net開發(fā)板作為虛擬板(也就是恢復(fù)第三步的環(huán)境變量),然后編譯cl文件即可。

5.編譯Host程序:

啟動(dòng)Visual Studio 2012,點(diǎn)擊“文件打開項(xiàng)目”,選擇C:altera13.1hldoard erasic estsoardtesthostoardtest.sln(或者直接在硬盤上雙擊這個(gè)sln文件,VS 2012會(huì)自動(dòng)完成上述步驟),然后點(diǎn)擊“生成生成解決方案”,最后在……h(huán)ostx64Release下產(chǎn)生了boardtest.exe,不過這個(gè)exe不能運(yùn)行,因?yàn)槿鄙賻讉€(gè)dll文件,把C:altera13.1hldwindows64in下的所有的6個(gè)dll文件復(fù)制過來,和這個(gè)exe放在同一個(gè)文件夾下就可以運(yùn)行了。

備注:沒有開發(fā)板的客戶可以跳過上面這個(gè)步驟。

6.查看結(jié)果:

把第四步產(chǎn)生的aocx文件下載到開發(fā)板,成功后會(huì)返回信息,然后運(yùn)行第五步產(chǎn)生的exe即可在PC屏幕上看到開發(fā)板返回的最終結(jié)果。

備注:沒有開發(fā)板的客戶可以跳過上面這個(gè)步驟。

沒有開發(fā)板的客戶只需要走1、2、4步即可。

參考資料、例子和其它:

1.參考資料:http://www.altera.com.cn/product 。.. l/opencl-index.html

網(wǎng)頁最下面3個(gè)入門文檔:

面向OpenCL的Altera SDK開始設(shè)計(jì):aocl_getting_started.pdf

面向OpenCL的Altera SDK編程指南:aocl_programming_guide.pdf

面向OpenCL的Altera SDK優(yōu)化指南:aocl_optimization_guide.pdf

其中13.1版本對(duì)應(yīng)的aocl_getting_started.pdf第8頁是錯(cuò)的,PATH應(yīng)該是C:altera13.1hldwindows64in,14.0里面改正了。

2.Altera目前有13個(gè)OpenCL的例子在http://www.altera.com.cn/support/examples/opencl/opencl.html 里面,上面第4步用到的exm_opencl_hello_world_windows64.zip例子就來自于這個(gè)網(wǎng)頁。

3.Cl文件是OpenCL的源碼文件,aocx是cl文件編譯后的編程文件,里面包括sof文件。PC機(jī)那邊的Host軟件不是必需的,做host軟件僅僅是為了和開發(fā)板通信來獲取開發(fā)板運(yùn)行openCL的信息。沒有開發(fā)板的用戶只要寫一個(gè)cl文件然后自己建立一個(gè)Quartus II工程就可以編譯了,最后產(chǎn)生了轉(zhuǎn)換后的.V源碼和整個(gè)編譯后的Quartus II完整工程,包括大量的底層配套的各種IP源碼。

4.因?yàn)槭孪仍O(shè)置了環(huán)境變量的緣故,所以cl文件放到任何路徑下都可以編譯,編譯后會(huì)在cl文件所在的文件夾里面產(chǎn)生完整的Quartus II整個(gè)工程,里面就有轉(zhuǎn)換后的.v文件。

-

FPGA

+關(guān)注

關(guān)注

1644文章

22009瀏覽量

616594 -

編譯器

+關(guān)注

關(guān)注

1文章

1659瀏覽量

50059 -

OpenCL

+關(guān)注

關(guān)注

2文章

48瀏覽量

33718

原文標(biāo)題:Intel altera opencl 入門

文章出處:【微信號(hào):HXSLH1010101010,微信公眾號(hào):FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Altera Stratix 10和Agilex 7 FPGA的電源管理及配置問題案例

Altera Agilex 3 FPGA和SoC產(chǎn)品介紹

Intel-Altera FPGA:通信行業(yè)的加速引擎,開啟高速互聯(lián)新時(shí)代

Altera大學(xué)成立,助力FPGA教學(xué)發(fā)展與人才培養(yǎng)

英特爾向銀湖資本出售Altera 51%股份

如何下載GPG-PUB-KEY-INTEL-OPENVINO-2021?

Intel為什么在2015年收購(gòu)Altera?現(xiàn)在又為什么拋棄Altera

Altera正式獨(dú)立運(yùn)營(yíng):FPGA行業(yè)格局將迎來新變局

Altera發(fā)布全新合作伙伴加速計(jì)劃

Altera推出解決方案合作伙伴加速計(jì)劃

Altera宣布正式獨(dú)立,結(jié)束與英特爾8年從屬關(guān)系

5CGTFD7D5F27C7N Intel/Altera可編程邏輯器件(CPLD/FPGA)

Intel altera opencl入門

Intel altera opencl入門

評(píng)論