1.1 硬件介紹

我們從原理圖中可以看到 ZYNQ 芯片分為PL和PS,PS端的IO分配相對是固定的,不能任意分配,而且不需要在Vivado軟件里分配管腳,雖然本實(shí)驗(yàn)僅僅使用了PS,但是還要建立一個Vivado工程,用來配置PS管腳。雖然PS端的ARM是硬核,但是在ZYNQ當(dāng)中也要將ARM硬核添加到工程當(dāng)中才能使用。前面章節(jié)介紹的是代碼形式的工程,本章開始介紹ZYNQ的圖形化方式建立工程。

下面介紹FPGA工程師負(fù)責(zé)內(nèi)容。

1.2 Vivado工程建立

1)創(chuàng)建一個名為“ps_hello”的工程,建立過程不再贅述,參考“PL的”Hello World”LED實(shí)驗(yàn)”。

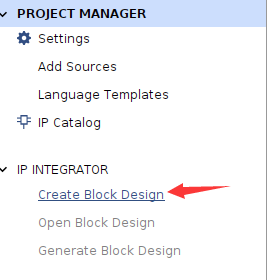

2)點(diǎn)擊“Create Block Design”,創(chuàng)建一個Block設(shè)計(jì)

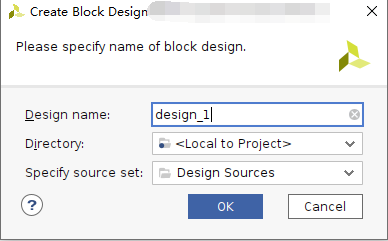

3)“Design name”這里不做修改,保持默認(rèn)“design_1”,這里可以根據(jù)需要修改,不過名字要盡量簡短,否則在Windows下編譯會有問題。

? ? ? ?

? ? ? ?

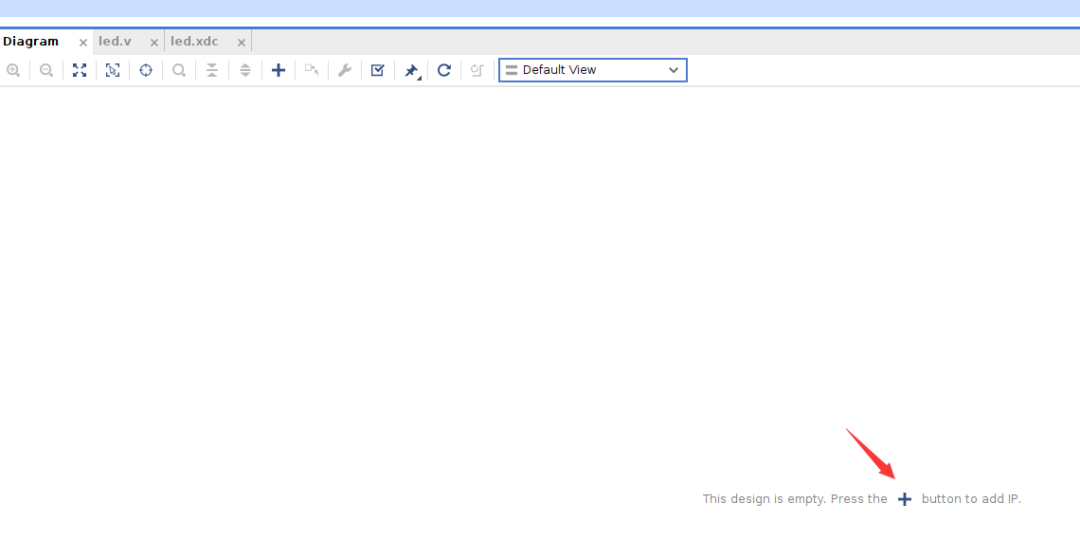

4)點(diǎn)擊“Add IP”快捷圖標(biāo)

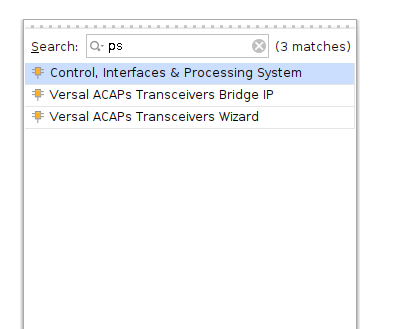

5)搜索“PS”,在搜索結(jié)果列表中雙擊”Control,Interfaces & Processing System”

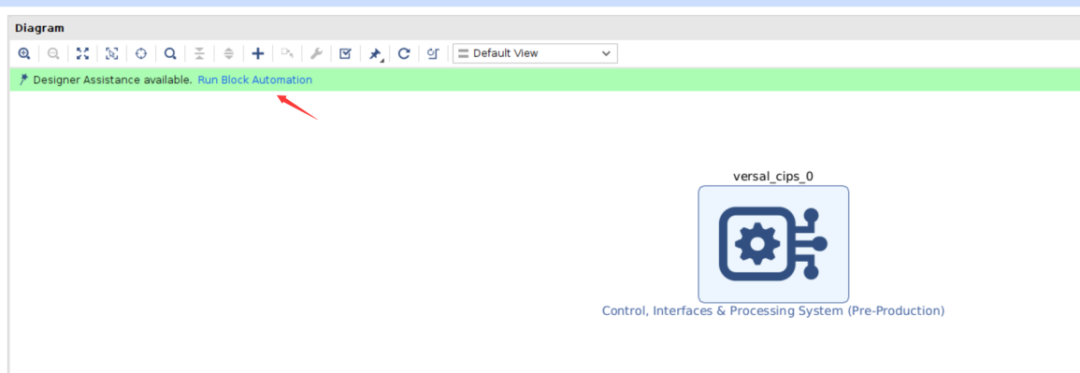

6)點(diǎn)擊Run Block Automation

7)配置如下,點(diǎn)擊OK

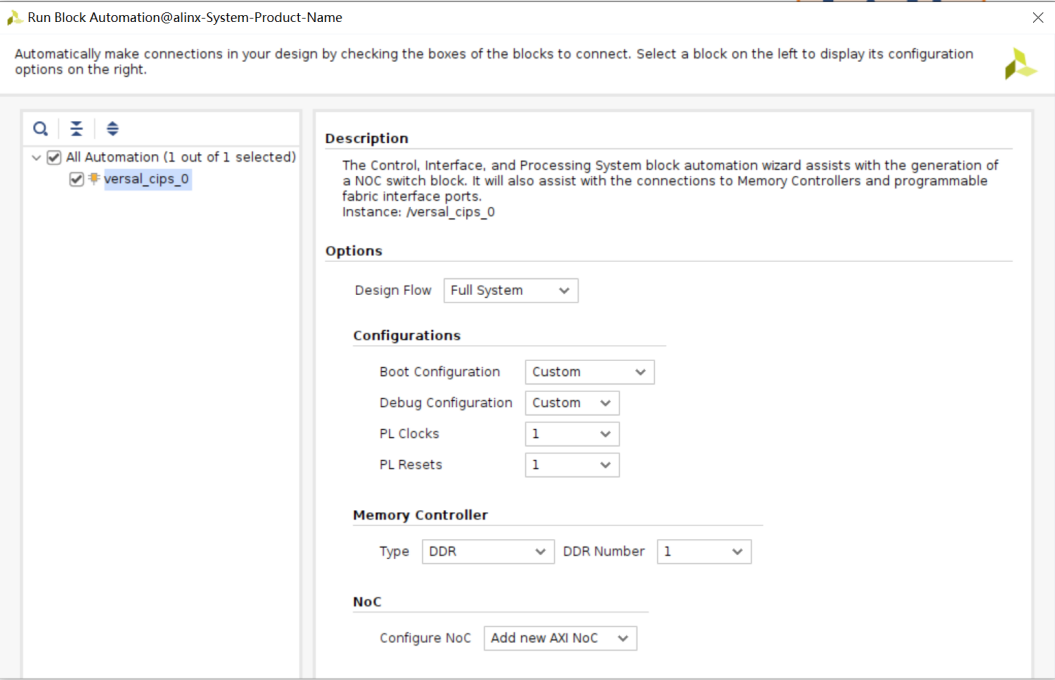

8)自動連接如下

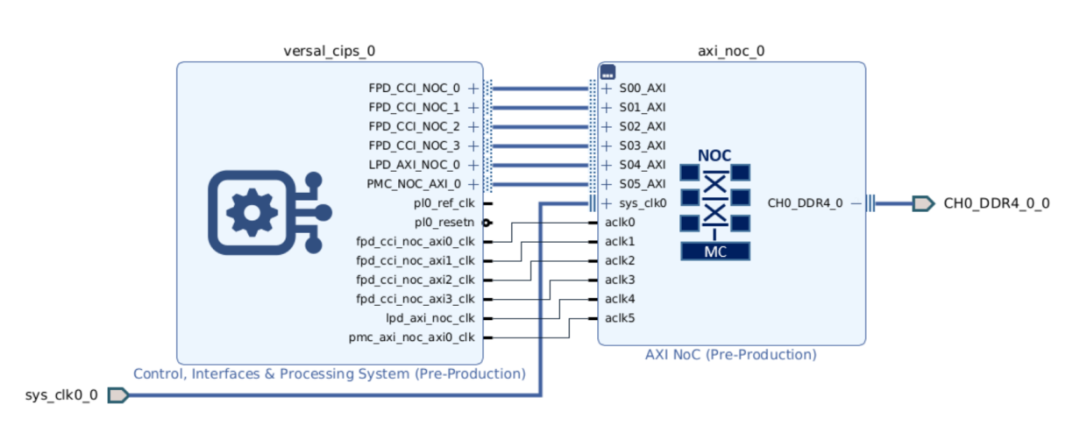

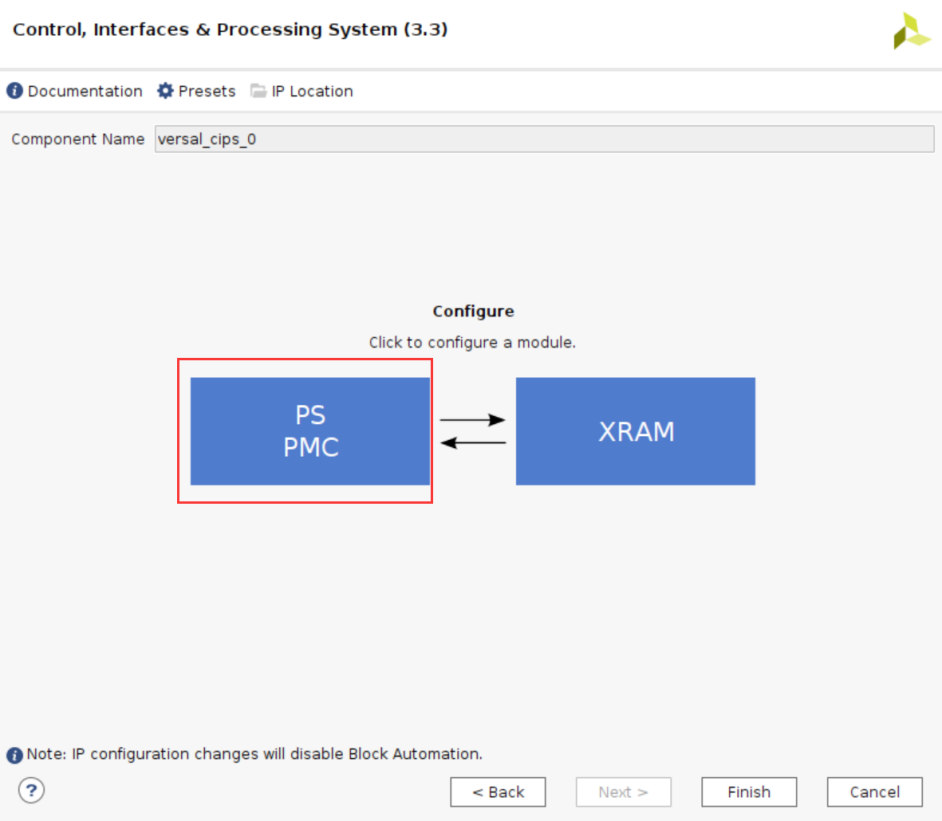

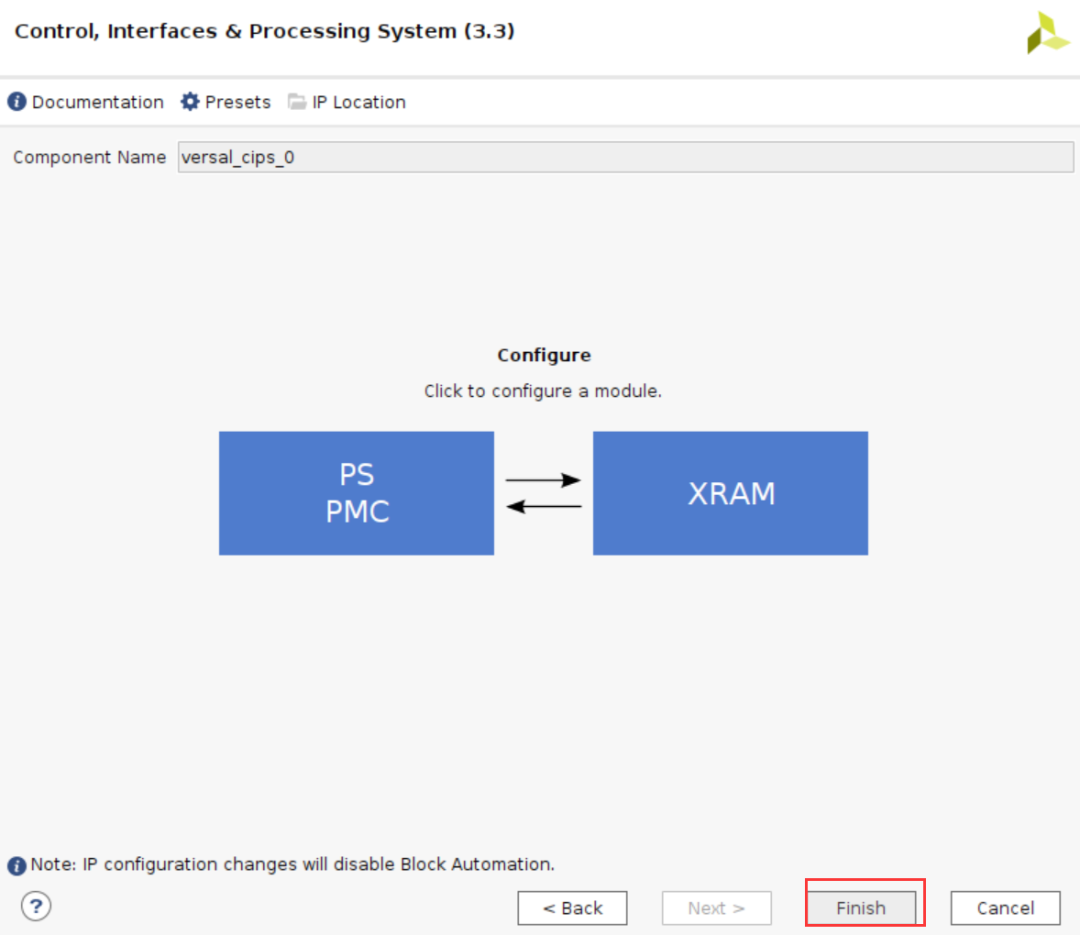

9)雙擊CIPS進(jìn)行配置

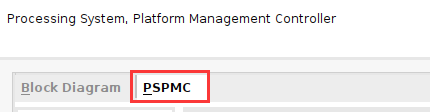

點(diǎn)擊PSPMC進(jìn)行配置

? ?

? ?

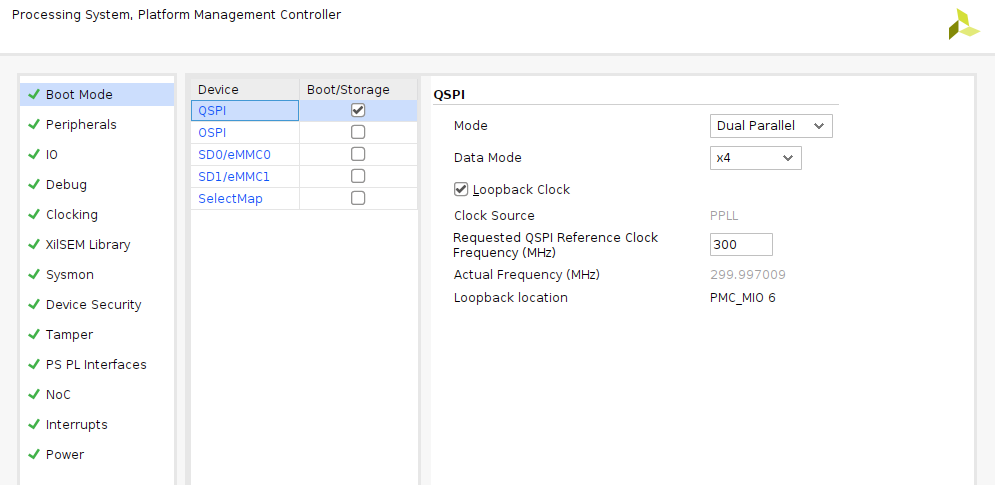

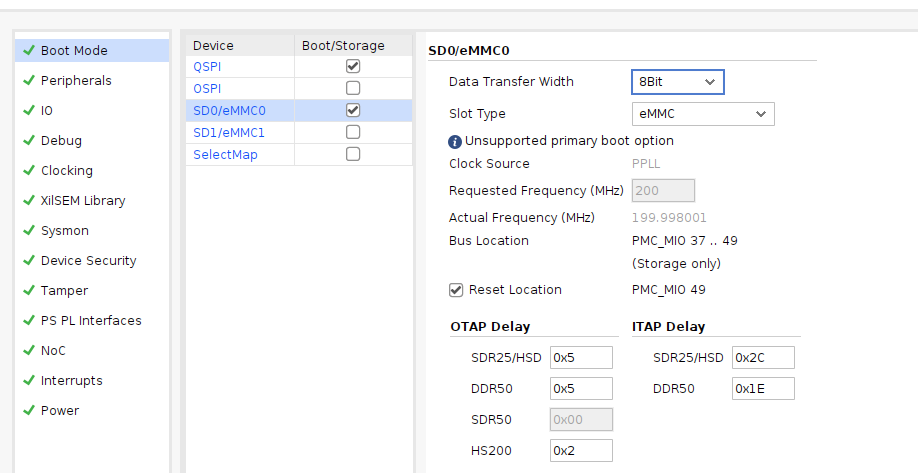

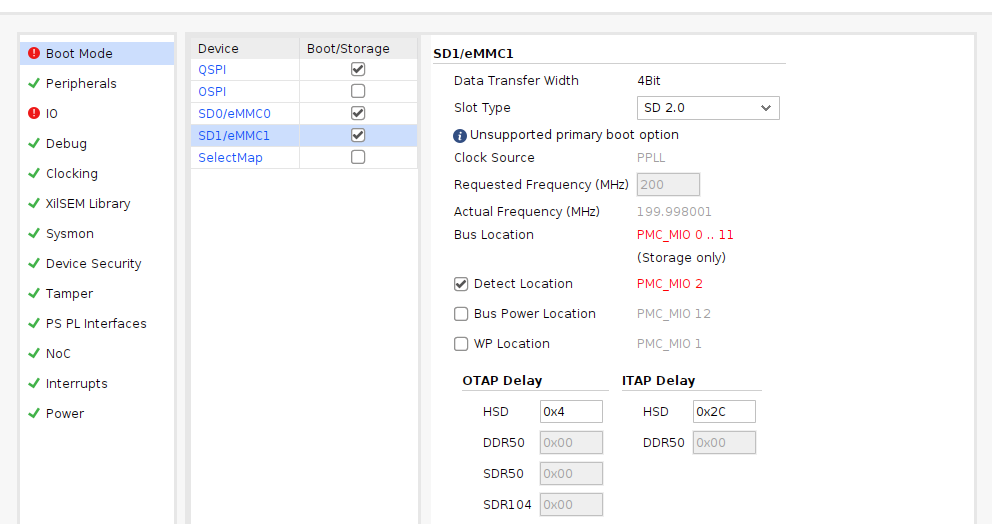

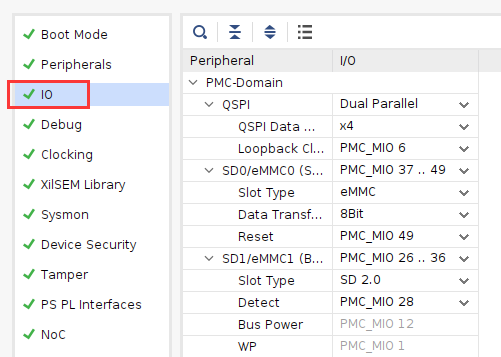

10)配置QSPI,EMMC,SD

選擇相應(yīng)MIO

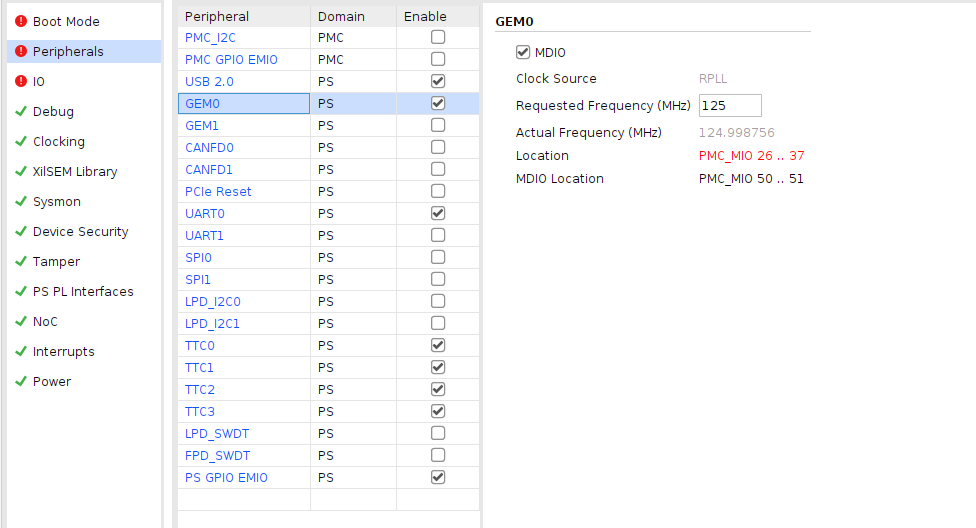

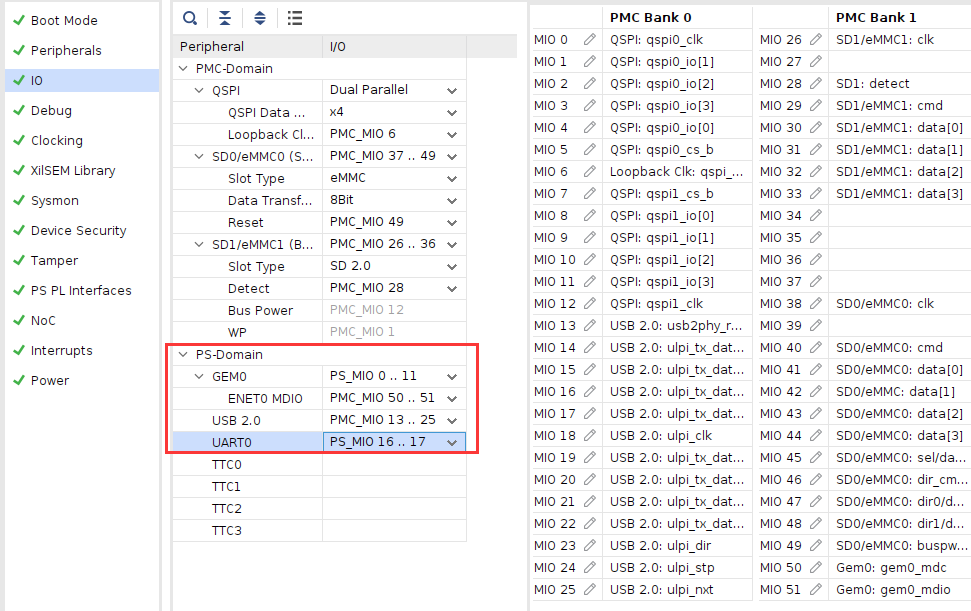

11)勾選USB 2.0,GEM0,UART0,TTC,GPIO等外設(shè)

配置外設(shè)

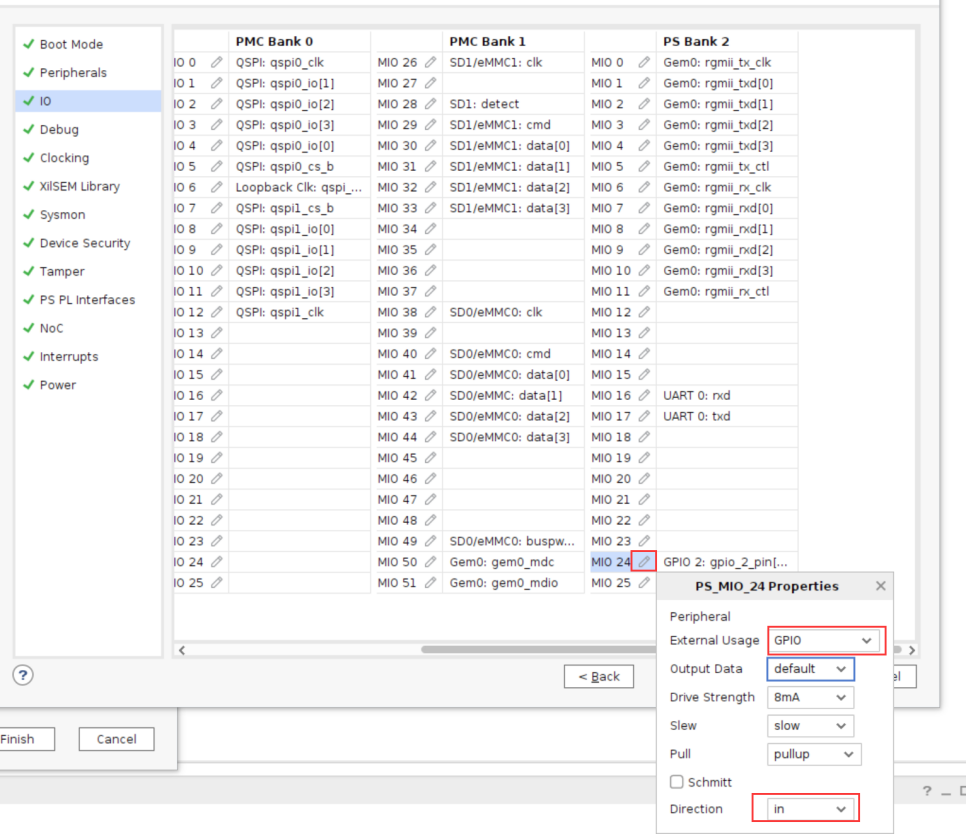

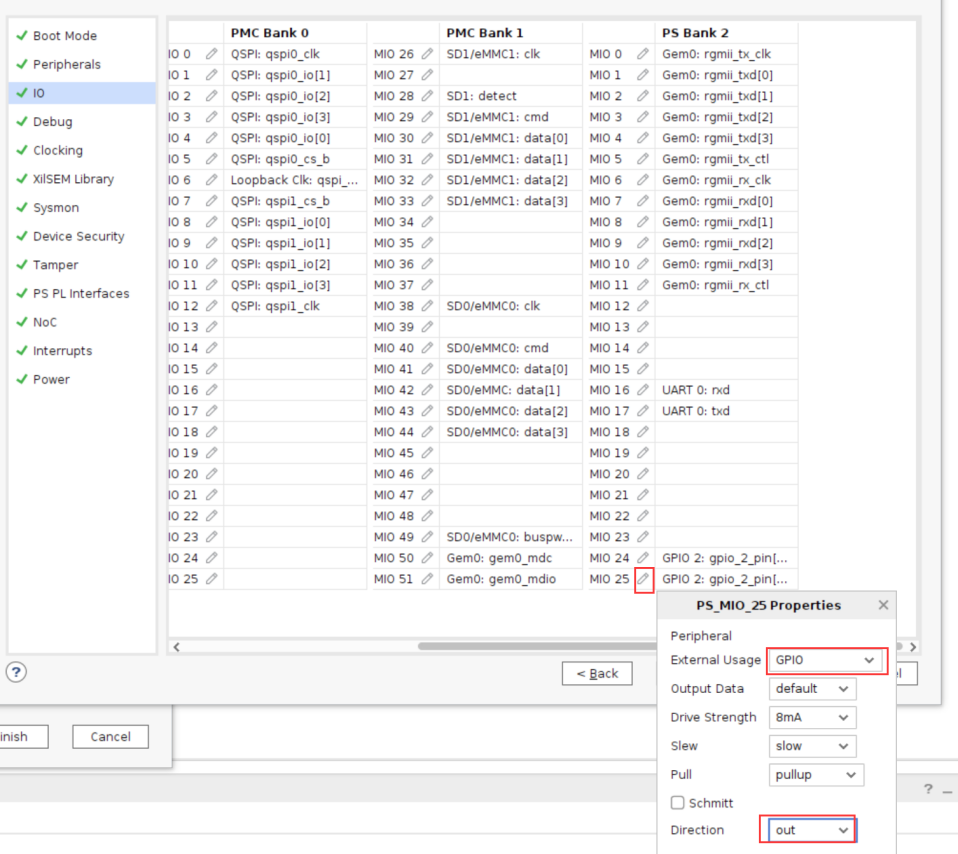

12)將MIO24配置成GPIO輸入,對應(yīng)PS端按鍵,MIO25配置成GPIO輸出,對應(yīng)PS端LED燈

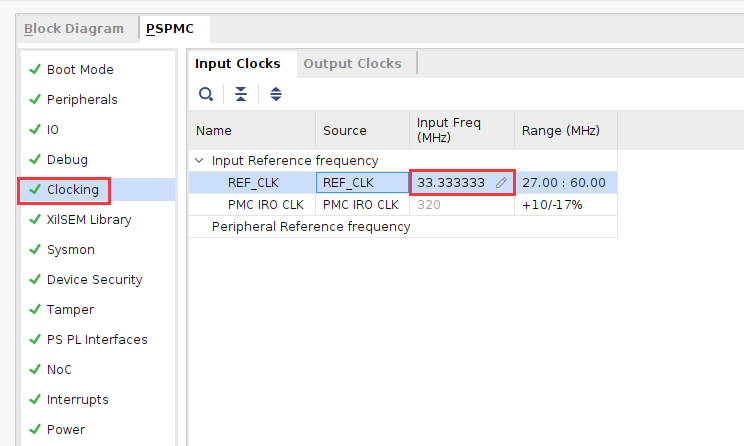

13)在clocking中,將參考時鐘設(shè)置更精確些

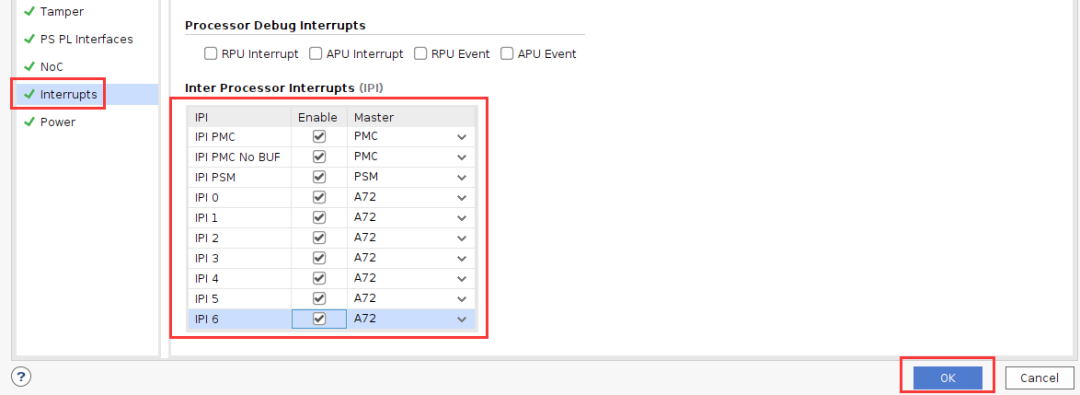

14)將內(nèi)部中斷都勾選上,配置完成,點(diǎn)擊OK

15)點(diǎn)擊Finish

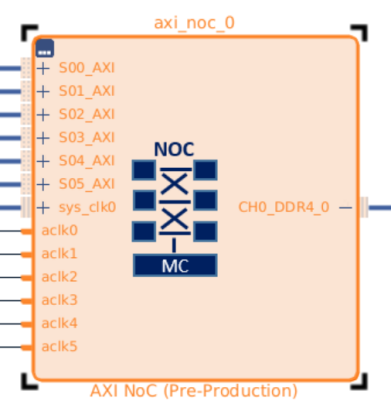

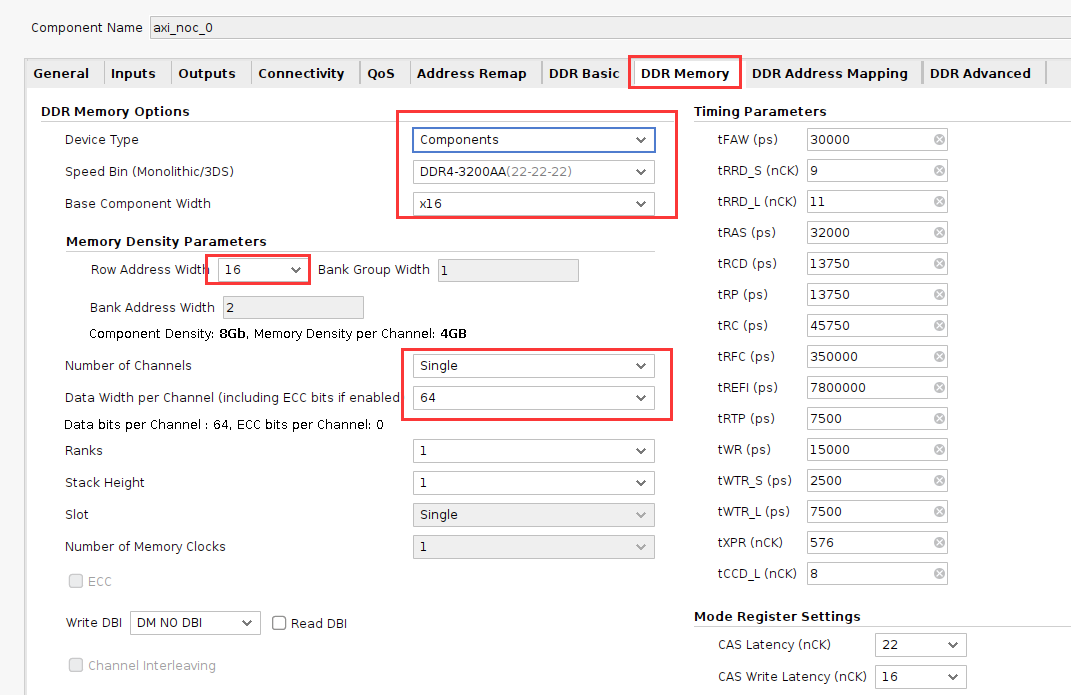

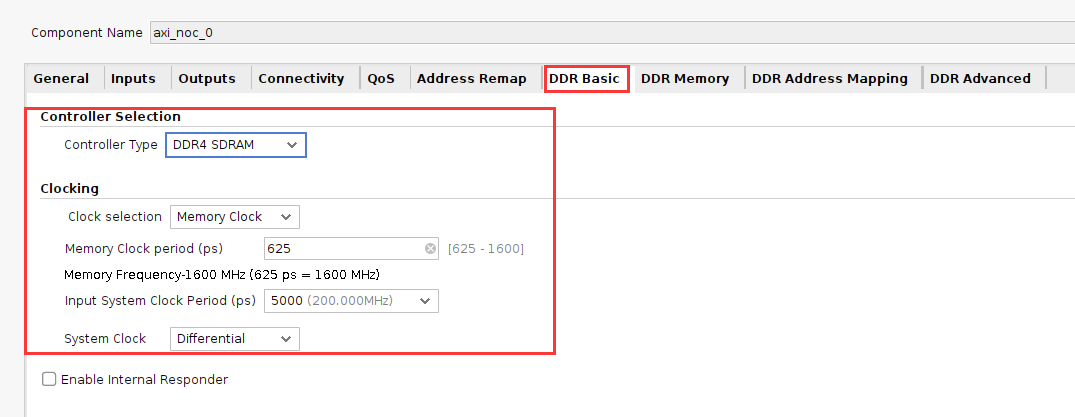

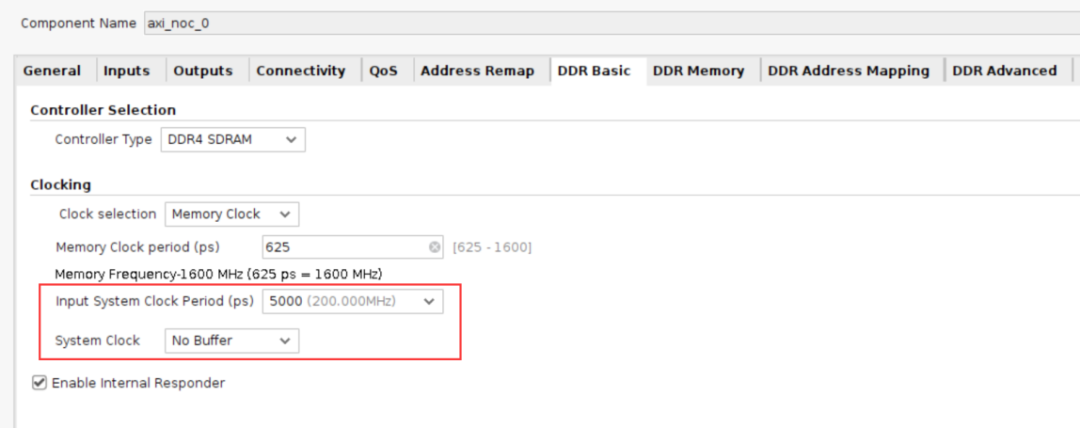

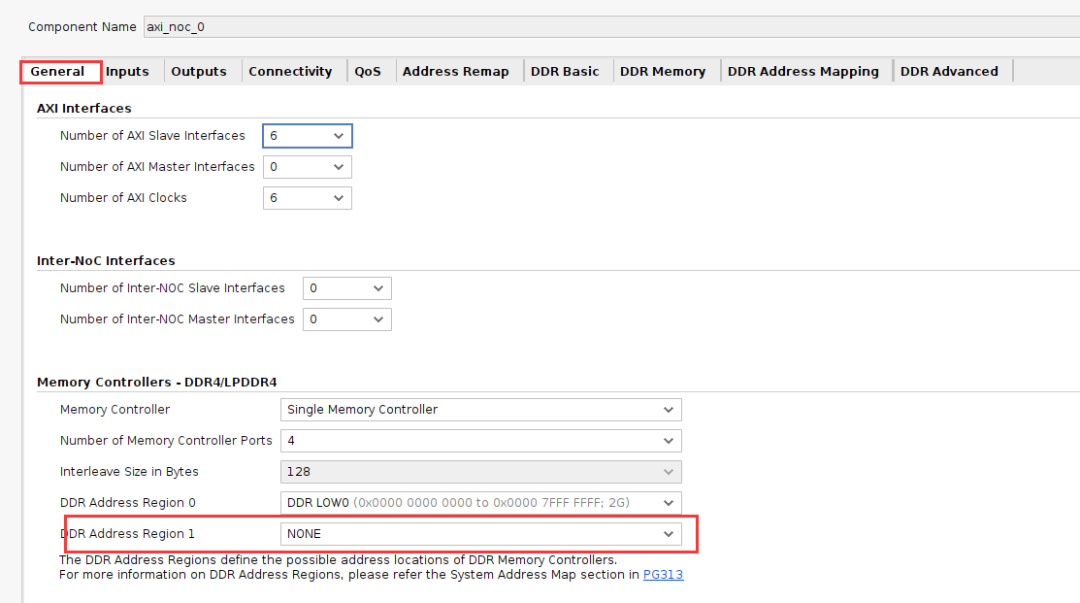

16)雙擊AXI NoC配置DDR4

選擇參考時鐘和system clock

DDR Address Region 1選擇NONE,點(diǎn)擊OK

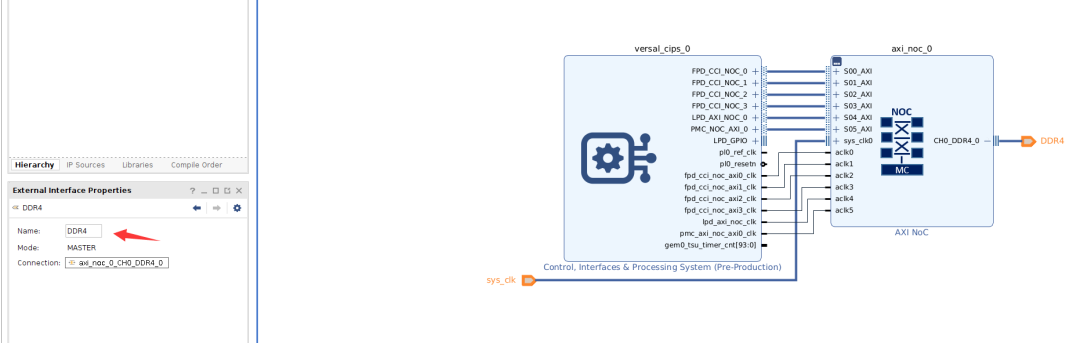

17)修改引腳名稱

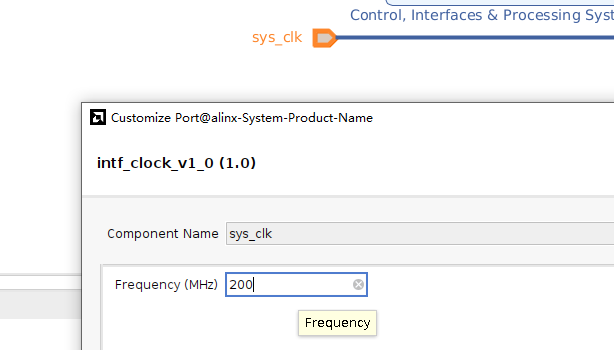

雙擊配置sys_clk的頻率為200MHz

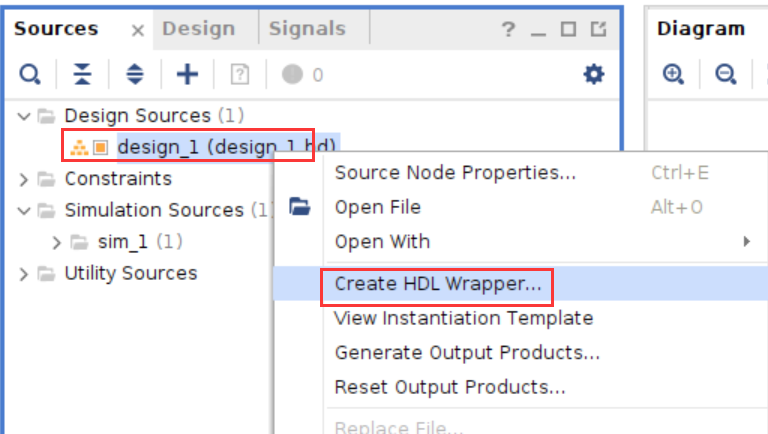

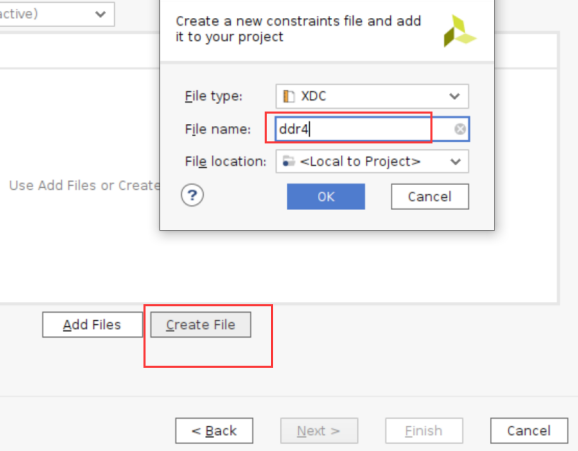

18)選擇Block設(shè)計(jì),右鍵“Create HDL Wrapper...”,創(chuàng)建一個Verilog或VHDL文件,為block design生成HDL頂層文件。

19)保持默認(rèn)選項(xiàng),點(diǎn)擊“OK”

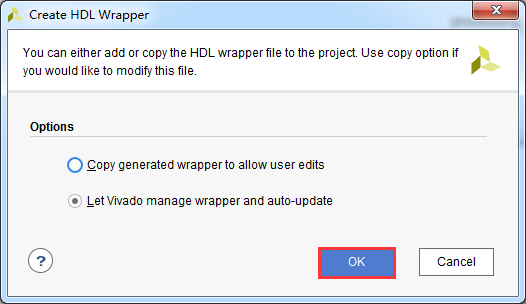

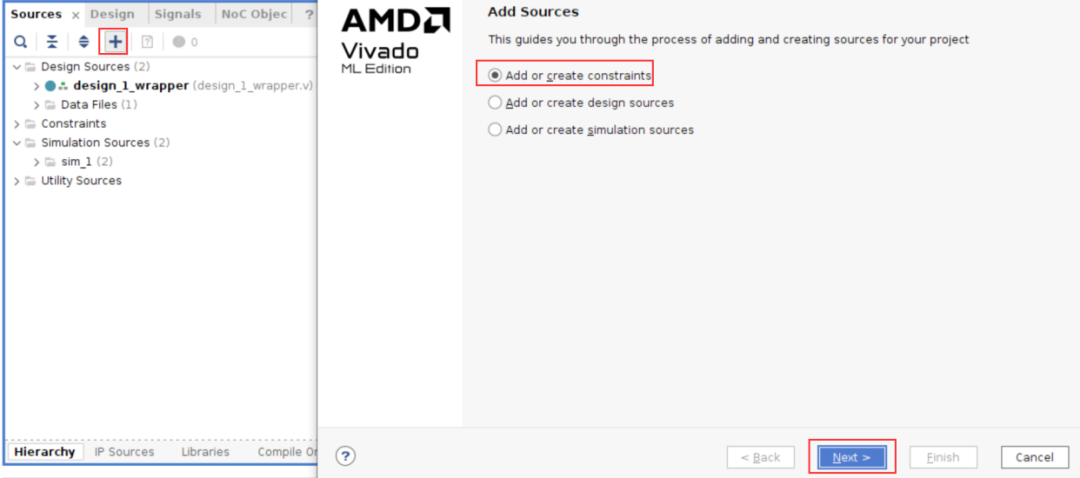

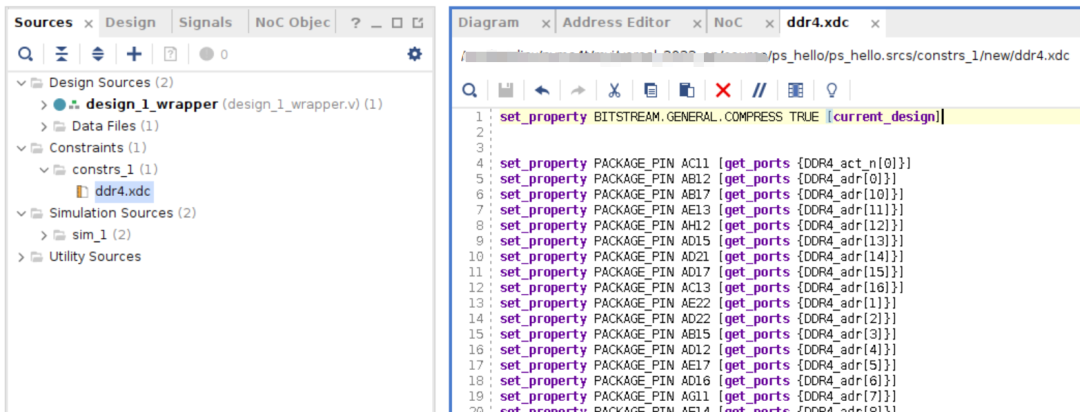

20)添加約束

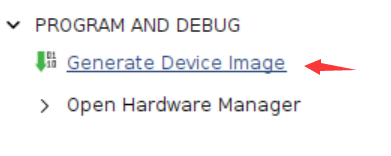

21)Generate Device Image

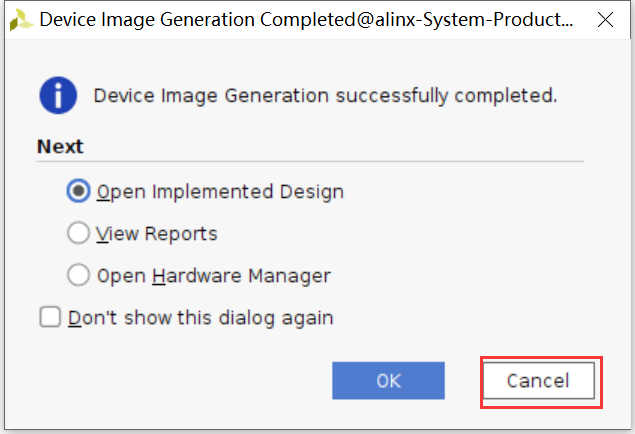

22)完成后取消

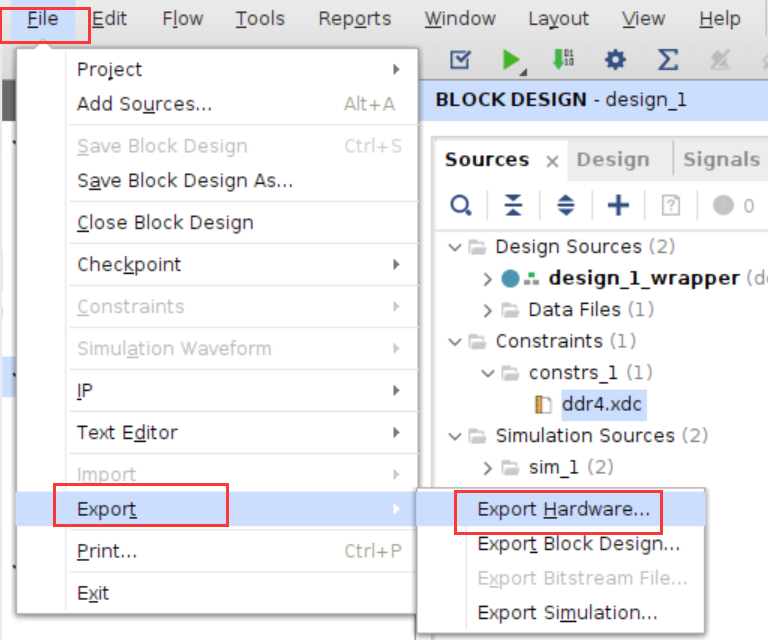

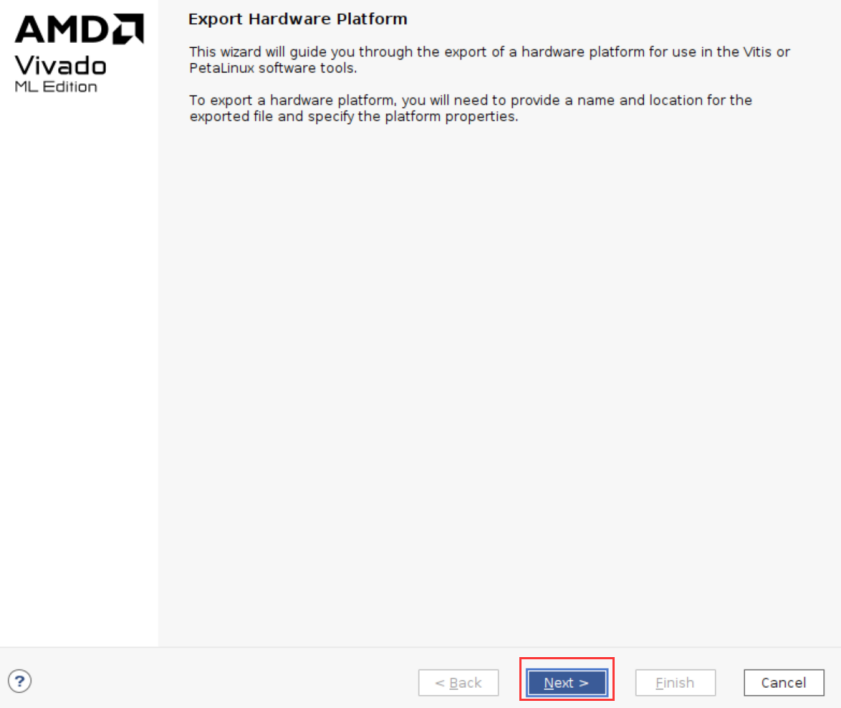

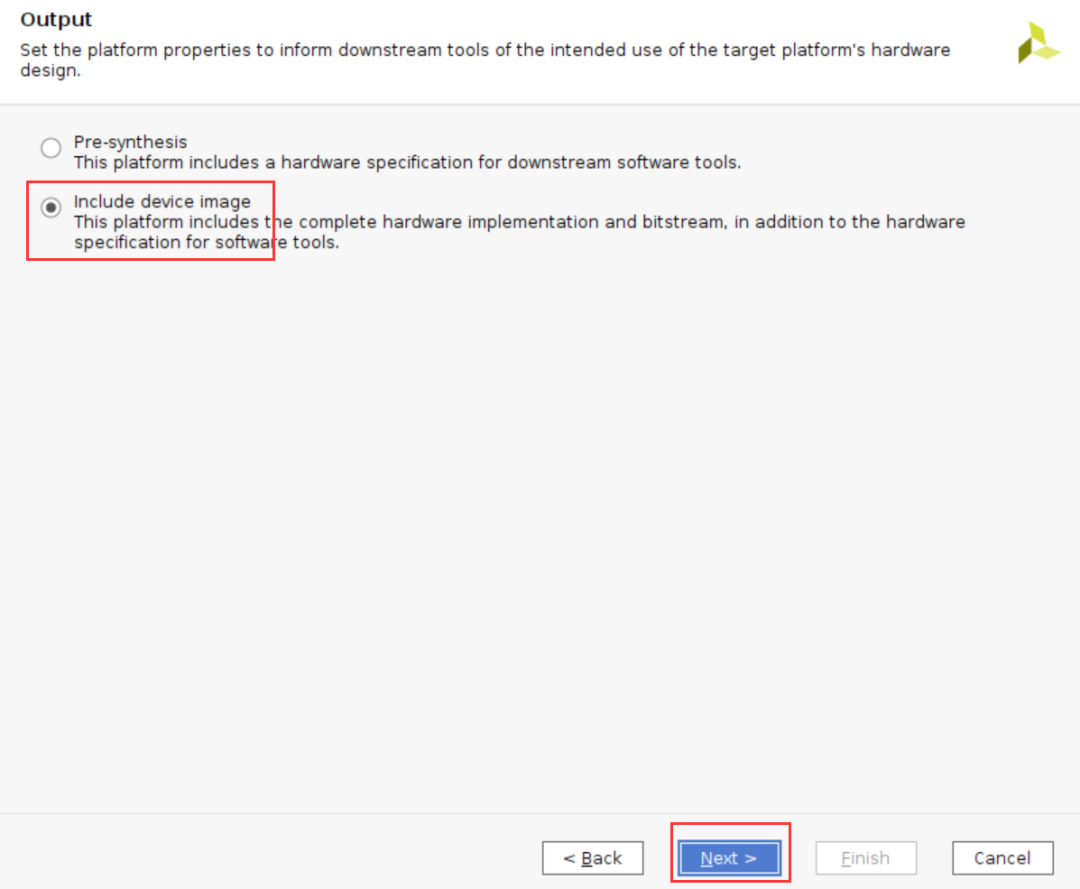

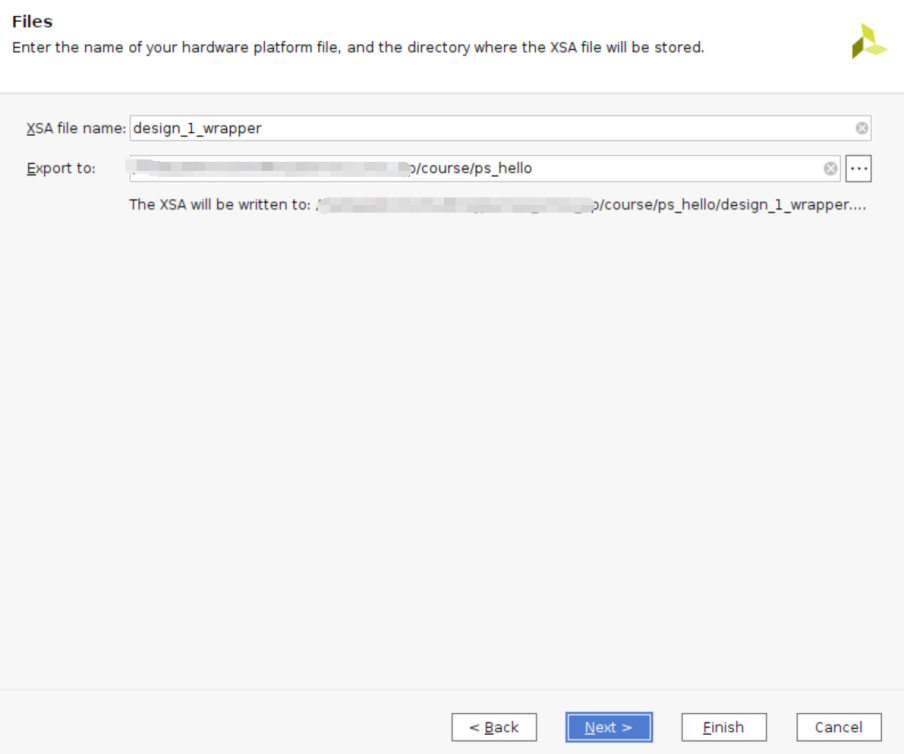

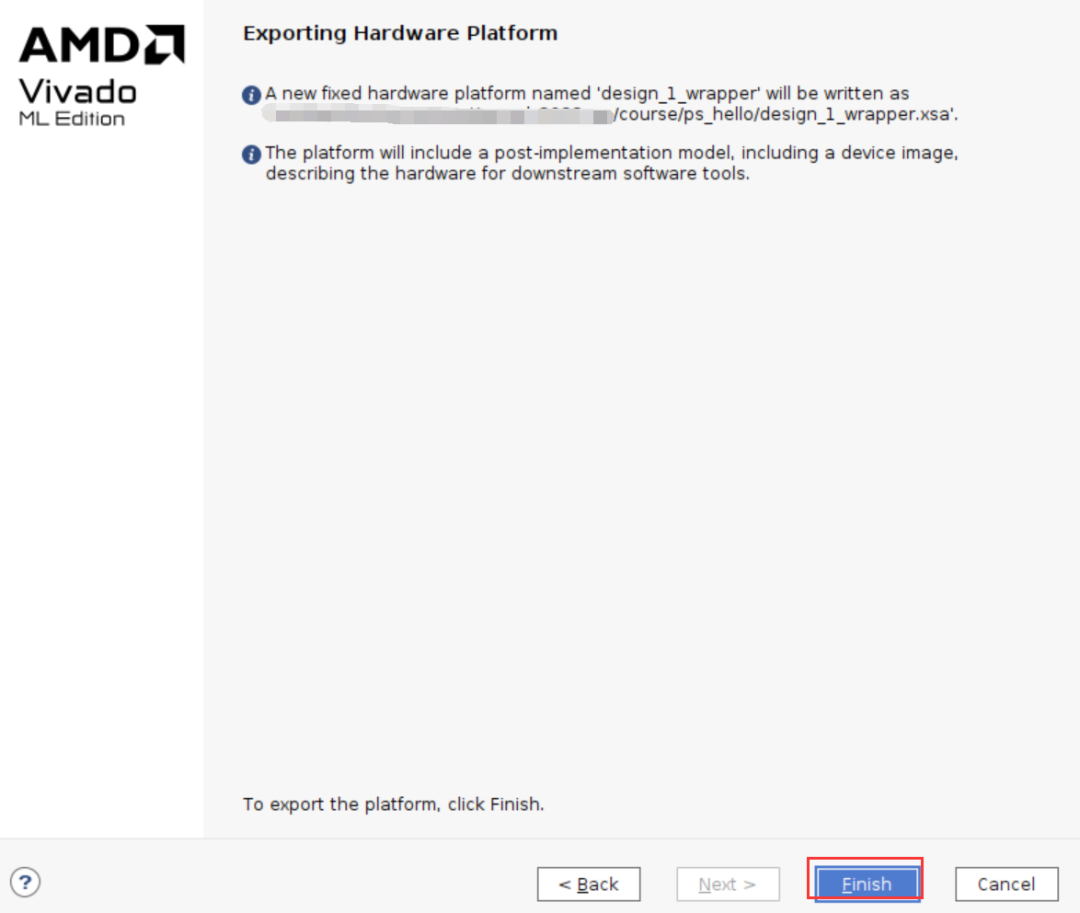

23)File->Export->Export Hardware...

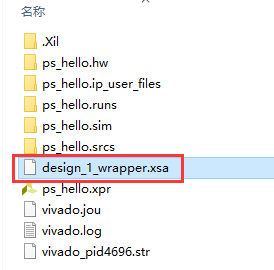

此時在工程目錄下可以看到xsa文件,這個文件就包含了Vivado硬件設(shè)計(jì)的信息,可交由軟件開發(fā)人員使用。

到此為止,F(xiàn)PGA工程師工作告一段落。

軟件工程師工作內(nèi)容

Vitis工程目錄為“ps_hello/vitis”

以下為軟件工程師負(fù)責(zé)內(nèi)容。

1.3 Vitis調(diào)試

1.3.1 創(chuàng)建Application工程

1)新建一個文件夾,將vivado導(dǎo)出的xx.xsa文件拷貝進(jìn)來。

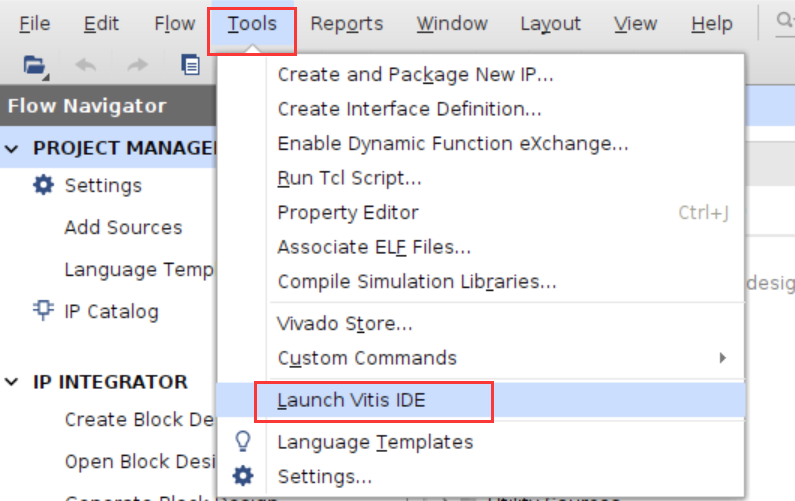

2)Vitis是獨(dú)立的軟件,可以雙擊Vitis軟件打開,也可以通過在Vivado軟件中選擇ToolsàLaunch Vitis打開Vitis軟件

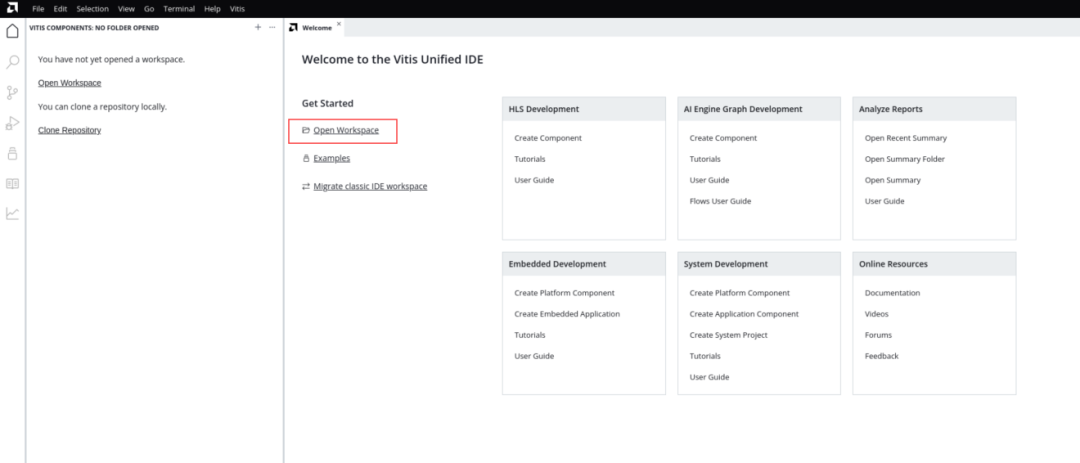

在歡迎界面,點(diǎn)擊Open Workspace,選擇之前新建的文件夾,點(diǎn)擊”O(jiān)K”

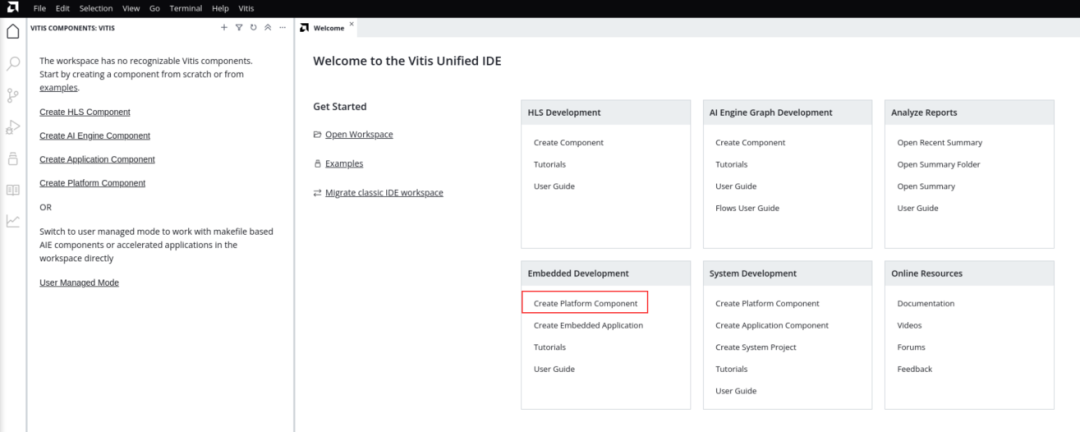

3)啟動Vitis之后界面如下,點(diǎn)擊“Create Platform Component”,這個選項(xiàng)會創(chuàng)建Platfrom工程,Platform工程類似于以前版本的hardware platform,包含了硬件支持的相關(guān)文件以及BSP。

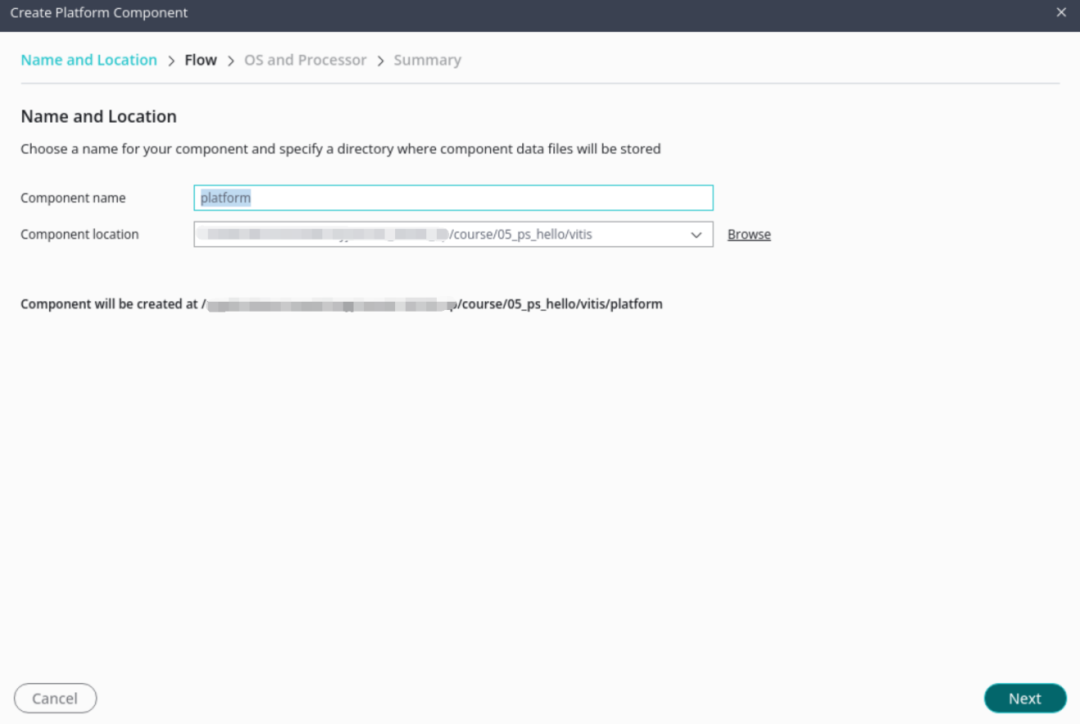

4)第一頁填寫Component name和路徑,保持默認(rèn),點(diǎn)擊Next

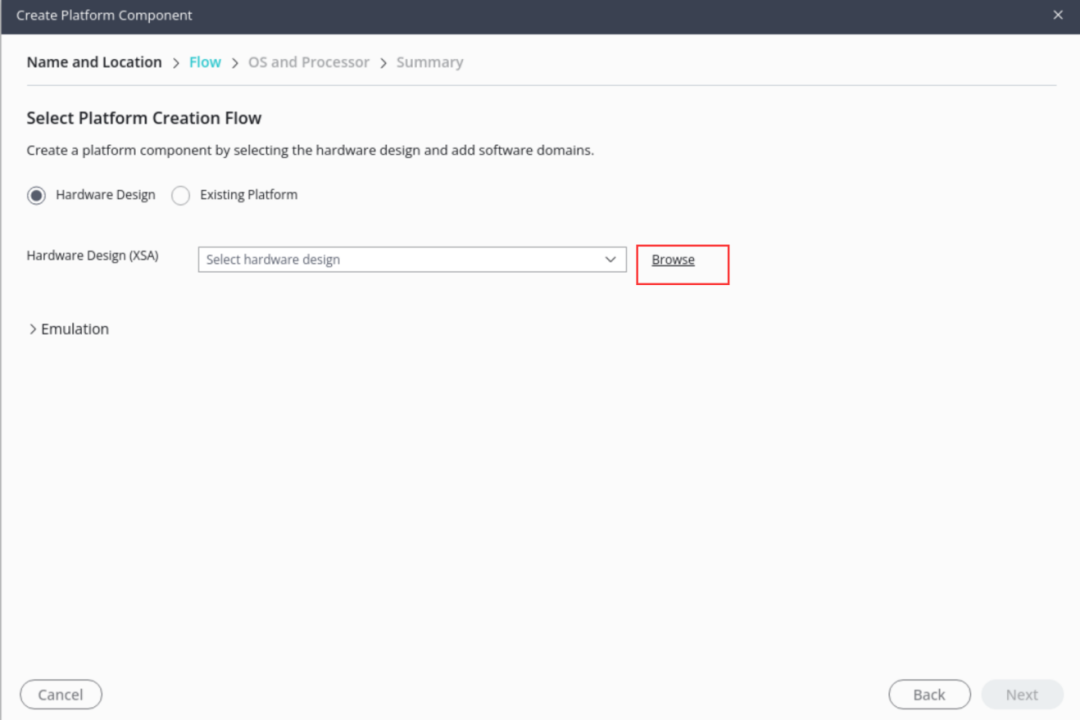

5)選擇(XSA,選擇“Browse”,選擇之前生成的xsa,點(diǎn)擊打開,之后點(diǎn)擊Next

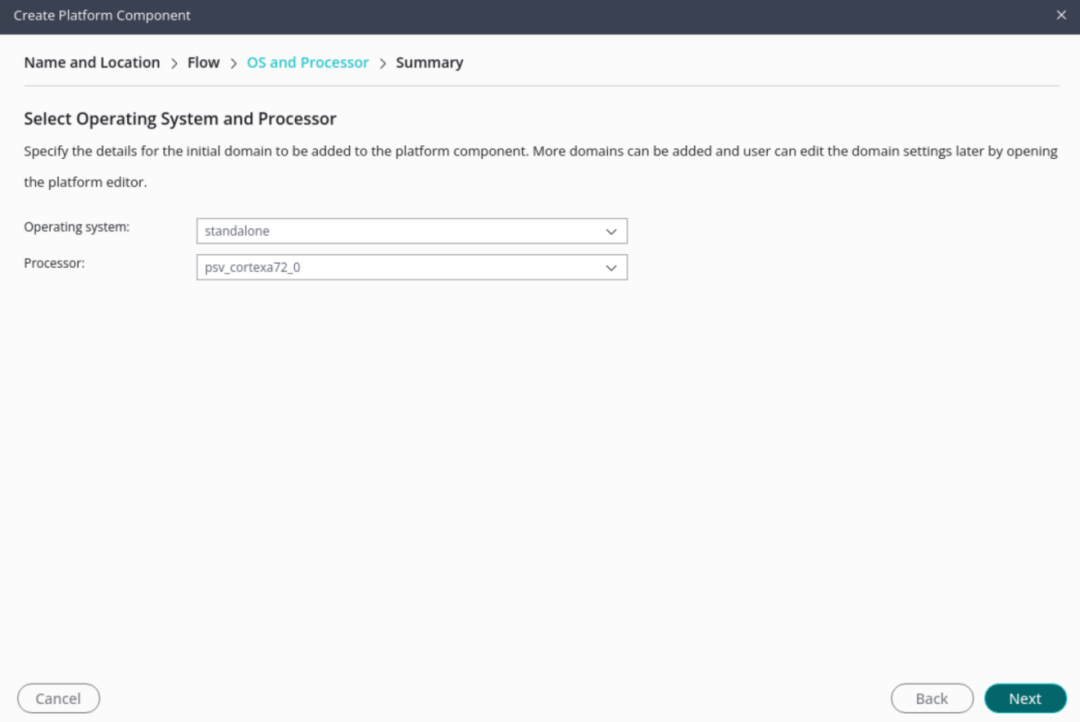

6)選擇操作系統(tǒng)和處理器,這里保持默認(rèn)

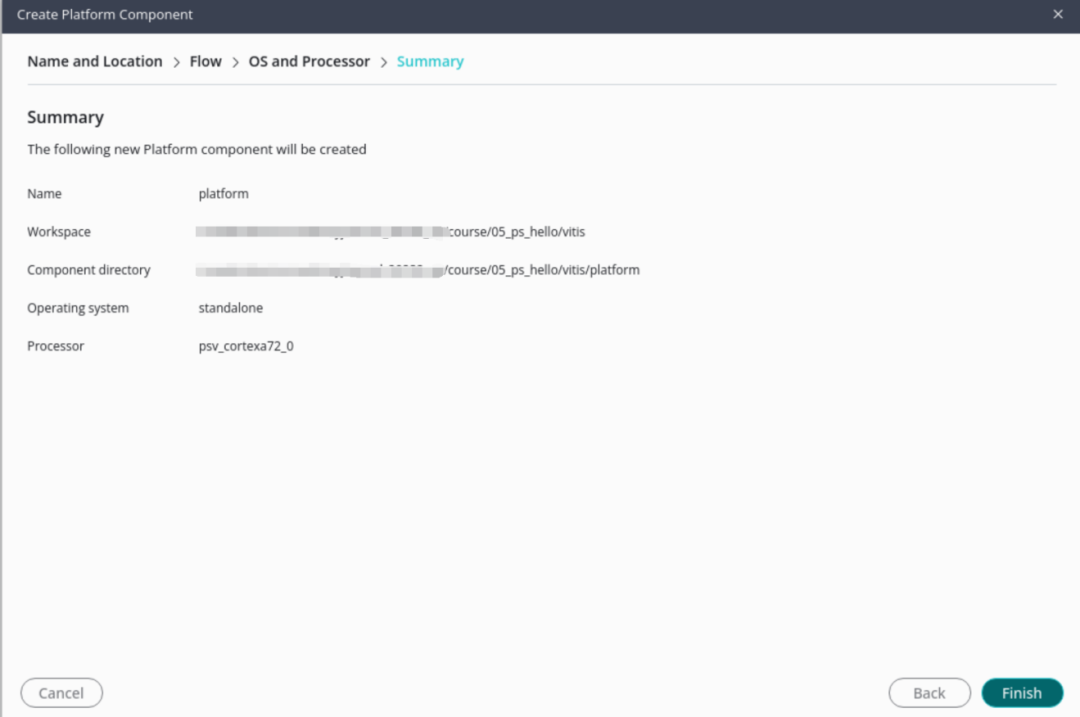

7)點(diǎn)擊Finish完成

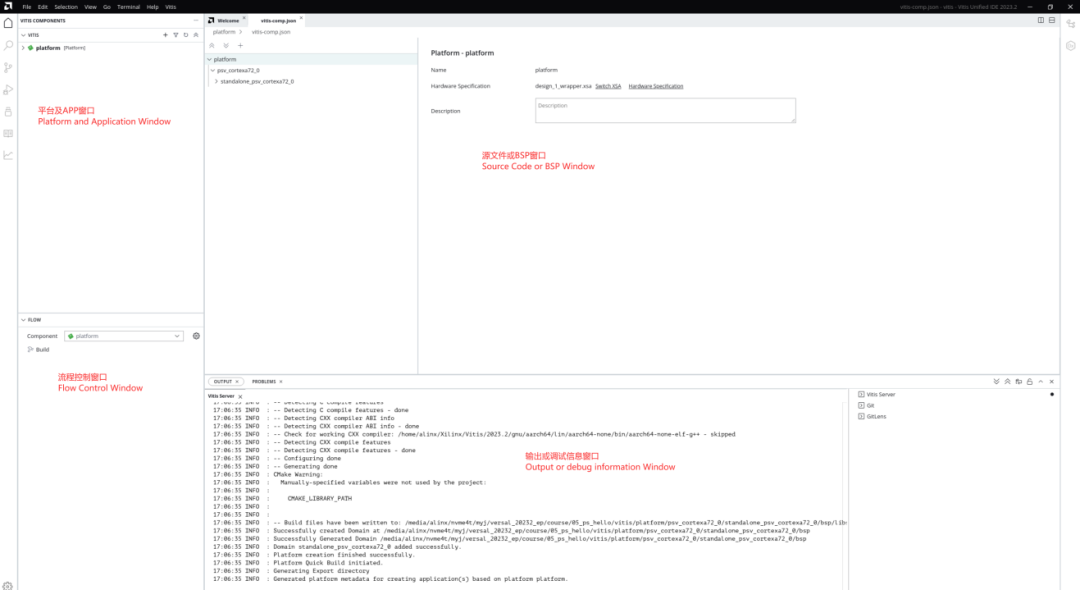

8)生成之后出現(xiàn)窗口界面,以下是一些窗口介紹,與之前版本的Vitis界面有相似之處,但差別也比較大。

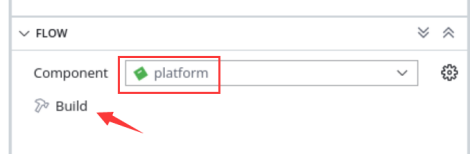

9)可以在Flow窗口編譯平臺

沒有錯誤狀態(tài)

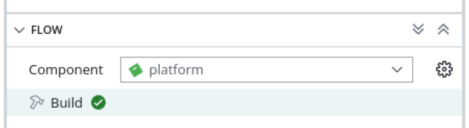

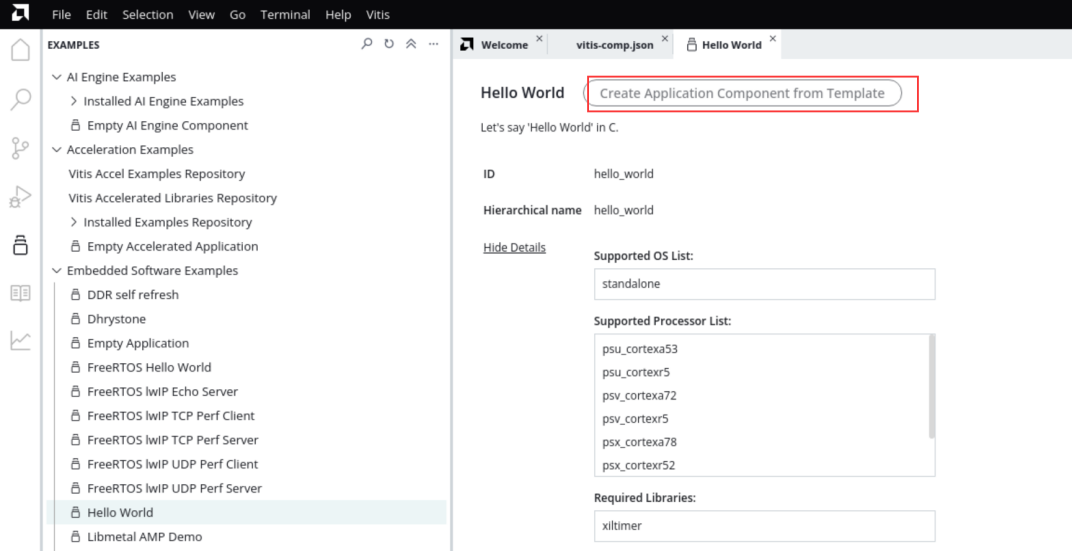

10)點(diǎn)擊左側(cè)Example,這里面有很多官方的例程,與以前版本也比較類似,選擇Hello World

11)點(diǎn)擊創(chuàng)建工程

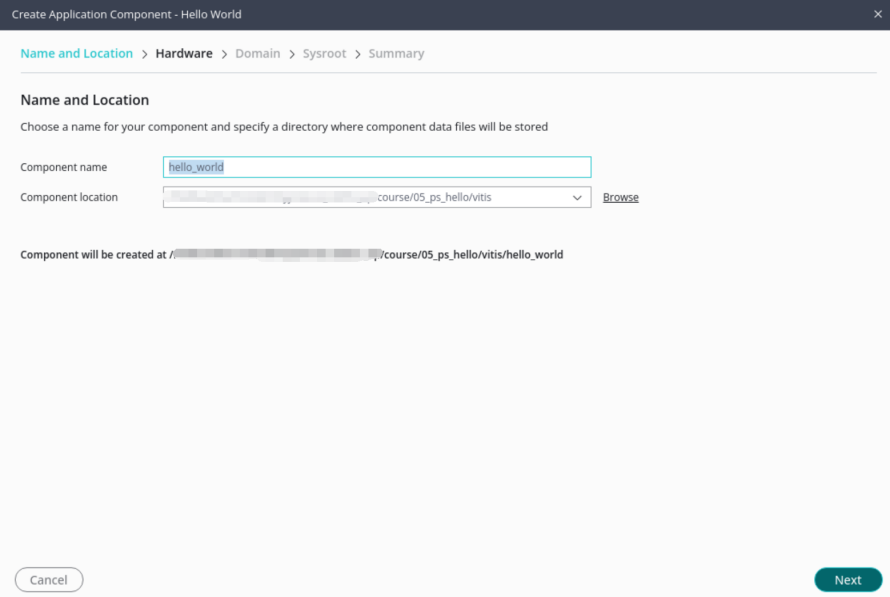

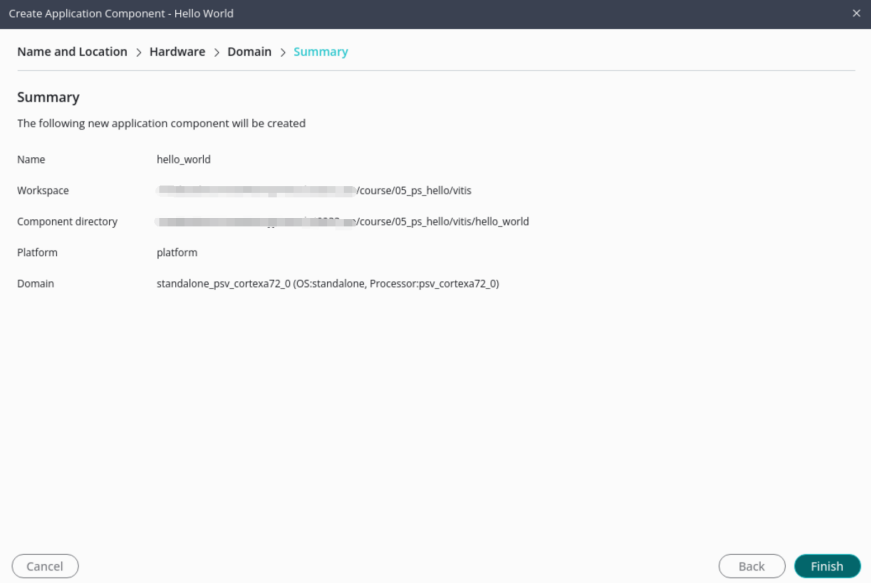

12)填寫工程名稱和路徑,保持默認(rèn)

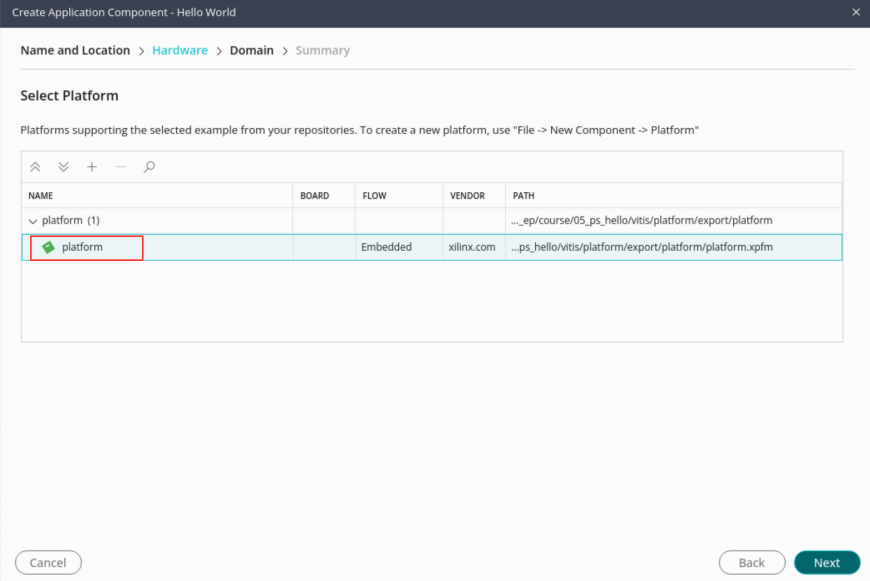

13)選中平臺

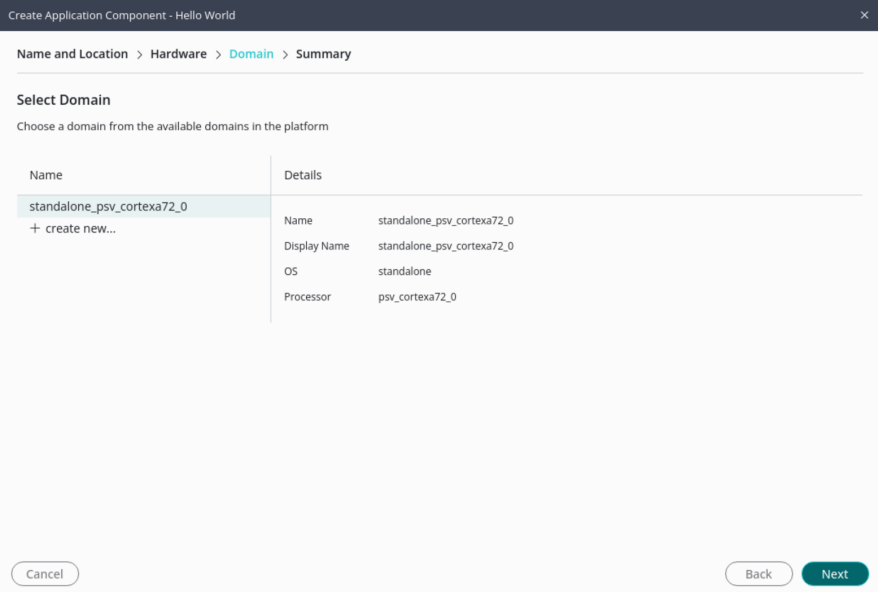

14)點(diǎn)擊Next

15)完成

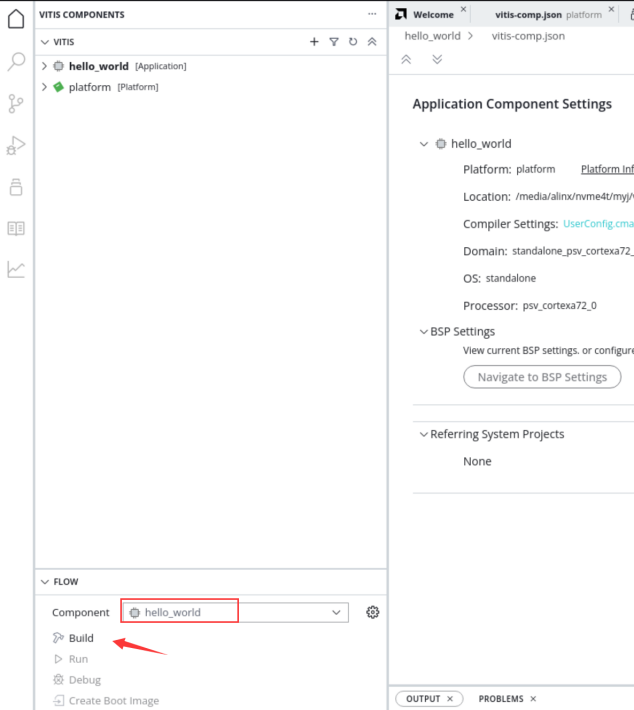

16)選中hello_world,點(diǎn)擊Build

1.3.2 下載調(diào)試

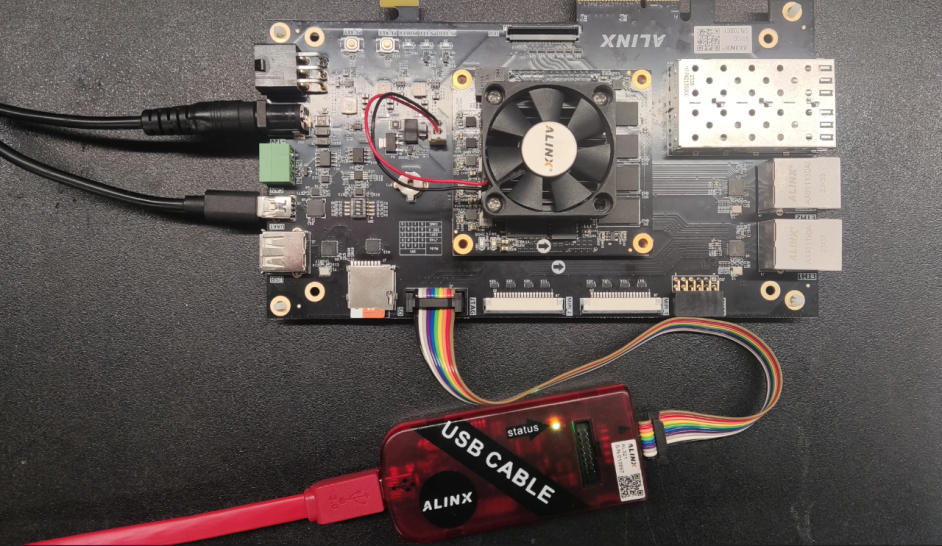

1)連接JTAG線到開發(fā)板、UART的USB線到PC

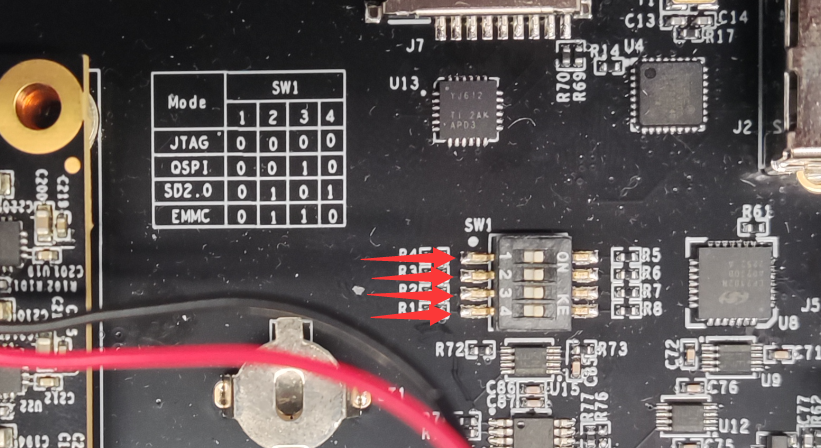

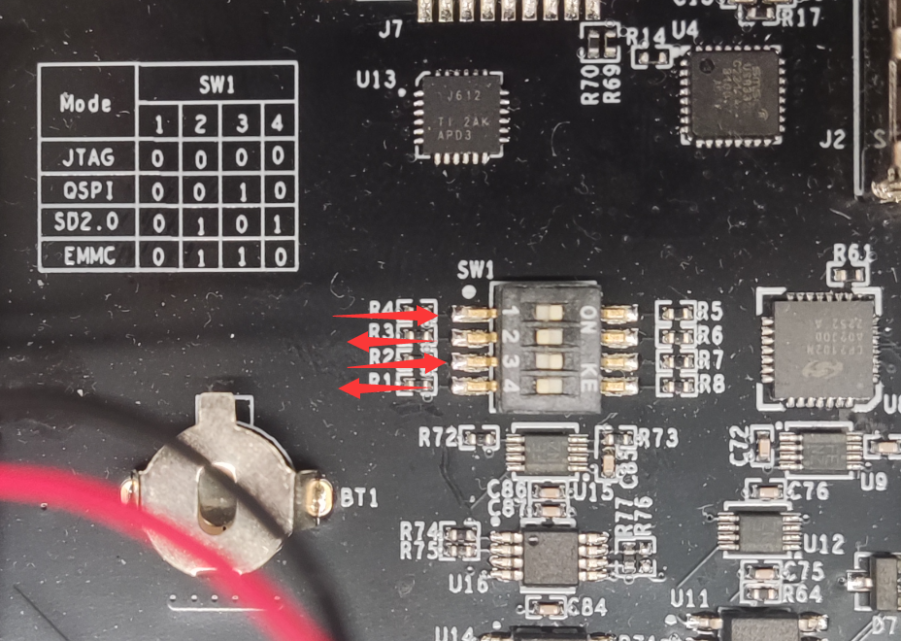

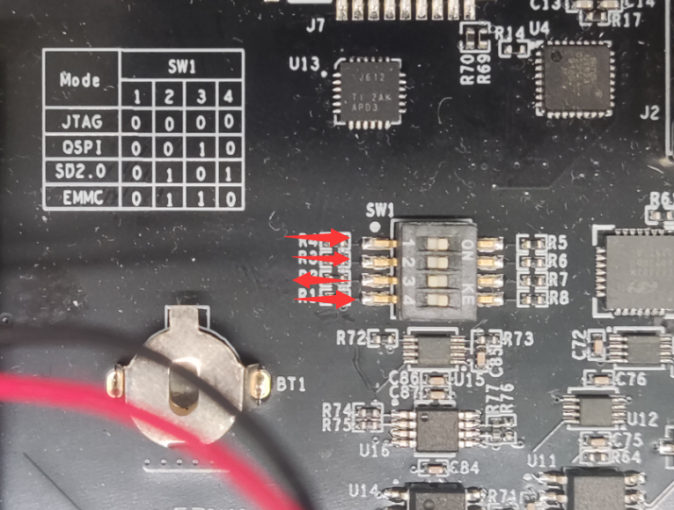

2)在上電之前最好將開發(fā)板的啟動模式設(shè)置到JTAG模式,拔到”O(jiān)N”的位置

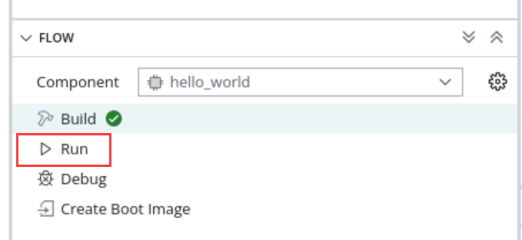

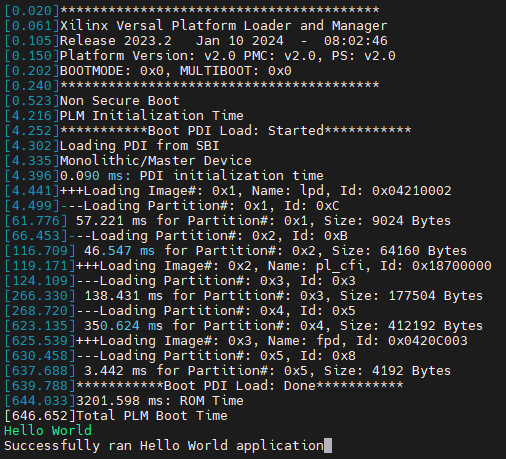

3)開發(fā)板上電,并且打開串口調(diào)試工具,點(diǎn)擊Flow中的Run

4)這個時候觀察串口調(diào)試工具,即可以看到輸出”Hello World”

1.4 固化程序

普通的FPGA一般是可以從flash啟動,或者被動加載,在第一章的PMC架構(gòu)中已經(jīng)介紹啟動過程,這里不再介紹。

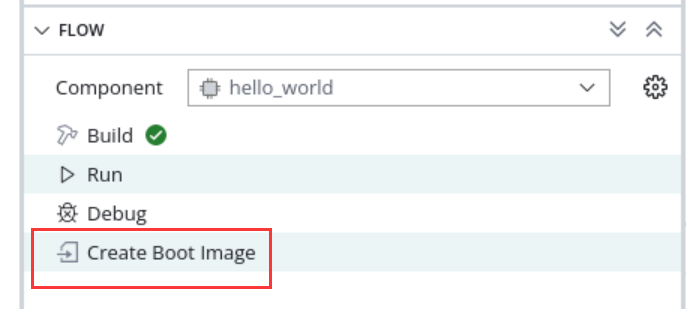

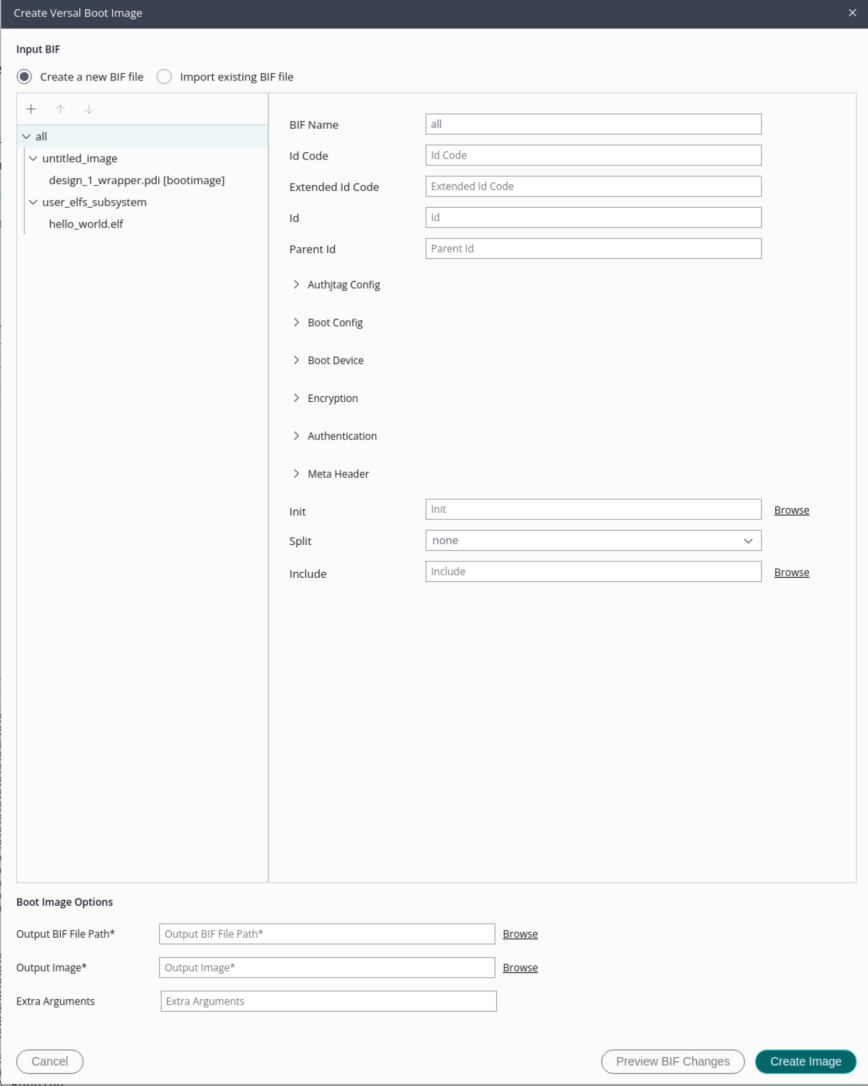

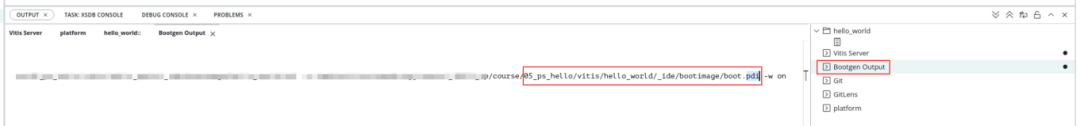

在Flow中選擇Creat Boot Image,彈出的窗口中可以看到生成的BIF文件路徑,BIF文件是生成BOOT文件的配置文件,還有生成的Output Image文件路徑,也就是生成BOOT.pdi文件,它是我們需要的啟動文件,可以放到SD卡啟動,也可以燒寫到QSPI Flash。

在生成的目錄下可以找到boot.pdi文件

1.4.1 SD卡啟動測試

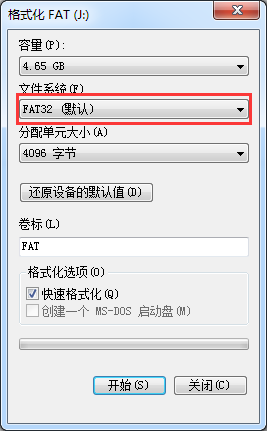

1)格式化SD卡,只能格式化為FAT32格式,其他格式無法啟動

? ? ? ? ?

? ? ? ? ?

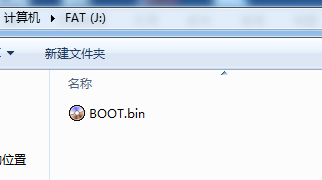

2)放入boot.pdi文件,放在根目錄

3)SD卡插入開發(fā)板的SD卡插槽

4)啟動模式調(diào)整為SD卡啟動

? ?

? ?

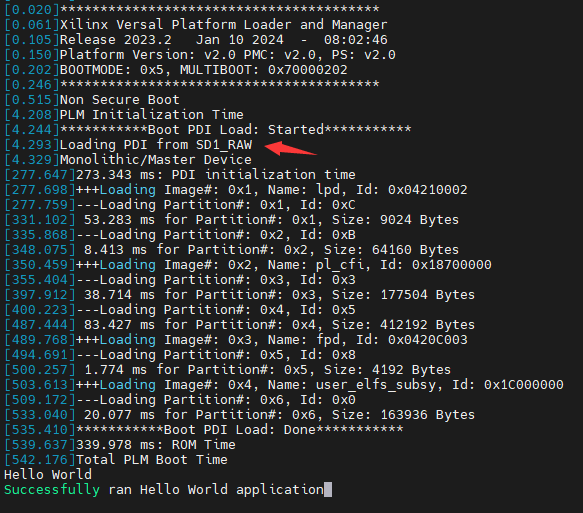

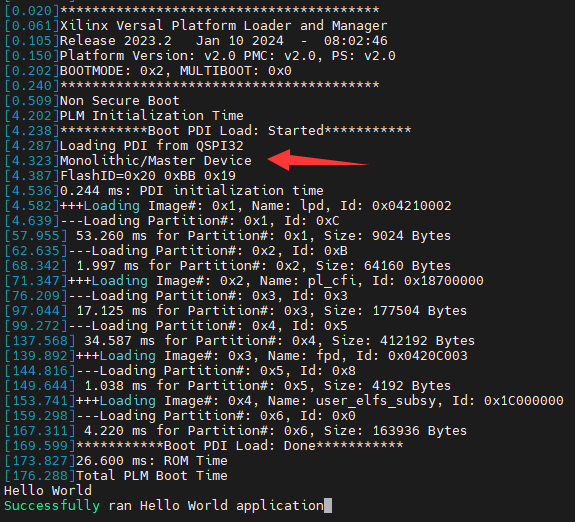

5)打開串口軟件,上電啟動,即可看到打印信息,紅色框?yàn)镕SBL啟動信息,黃色箭頭部分為執(zhí)行的應(yīng)用程序helloworld

1.4.2 QSPI啟動測試

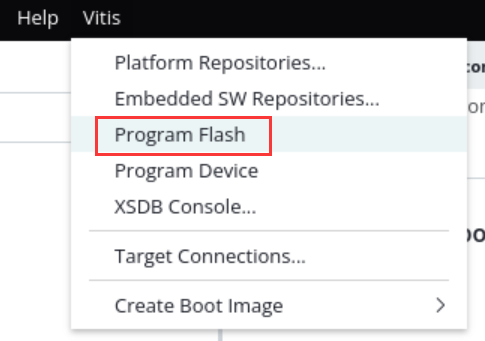

1)在Vitis菜單Vitis -> Program Flash

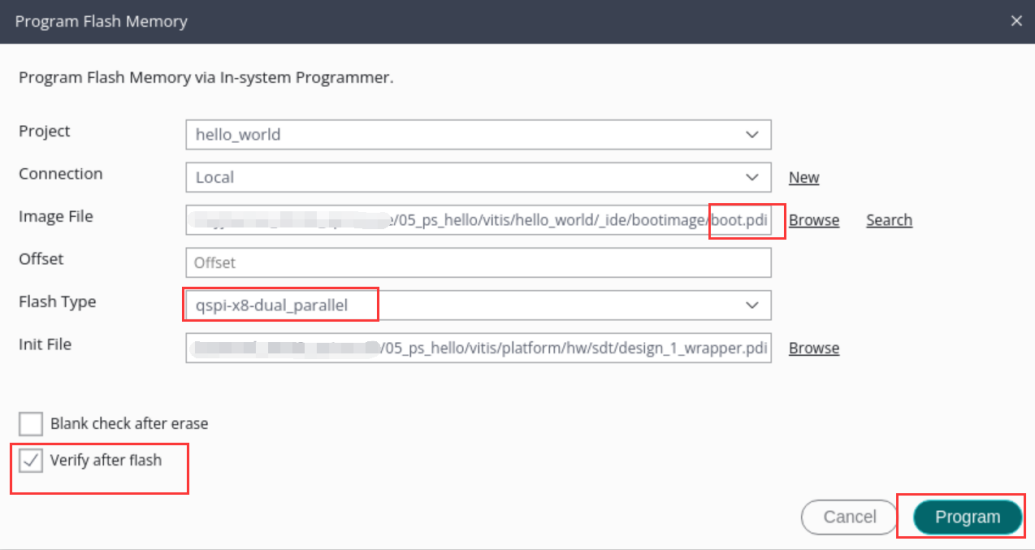

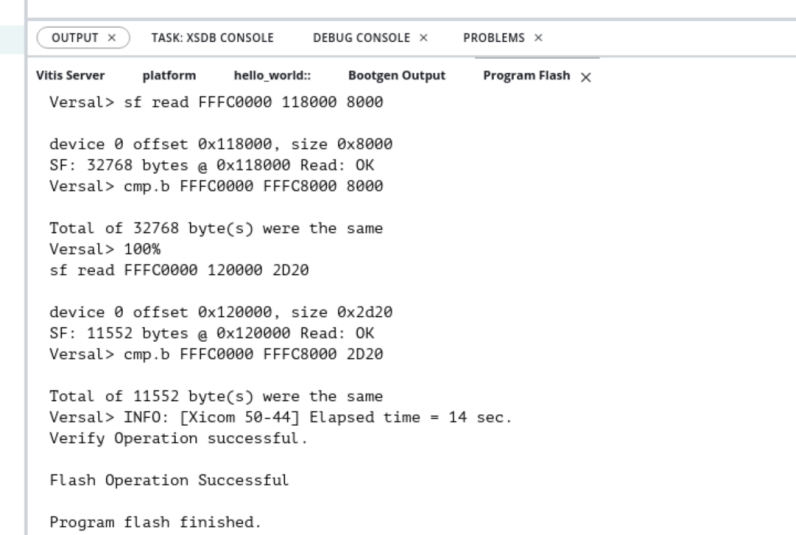

2)Image FIle文件選擇要燒寫的boot.pdi。選擇Verify after flash,F(xiàn)lash Type選擇qspi-x8-dual_parallel,在燒寫完成后校驗(yàn)flash。

3)點(diǎn)擊Program等待燒寫完成

4)設(shè)置啟動模式為QSPI,再次啟動,可以在串口軟件里看到與SD同樣的啟動效果。

1.5 本章小結(jié)

本章從FPGA工程師和軟件工程師兩者角度出發(fā),介紹了Versal開發(fā)的經(jīng)典流程,F(xiàn)PGA工程師的主要工作是搭建好硬件平臺,提供硬件描述文件xsa給軟件工程師,軟件工程師在此基礎(chǔ)上開發(fā)應(yīng)用程序。本章是一個簡單的例子介紹了FPGA和軟件工程師協(xié)同工作,后續(xù)還會牽涉到PS與PL之間的聯(lián)合調(diào)試,較為復(fù)雜,也是Versal開發(fā)的核心部分。

同時也介紹了FSBL,啟動文件的制作,SD卡啟動方式,QSPI下載及啟動方式。

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

19865瀏覽量

234434 -

led燈

+關(guān)注

關(guān)注

22文章

1596瀏覽量

109560 -

DDR4

+關(guān)注

關(guān)注

12文章

332瀏覽量

41678 -

串口調(diào)試

+關(guān)注

關(guān)注

2文章

270瀏覽量

25113 -

QSPI

+關(guān)注

關(guān)注

0文章

45瀏覽量

12673

原文標(biāo)題:【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺之體驗(yàn)ARM,裸機(jī)輸出(7)

文章出處:【微信號:ALINX,微信公眾號:ALINX】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺之Versal介紹(2)

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺之準(zhǔn)備工作(1)

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺之 Versal 介紹(2)

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺PL LED實(shí)驗(yàn)(3)

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺之PL LED實(shí)驗(yàn)(3)

自適應(yīng)計(jì)算加速平臺 功能超CPU和FPGA

Xilinx推出Versal:業(yè)界首款自適應(yīng)計(jì)算加速平臺,支持快速創(chuàng)新

賽靈思發(fā)布自適應(yīng)計(jì)算加速平臺芯片系列Versal

賽靈思Versal自適應(yīng)計(jì)算加速平臺助于高效實(shí)現(xiàn)設(shè)計(jì)目標(biāo)

賽靈思Versal自適應(yīng)計(jì)算加速平臺指南

Versal:首款自適應(yīng)計(jì)算加速平臺(ACAP)

AMD發(fā)布第二代Versal自適應(yīng)SoC,AI嵌入式領(lǐng)域再提速

ALINX受邀參加AMD自適應(yīng)計(jì)算峰會

面向AI與機(jī)器學(xué)習(xí)應(yīng)用的開發(fā)平臺 AMD/Xilinx Versal? AI Edge VEK280

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺之體驗(yàn)ARM,裸機(jī)輸出(7)

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺之體驗(yàn)ARM,裸機(jī)輸出(7)

評論