隨著AI、大數據、云計算等技術在各行各業(yè)廣泛應用,相應的設計結構和設計內容也變得日益復雜。目前的應用開發(fā)速度已無法滿足企業(yè)的需求,如何簡化設計進程,提高應用開發(fā)效率成為當下亟需解決的問題?賽靈思 Versal 自適應計算加速平臺的設計方法論是幫助精簡 Versal 器件設計進程的一整套最佳實踐,遵循這些步驟和最佳實踐進行操作,將有助于以最快且最高效的方式實現期望的設計目標。

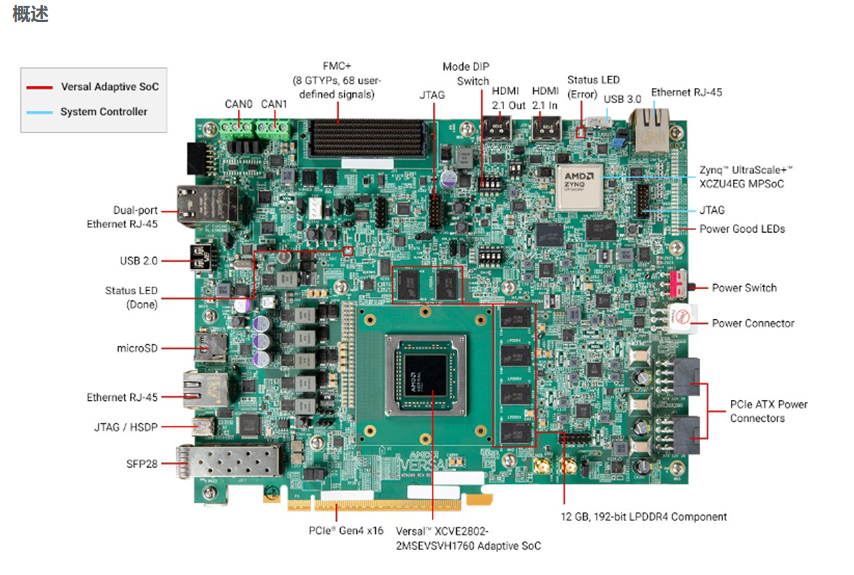

Versal ACAP 屬于異構計算平臺,具有多個計算引擎。在 Versal ACAP 上可映射各種應用,包括對無線系統(tǒng)、機器學習推斷和視頻處理算法進行信號處理。除了多個計算引擎外,Versal ACAP 還可使用高速串行 I/O、片上網絡 (NoC)、 DDR4/LPDDR4 存儲器控制器和多重速率以太網介質訪問控制器 (MRMAC) 來提供超高系統(tǒng)帶寬。Versal 器件分類為 Versal Prime 系列、Premium 系列和 AI Core 系列。

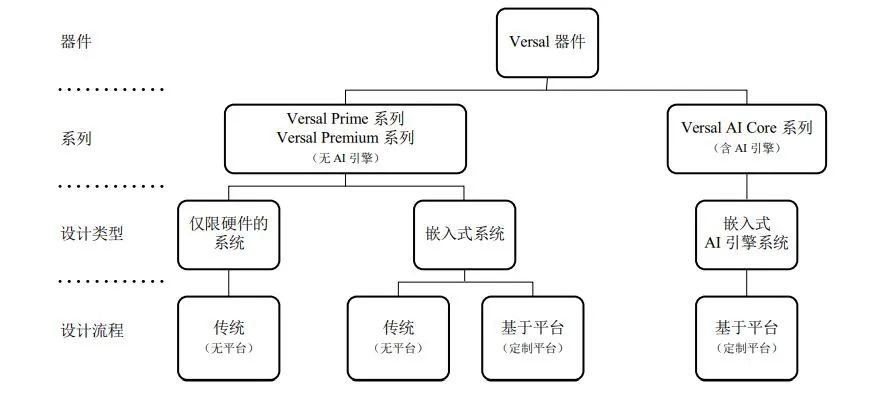

下圖顯示了每種 Versal 器件系列所支持的不同系統(tǒng)設計類型和設計流程。

圖:系統(tǒng)設計類型

適用所有系統(tǒng)的設計流程

系統(tǒng)設計方法論要求基于目標應用明確所有系統(tǒng)要求。其中包括識別具有正確特性(例如,DDRMC IP 數量、AI 引擎 等)的相應 Versal 器件。您還必須考量功耗和發(fā)熱要求。選擇相應的器件后,下一步即可著手系統(tǒng)設計,包括在器件上進行目標應用的軟硬件協(xié)同設計、系統(tǒng)驗證以及初始化和調試。

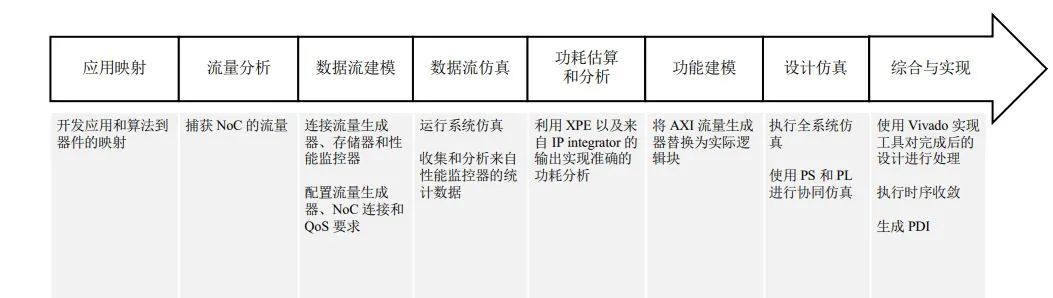

為確保充分利用 Versal ACAP 中可用的多種多樣的計算元件,并使用最高效的實現流程,賽靈思建議采用下圖所示的系統(tǒng)設計方法論流程,此流程適用于所有系統(tǒng)設計類型。

圖:系統(tǒng)設計方法流程

系統(tǒng)設計時的考慮因素

合理可行的設計流程解決方案需要將各種關鍵變量考慮在內,在僅限硬件的系統(tǒng)設計中,關鍵注意事項之一設計中的數據流。通常這些設計都具有下列組件:

? 多個高速 I/O 接口

? 內部數據緩沖和存儲,具有由片上 RAM 和外部 DDR 存儲器組成的存儲器層級

? 內部數據處理邏輯

對于能夠處理外部和內部流量帶寬和時延要求的設計,為其創(chuàng)建 DDRMC-NoC 配置至關重要。賽靈思建議先執(zhí)行流量分析以評估并最終明確流量,然后再繼續(xù)執(zhí)行設計的整體集成和實現階段。除此以外,報告中還涵蓋了嵌入式系統(tǒng)設計值得考量的特殊注意事項,根據隨附的是嵌入式系統(tǒng)還是服務器系統(tǒng),每個步驟所面臨的難題也不盡相同。

原文標題:用戶指南 | Versal ACAP:精簡設計進程的最佳實踐

文章出處:【微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

Versal

+關注

關注

1文章

169瀏覽量

8078 -

ACAP

+關注

關注

1文章

54瀏覽量

8397

原文標題:用戶指南 | Versal ACAP:精簡設計進程的最佳實踐

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

利用AMD VERSAL自適應SoC的設計基線策略

Versal 600G DCMAC Subsystem LogiCORE IP產品指南

適用于Versal的AMD Vivado 加快FPGA開發(fā)完成Versal自適應SoC設計

第二代AMD Versal Premium系列SoC滿足各種CXL應用需求

面向AI與機器學習應用的開發(fā)平臺 AMD/Xilinx Versal? AI Edge VEK280

AMD Versal自適應SoC器件Advanced Flow概覽(下)

AMD Versal自適應SoC器件Advanced Flow概覽(上)

AMD Versal自適應SoC DDRMC如何使用Micron仿真模型進行仿真

賽靈思低溫失效的原因,有沒有別的方法或者一些見解?

使用 AMD Versal AI 引擎釋放 DSP 計算的潛力

AMD推出第二代Versal Premium系列

AMD Alveo V80計算加速器網絡研討會

AMD Versal自適應SoC CPM5 QDMA的Tandem PCIe啟動流程介紹

第二代AMD Versal Prime系列自適應SoC的亮點

賽靈思Versal自適應計算加速平臺助于高效實現設計目標

賽靈思Versal自適應計算加速平臺助于高效實現設計目標

評論