摘 要

Quartus開發(fā)軟件已添加到開發(fā)者云中,為領(lǐng)先的FPGA軟件提供云訪問能力。這一創(chuàng)新使得FPGA開發(fā)人員和合作伙伴能夠使用最新技術(shù)進行解決方案評估和開發(fā),讓他們能夠便捷地獲得領(lǐng)先性能,這凸顯了對用戶體驗的重視與不懈追求。

本白皮書將討論云托管環(huán)境的優(yōu)勢,以及用戶應(yīng)該采用開發(fā)者云的合理理由。這個領(lǐng)先的云平臺為FPGA設(shè)計師提供了Quartus開發(fā)軟件,用于在開發(fā)下一代FPGA設(shè)計時評估最新的技術(shù)。通過使用開發(fā)者云,F(xiàn)PGA設(shè)計人員將可以搶先體驗新功能并及早獲得最新支持硬件的報告,從而縮短產(chǎn)品的上市時間,并充分發(fā)揮自身創(chuàng)意。

克服創(chuàng)新滯后障礙

在技術(shù)快速進步的推動下,F(xiàn)PGA設(shè)計人員面臨著管理復(fù)雜設(shè)計環(huán)境,同時保持設(shè)計領(lǐng)先的雙重挑戰(zhàn)。基于云的開發(fā)對于解決這些問題十分重要,可以讓這些設(shè)計人員及早獲取最新軟件和器件,在競爭日益激烈且不斷變化的環(huán)境中開展創(chuàng)新并交付高質(zhì)量應(yīng)用。

軟件發(fā)布周期的挑戰(zhàn)

FPGA開發(fā)人員設(shè)計復(fù)雜的FPGA可能難度很大,特別是當設(shè)計軟件尚未推出他們所需的功能、器件的時候。這種延遲導致了創(chuàng)新滯后,F(xiàn)PGA開發(fā)人員無法將他們的想法和創(chuàng)意變?yōu)楝F(xiàn)實,因為他們必須等待下一個版本,然后才能在現(xiàn)有設(shè)計中利用最新技術(shù),或者延遲決定未來使用什么技術(shù)。所有這些延遲都會影響上市時間。

創(chuàng)新滯后可能會影響設(shè)計的性能、效率和整體能力,因為設(shè)計人員可能需要手動實施某些復(fù)雜方案,而這些方案在未來版本的軟件中已簡化或自動化,無法盡快獲取這些功能可能導致時間浪費和錯誤風險增加。在快速發(fā)展的技術(shù)行業(yè)中,上市時間至關(guān)重要。由于軟件版本而造成設(shè)計延遲可能會導致錯失機會和收入損失。能夠使用最新功能的競爭對手可能會更快地推出產(chǎn)品,從而獲得顯著優(yōu)勢。

為了解決創(chuàng)新滯后和上市時間的問題,開發(fā)人員需要搶先使用軟件功能和硬件設(shè)備。

在軟件整體發(fā)布之前,新的功能可以提前幾個月通過線上的方式提供。FPGA開發(fā)人員可以使用最新發(fā)布的軟件繼續(xù)在本地開發(fā)大部分應(yīng)用。盡早獲取領(lǐng)先器件的在線功能和分析報告,可以讓FPGA開發(fā)人員探索最新的概念并突破設(shè)計限制。如果無法盡早獲取,設(shè)計師可能不得不在創(chuàng)意上有所妥協(xié)。

基于云的環(huán)境能夠讓他們及早獲取領(lǐng)先技術(shù),并獲得搶先體驗合作關(guān)系等途徑,從而克服等待下一個軟件版本所帶來的挑戰(zhàn)。這些策略可以幫助設(shè)計人員采用最先進的技術(shù),提高設(shè)計質(zhì)量并在市場中保持競爭優(yōu)勢。

基于云的優(yōu)勢

基于云的環(huán)境為FPGA開發(fā)提供了靈活性、全局可訪問性、更高的安全性,并可以降低PFGA開發(fā)成本。這種環(huán)境可以使軟件擺脫物理硬件限制的束縛,允許全局訪問,投資于安全性,降低前期費用,并為前沿應(yīng)用和算法提供可擴展性。由于可以使用云數(shù)據(jù)中心的多個CPU或更大內(nèi)存,這些應(yīng)用和算法可能會發(fā)揮更大優(yōu)勢。

云托管軟件的優(yōu)勢

1、靈活性

云托管功能將軟件從物理硬件的約束中解放出來,幫助靈活滿足不同的實施需求。

2、全球可訪問性

地理位置不再是獲取領(lǐng)先軟件的障礙。云部署允許用戶通過互聯(lián)網(wǎng)連接從任何地方訪問其應(yīng)用,打破界限,實現(xiàn)全球范圍內(nèi)的協(xié)作。

3、降低開發(fā)成本

傳統(tǒng)的FPGA開發(fā)需要大量的設(shè)計和開發(fā)費用,并需要購買現(xiàn)場硬件來確認性能。基于云的評估可以減少這些前期費用,允許您使用最新的軟件和硬件來快速確認您的開發(fā)目標能否實現(xiàn),并可以讓您的團隊專注于創(chuàng)新和增長,從而節(jié)省資金。

4、靈活性與可擴展性

云環(huán)境允許您快速為虛擬機配置所需的軟件。此外,您可以根據(jù)項目需求輕松增加或縮減云資源,確保您在需要時擁有適當?shù)挠嬎隳芰ΑT诮鉀Q方案在線驗證之前,您可以減輕本地IT部門的負擔。

開發(fā)者云將Quartus開發(fā)軟件的強大功能與敏捷的云技術(shù)相結(jié)合,提供了一款顛覆性的解決方案。通過允許用戶利用軟件的功能并及早獲取新功能,開發(fā)者云打開了無與倫比的創(chuàng)新之門。

使用最新的軟件功能進行開發(fā)

在當今快速變化的技術(shù)環(huán)境中,創(chuàng)新是成功背后的驅(qū)動力,擁有合適的工具至關(guān)重要。

開發(fā)者云平臺是面向FPGA開發(fā)人員的一站式解決方案,旨在為他們提供最新的FPGA軟件和IP庫。除了Quartus開發(fā)軟件外,開發(fā)者云平臺還包括完整的IP庫和FPGA開發(fā)環(huán)境,為FPGA設(shè)計提供了全流程的支撐。

Quartus開發(fā)軟件:及早獲取最新算法

Quartus開發(fā)軟件是FPGA開發(fā)軟件,它對于任何FPGA設(shè)計人員來說都是不可或缺的解決方案。這個全面的工具集簡化了從啟動到實施的設(shè)計過程,確保您高效實現(xiàn)自己的FPGA設(shè)計。

效率:Quartus開發(fā)軟件提供豐富的高級功能和庫,優(yōu)化了從設(shè)計捕獲到時序分析、驗證和路由的設(shè)計過程。這可以加快開發(fā)速度,減少設(shè)計迭代,并最終縮短上市時間。

高級算法:該軟件結(jié)合了先進的算法,提高了設(shè)計效率和性能,幫助實現(xiàn)更強大的FPGA設(shè)計。

每個版本的Quartus開發(fā)軟件都增加了改進、新功能和特性,可以幫助您提高設(shè)計效率和性能。使用尚未發(fā)布的軟件功能可以對FPGA開發(fā)特性產(chǎn)生積極影響。

通過在開發(fā)者云環(huán)境中使用Quartus開發(fā)軟件,F(xiàn)PGA開發(fā)人員能夠使用最新的軟件功能創(chuàng)建、開發(fā)和驗證他們的設(shè)計,同時確保出色的精度和效率。

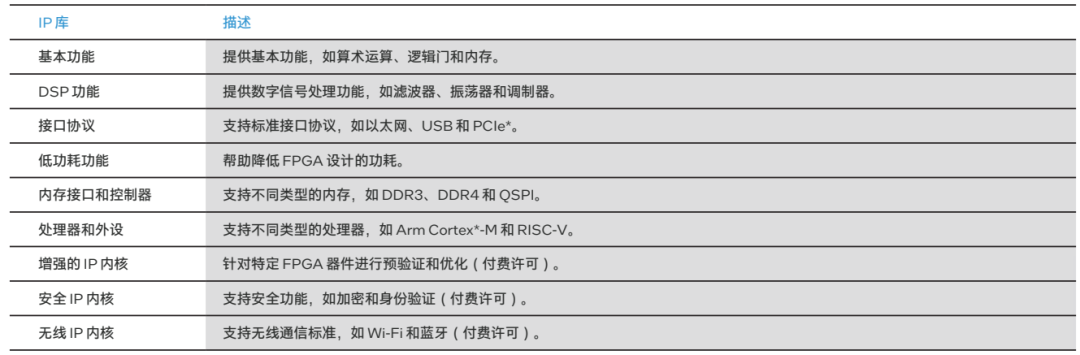

完全許可的IP庫助力探索無限可能

Quartus開發(fā)軟件的一個顯著優(yōu)勢在于其豐富的IP核庫。這些預(yù)先設(shè)計的功能塊可為您的項目提供堅實的基礎(chǔ),節(jié)省時間和精力,同時確保可靠性。IP庫涵蓋廣泛的功能,包括內(nèi)存控制器、接口、處理器等,如下表1所示。

表1. 開發(fā)者云環(huán)境中提供的預(yù)裝IP內(nèi)核

對于剛剛開始FPGA設(shè)計的用戶來說,免費庫是一個很好的選擇,而付費庫則為要求苛刻的應(yīng)用提供更專業(yè)的功能。云環(huán)境允許您使用付費許可,并獲得相關(guān)設(shè)計影響的報告。從開發(fā)者云環(huán)境下載的IP只包括付費IP的實例化,您可以使用本地付費許可在本地復(fù)制結(jié)果。

通過開發(fā)者云平臺,您可以使用最新、最先進和優(yōu)化的IP來滿足您的設(shè)計需求。

無安裝的完整設(shè)計環(huán)境

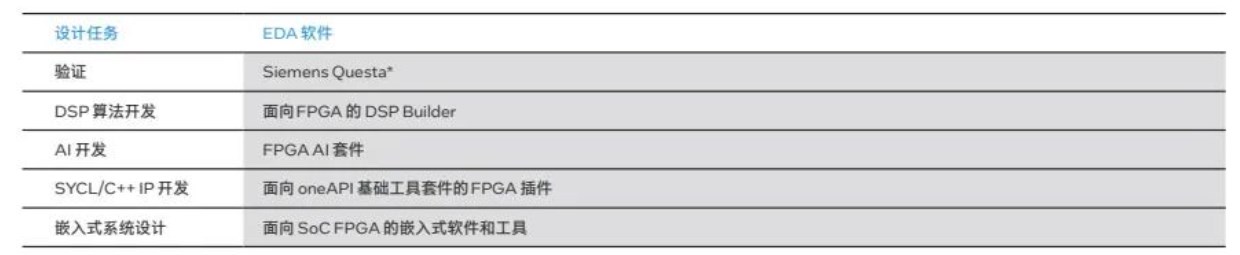

Quartus開發(fā)軟件及其IP庫提供了一個先進的FPGA開發(fā)環(huán)境。然而,開發(fā)人員通常需要使用額外的軟件工具,以優(yōu)化成本和性能。

開發(fā)者云通過支持現(xiàn)有的方法提供了額外的優(yōu)勢。一旦進入開發(fā)者云平臺,用戶就可以使用完成FPGA開發(fā)任務(wù)所需的所有許可工具,例如驗證、設(shè)計集成和高級IP創(chuàng)建等任務(wù)。

下面的表2重點介紹了典型的開發(fā)者云環(huán)境中提供的軟件工具,開發(fā)人員無需安裝軟件、匹配工具版本或確認正確安裝。

表2. 開發(fā)者云環(huán)境中預(yù)裝的軟件

預(yù)裝工具可確保開發(fā)者云為FPGA開發(fā)人員提供其在本地FPGA開發(fā)中使用的相同軟件和環(huán)境,使他們能夠?qū)W⒂诓⒗眯碌南冗M功能,提高性能、效率和可靠性。

在您自己的環(huán)境中開發(fā)

開發(fā)者云中提供的FPGA設(shè)計環(huán)境適用于幾種常見的操作系統(tǒng),包括Windows*和最常見的Linux*變體,允許設(shè)計團隊在熟悉的本地環(huán)境中執(zhí)行所有典型任務(wù)。

虛擬機(VM)預(yù)先配置了開發(fā)FPGA所需的工具和IP,使FPGA開發(fā)人員能夠立即開始開發(fā)硬件模型,執(zhí)行模擬程序,運行實驗,并在各種硬件配置和器件上測試代碼,包括發(fā)布軟件中可能沒有的搶先體驗器件。

正如下面的方法所強調(diào)的,設(shè)置和配置云資源比獲取物理硬件更快。這可以幫助您在不同條件下更快地測試和驗證應(yīng)用的行為。

開發(fā)者云FPGA方法:

1. 通過安全的文件傳輸途徑上傳設(shè)計數(shù)據(jù)

2. 選擇Windows或Linux變體虛擬機。

3. 啟動Quartus開發(fā)軟件及其他預(yù)裝的許可軟件和IP。

4. 選擇一個FPGA器件。

5. 開發(fā)、優(yōu)化并驗證應(yīng)用。

6. 查看報告和性能指標。

7. (可選)返回第4步,選擇另一個器件。

8. 通過安全的文件傳輸途徑下載優(yōu)化的結(jié)果。

在生產(chǎn)環(huán)境中部署解決方案之前,開發(fā)者云平臺可以用來確認您的期望,也可以作為一種學習工具來熟悉最新的硬件和軟件技術(shù)。

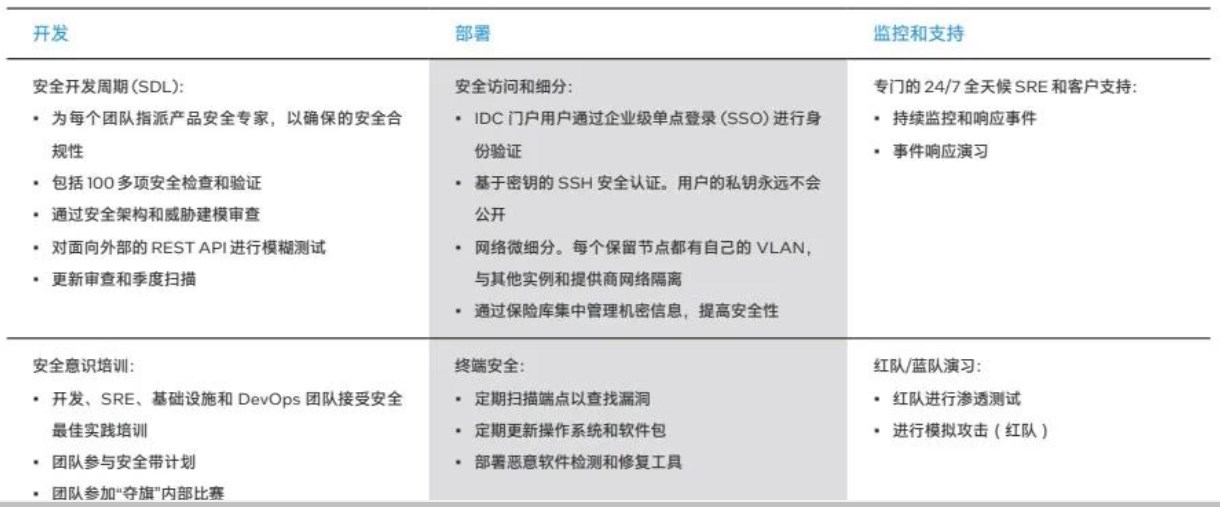

憑借行業(yè)領(lǐng)先的安全性,高枕無憂地進行設(shè)計

在使用任何云環(huán)境時,都必須考慮安全性。

所有上傳到開發(fā)者云平臺的數(shù)據(jù)都是您的數(shù)據(jù);它不會與任何人共享,并在安全云環(huán)境中受到保護。從云環(huán)境中刪除數(shù)據(jù)時,數(shù)據(jù)會被刪除,刪除后不會保留任何用戶數(shù)據(jù)。

開發(fā)者云平臺的架構(gòu)在設(shè)計之初就考慮到了數(shù)據(jù)安全性問題,并遵循安全開發(fā)周期(SDL)流程,該流程已集成到云產(chǎn)品開發(fā)生命周期中。SDL確保在每個產(chǎn)品開發(fā)階段都考慮到安全性。

安全團隊一直在執(zhí)行廣泛的威脅建模,以識別關(guān)鍵資產(chǎn)、攻擊面、威脅,并提供化解措施。

一支由長期安全專業(yè)人員組成的跨學科團隊負責審查云架構(gòu)和威脅建模。

在開發(fā)者云平臺的主要發(fā)布點啟動服務(wù)之前,會隨機執(zhí)行主動滲透測試或道德黑客攻擊。

在每個開發(fā)和使用階段都要考慮和處理安全問題。

已在運營的一個持續(xù)監(jiān)控和運營安全事件響應(yīng)中心,由產(chǎn)品安全事件響應(yīng)團隊(PSIRT)和行業(yè)安全研究提供支持,并要求員工接受強制性的安全培訓和資源,以幫助培養(yǎng)安全第一的思維模式,并確保安全融入運營的各個方面。

結(jié)論:塑造FPGA設(shè)計的未來

盡早獲得新功能和硬件將帶來顯著的競爭優(yōu)勢。

開發(fā)者云平臺為FPGA設(shè)計人員提供了一個絕佳機會,幫助他們徹底改變工作流程,簡化協(xié)作并擁抱創(chuàng)新。通過將Quartus開發(fā)軟件與云技術(shù)無縫集成,開發(fā)者云平臺可幫助設(shè)計人員快速創(chuàng)作,高效協(xié)作并克服現(xiàn)代FPGA設(shè)計的挑戰(zhàn)。

使用基于云的環(huán)境的主要優(yōu)勢如下:

無需本地硬件投資,降低技術(shù)評估期間的前期成本。

只為使用的資源付費,優(yōu)化預(yù)算分配。

避免硬件限制,無論項目復(fù)雜程度如何,都確保出色性能。

促進設(shè)計團隊之間的無縫協(xié)作,無論其位于何處。

總之,開發(fā)者云平臺結(jié)合了Quartus開發(fā)軟件的強大功能、最新的硬件以及靈活的云技術(shù),為開發(fā)人員及早提供新功能和最佳實踐示例,提供了變革性的體驗,是推動FPGA設(shè)計創(chuàng)新和效率的關(guān)鍵平臺。

開發(fā)者云助您擁抱設(shè)計的未來,實現(xiàn)無限可能。

相關(guān)技術(shù)可能需要支持的硬件、特定軟件或服務(wù)激活。

沒有任何產(chǎn)品或組件是絕對安全的。

您的成本和結(jié)果可能會有所不同。

性能因使用、配置和其他因素而異。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1645文章

22021瀏覽量

617230 -

虛擬機

+關(guān)注

關(guān)注

1文章

966瀏覽量

29266

原文標題:助力搶先體驗:利用Quartus? 開發(fā)軟件進行基于云的開發(fā)

文章出處:【微信號:英特爾FPGA,微信公眾號:英特爾FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

EP1C6Q240老產(chǎn)品維護求低版本QUARTUS

【高云GW5AT-LV60 開發(fā)套件試用體驗】開箱及IDE與開發(fā)板基礎(chǔ)功能測評

STM32開發(fā)板教程之STM32開發(fā)指南免費下載

基于瑞薩RA0E1開發(fā)板的IIC OLED測試

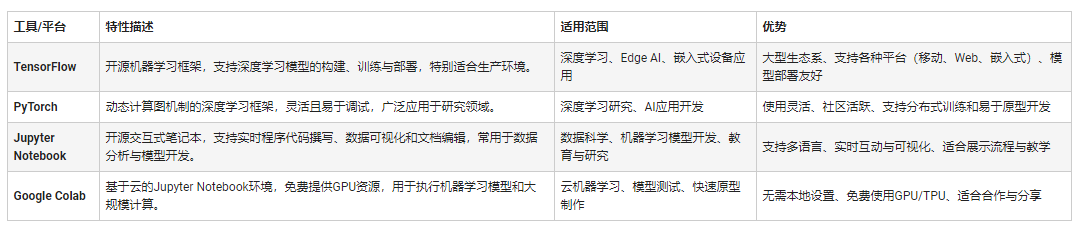

嵌入式機器學習的應(yīng)用特性與軟件開發(fā)環(huán)境

華為云軟件開發(fā)生產(chǎn)線(CodeArts)10 月新功能特性

恩智浦eIQ AI和機器學習開發(fā)軟件增加兩款新工具

TAS5721沒有DEMO板能開發(fā)軟件嗎?

使用MATLAB、Simulink和Polyspace加速軟件定義汽車開發(fā)

恒訊科技分析:使用顯卡云服務(wù)器進行游戲開發(fā)有哪些優(yōu)勢和劣勢?

用于開發(fā)HS2247PT射頻發(fā)射通用程序的智能軟件

利用Quartus開發(fā)軟件進行基于云的開發(fā),及早獲取最新算法

利用Quartus開發(fā)軟件進行基于云的開發(fā),及早獲取最新算法

評論