一.TTL

TTL集成電路的主要型式為晶體管-晶體管邏輯門(transistor-transistor logic gate),TTL大部分都采用5V電源.

1.輸出高電平Uoh和輸出低電平UolUoh≥2.4V,Uol≤0.4V

2.輸入高電平和輸入低電平Uih≥2.0V,Uil≤0.8V二.CMOS

CMOS電路是電壓控制器件,輸入電阻極大,對(duì)于干擾信號(hào)十分敏感,因此不用的輸入端不應(yīng)開(kāi)路,接到地或者電源上.CMOS電路的優(yōu)點(diǎn)是噪聲容限較寬,靜態(tài)功耗很小.

1.輸出高電平Uoh和輸出低電平UolUoh≈VCC,Uol≈GND

2.輸入高電平Uoh和輸入低電平UolUih≥0.7VCC,Uil≤0.2VCC (VCC為電源電壓,GND為地)

從上面可以看出:

在 同樣5V電源電壓情況下,COMS電路可以直接驅(qū)動(dòng)TTL,因?yàn)镃MOS的輸出高電平大于2.0V,輸出低電平小于0.8V;而TTL電路則不能直接驅(qū)動(dòng) CMOS電路,TTL的輸出高電平為大于2.4V,如果落在2.4V~3.5V之間,則CMOS電路就不能檢測(cè)到高電平,低電平小于0.4V滿足要求,所 以在TTL電路驅(qū)動(dòng)COMS電路時(shí)需要加上拉電阻.如果出現(xiàn)不同電壓電源的情況,也可以通過(guò)上面的方法進(jìn)行判斷.

如果電路中出現(xiàn)3.3V的COMS電路去驅(qū)動(dòng)5V CMOS電路的情況,如3.3V單片機(jī)去驅(qū)動(dòng)74HC,這種情況有以下幾種方法解決,最簡(jiǎn)單的就是直接將74HC換成74HCT(74系列的輸入輸出在下面有介紹)的芯片,因?yàn)?.3V CMOS 可以直接驅(qū)動(dòng)5V的TTL電路;或者加電壓轉(zhuǎn)換芯片;還有就是把單片機(jī)的I/O口設(shè)為開(kāi)漏,然后加上拉電阻到5V,這種情況下得根據(jù)實(shí)際情況調(diào)整電阻的大小,以保證信號(hào)的上升沿時(shí)間.三.74系列簡(jiǎn)介

74系列可以說(shuō)是我們平時(shí)接觸的最多的芯片,74系列中分為很多種,而我們平時(shí)用得最多的應(yīng)該是以下幾種:74LS,74HC,74HCT這三種,這三種系列在電平方面的區(qū)別如下:

TTL和CMOS電平

1、TTL電平(什么是TTL電平):

輸出高電平>2.4V,輸出低電平=2.0V,輸入低電平 Vih,輸入低電平 Vih > Vt > Vil > Vol

6:Ioh:邏輯門輸出為高電平時(shí)的負(fù)載電流(為拉電流).7:Iol:邏輯門輸出為低電平時(shí)的負(fù)載電流(為灌電流).8:Iih:邏輯門輸入為高電平時(shí)的電流(為灌電流).9:Iil:邏輯門輸入為低電平時(shí)的電流(為拉電流).

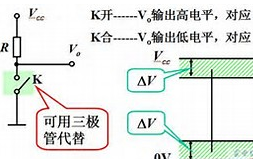

門電路輸出極在集成單元內(nèi)不接負(fù)載電阻而直接引出作為輸出端,這種形式的門稱為開(kāi)路門.開(kāi)路的TTL、CMOS、ECL門分別稱為集電極開(kāi)路(OC)、漏極開(kāi)路(OD)、發(fā)射極開(kāi)路(OE),使用時(shí)應(yīng)審查是否接上拉電阻(OC、OD門)或下拉電阻(OE門),以及電阻阻值是否合適.對(duì)于集電極開(kāi)路(OC)門,其上拉電阻阻值RL應(yīng)滿足下面條件:

(1):RL < (VCC-Voh)/(n*Ioh+m*Iih)(2):RL > (VCC-Vol)/(Iol+m*Iil)

其中n:線與的開(kāi)路門數(shù);m:被驅(qū)動(dòng)的輸入端數(shù).

10:常用的邏輯電平

·邏輯電平:有TTL、CMOS、LVTTL、ECL、PECL、GTL;RS232、RS422、LVDS等.

·其中TTL和CMOS的邏輯電平按典型電壓可分為四類:5V系列(5V TTL和5V CMOS)、3.3V系列,2.5V系列和1.8V系列.

·5V TTL和5V CMOS邏輯電平是通用的邏輯電平.

·3.3V及以下的邏輯電平被稱為低電壓邏輯電平,常用的為L(zhǎng)VTTL電平.

·低電壓的邏輯電平還有2.5V和1.8V兩種.

·ECL/PECL和LVDS是差分輸入輸出.

·RS-422/485和RS-232是串口的接口標(biāo)準(zhǔn),RS-422/485是差分輸入輸出,RS-232是單端輸入輸出.OC門,又稱集電極開(kāi)路(漏極開(kāi)路)與非門門電路,Open Collector(Open Drain).

為什么引入OC門?

實(shí)際使用中,有時(shí)需要兩個(gè)或兩個(gè)以上與非門的輸出端連接在同一條導(dǎo)線上,將這些與非門上的數(shù)據(jù)(狀態(tài)電平)用同一條導(dǎo)線輸送出去.因此,需要一種新的與非門電路--OC門來(lái)實(shí)現(xiàn)“線與邏輯”.OC門主要用于3個(gè)方面:

1、實(shí)現(xiàn)與或非邏輯,用做電平轉(zhuǎn)換,用做驅(qū)動(dòng)器.由于OC門電路的輸出管的集電極懸空,使用時(shí)需外接一個(gè)上拉電阻 Rp到電源VCC.OC門使用上拉電阻以輸出高電平,此外為了加大輸出引腳的驅(qū)動(dòng)能力,上拉電阻阻值的選擇原則,從降低功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足 夠大;從確保足夠的驅(qū)動(dòng)電流考慮應(yīng)當(dāng)足夠小.2、線與邏輯,即兩個(gè)輸出端(包括兩個(gè)以上)直接互連就可以實(shí)現(xiàn)“AND”的邏輯功能.在總線傳輸?shù)葘?shí)際應(yīng)用中需要多個(gè)門 的輸出端并聯(lián)連接使用,而一般TTL門輸出端并不能直接并接使用,否則這些門的輸出管之間由于低阻抗形成很大的短路電流(灌電流),而燒壞器件.在硬件 上,可用OC門或三態(tài)門(ST門)來(lái)實(shí)現(xiàn). 用OC門實(shí)現(xiàn)線與,應(yīng)同時(shí)在輸出端口應(yīng)加一個(gè)上拉電阻.3、三態(tài)門(ST門)主要用在應(yīng)用于多個(gè)門輸出共享數(shù)據(jù)總線,為避免多個(gè)門輸出同時(shí)占用數(shù)據(jù)總線,這些門的使能信號(hào) (EN)中只允許有一個(gè)為有效電平(如高電平),由于三態(tài)門的輸出是推拉式的低阻輸出,且不需接上拉(負(fù)載)電阻,所以開(kāi)關(guān)速度比OC門快,常用三態(tài)門作 為輸出緩沖器.什么是OC、OD?

集電極開(kāi)路門(集電極開(kāi)路 OC 或漏極開(kāi)路 OD)

Open-Drain是漏極開(kāi)路輸出的意思,相當(dāng)于集電極開(kāi)路(Open-Collector)輸出,即TTL中的集電極開(kāi)路(OC)輸出.一般用于線或、線與,也有的用于電流驅(qū)動(dòng).

Open-Drain是對(duì)MOS管而言,Open-Collector是對(duì)雙極型管而言,在用法上沒(méi)啥區(qū)別.開(kāi)漏形式的電路有以下幾個(gè)特點(diǎn):

a. 利用外部電路的驅(qū)動(dòng)能力,減少IC內(nèi)部的驅(qū)動(dòng). 或驅(qū)動(dòng)比芯片電源電壓高的負(fù)載.b.可以將多個(gè)開(kāi)漏輸出的Pin,連接到一條線上.通過(guò)一只上拉電阻,在不增加任何器件的情況下,形成“與邏輯”關(guān)系.這也是I2C,SMBus等總線判 斷總線占用狀態(tài)的原理.如果作為圖騰輸出必須接上拉電阻.接容性負(fù)載時(shí),下降延是芯片內(nèi)的晶體管,是有源驅(qū)動(dòng),速度較快;上升延是無(wú)源的外接電阻,速度 慢.如果要求速度高電阻選擇要小,功耗會(huì)大.所以負(fù)載電阻的選擇要兼顧功耗和速度.c. 可以利用改變上拉電源的電壓,改變傳輸電平.例如加上上拉電阻就可以提供TTL/CMOS電平輸出等.d. 開(kāi)漏Pin不連接外部的上拉電阻,則只能輸出低電平.一般來(lái)說(shuō),開(kāi)漏是用來(lái)連接不同電平的器件,匹配電平用的.

正常的CMOS輸出級(jí)是上、下兩個(gè)管子,把上面的管子去掉就是OPEN-DRAIN了.這種輸出的主要目的有兩個(gè):電平轉(zhuǎn)換和線與.

由于漏級(jí)開(kāi)路,所以后級(jí)電路必須接一上拉電阻,上拉電阻的電源電壓就可以決定輸出電平.這樣你就可以進(jìn)行任意電平的轉(zhuǎn)換了.

線與功能主要用于有多個(gè)電路對(duì)同一信號(hào)進(jìn)行拉低操作的場(chǎng)合,如果本電路不想拉低,就輸出高電平,因?yàn)镺PEN-DRAIN上面的管子被拿掉,高電平是靠外接的上拉電阻實(shí)現(xiàn)的.(而正常的CMOS輸出級(jí),如果出現(xiàn)一個(gè)輸出為高另外一個(gè)為低時(shí),等于電源短路.)

OPEN-DRAIN提供了靈活的輸出方式,但是也有其弱點(diǎn),就是帶來(lái)上升沿的延時(shí).因?yàn)樯仙厥峭ㄟ^(guò)外接上拉無(wú)源電阻對(duì)負(fù)載充電,所以當(dāng)電阻選擇小時(shí)延時(shí)就小,但功耗大;反之延時(shí)大功耗小.所以如果對(duì)延時(shí)有要求,則建議用下降沿輸出。

-

CMOS

+關(guān)注

關(guān)注

58文章

6005瀏覽量

238545 -

電源管理

+關(guān)注

關(guān)注

117文章

6425瀏覽量

145968 -

ttl邏輯門

+關(guān)注

關(guān)注

0文章

3瀏覽量

1613

原文標(biāo)題:TTL邏輯門與普通邏輯門混為一談?那你就大錯(cuò)特錯(cuò)了!

文章出處:【微信號(hào):Mouser-Community,微信公眾號(hào):貿(mào)澤電子設(shè)計(jì)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

TTL和CMOS電平,別傻傻分不清

TTL和CMOS電平,別傻傻分不清

評(píng)論