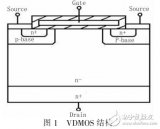

VDMOS(Vertical Double-Diffused Metal Oxide Semiconductor Field Effect Transistor,垂直雙擴散金屬氧化物半導(dǎo)體場效應(yīng)晶體管)器件的厚度對電阻的影響主要體現(xiàn)在以下幾個方面:

一、氧化層厚度對電阻的影響

- 柵氧化層厚度 :

- 影響柵電容 :柵氧化層的厚度直接影響柵電容的大小。較厚的柵氧化層可以減少柵電容,從而提高器件的開關(guān)速度。這是因為柵電容的減少降低了器件在開關(guān)過程中的電荷存儲和釋放時間。

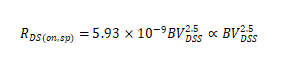

- 影響導(dǎo)通電阻 :然而,增加柵氧化層的厚度也會帶來導(dǎo)通電阻的增加。這是因為柵氧化層是電子從柵極到溝道傳輸?shù)谋亟?jīng)之路,其厚度的增加會增加電子傳輸?shù)淖枇Α?/li>

- 優(yōu)化策略 :為了平衡開關(guān)速度和導(dǎo)通電阻之間的矛盾,通常采用多層外延結(jié)構(gòu)等設(shè)計手段,以在不改變器件反向擊穿電壓的情況下,進一步減少器件電阻。

- 外延層厚度 :

- 影響電流承載能力 :VDMOS器件的外延層厚度直接影響其電流承載能力。較厚的外延層可以提供更大的電流通道,從而降低器件的導(dǎo)通電阻。

- 影響散熱性能 :同時,外延層的厚度也影響器件的散熱性能。較厚的外延層可以提供更好的散熱路徑,有助于降低器件在工作過程中的溫升。

二、其他厚度因素

- 襯底厚度 :雖然襯底厚度對VDMOS器件的電阻直接影響較小,但它對器件的機械穩(wěn)定性和熱穩(wěn)定性有重要影響。較厚的襯底可以提供更好的支撐和散熱效果。

三、綜合影響

- 電阻與性能平衡 :在VDMOS器件的設(shè)計中,需要綜合考慮各種厚度因素對電阻和性能的影響。通過優(yōu)化柵氧化層、外延層等關(guān)鍵層的厚度,可以在保證器件性能的前提下,實現(xiàn)電阻的最小化。

四、實際應(yīng)用中的考慮

- 市場需求 :不同應(yīng)用場景對VDMOS器件的性能要求不同。例如,高頻應(yīng)用需要更快的開關(guān)速度,而大功率應(yīng)用則需要更低的導(dǎo)通電阻。因此,在實際應(yīng)用中,需要根據(jù)具體需求選擇合適的器件厚度。

- 制造工藝 :制造工藝的限制也會影響VDMOS器件的厚度設(shè)計。例如,更薄的柵氧化層需要更先進的制造工藝來保證其質(zhì)量和穩(wěn)定性。

綜上所述,VDMOS器件的厚度對電阻具有顯著影響,需要在設(shè)計過程中綜合考慮各種因素以實現(xiàn)最佳性能。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

電阻

+關(guān)注

關(guān)注

87文章

5619瀏覽量

174869 -

VDMOS器件

+關(guān)注

關(guān)注

0文章

3瀏覽量

7060 -

場效應(yīng)晶體管

+關(guān)注

關(guān)注

6文章

394瀏覽量

20001

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

200V/100A的VDMOS器件開發(fā)

詳細論述了器件制造過程中的關(guān)鍵工藝環(huán)節(jié),包括柵氧化、光刻套準、多晶硅刻蝕、P 阱推進等。流水所得VDMOS 實測結(jié)果表明,該器件反向擊穿特性良好

發(fā)表于 12-02 10:45

?3745次閱讀

VDMOS功率器件用硅外延片

VDMOS功率器件用硅外延片:1973 年美國IR 公司推出VDMOS 結(jié)構(gòu),將器件耐壓、導(dǎo)通電阻和電流處理能力提高到一個新水平。功率

發(fā)表于 12-21 10:52

?41次下載

一種減少VDMOS寄生電容的新結(jié)構(gòu)

一種減少VDMOS寄生電容的新結(jié)構(gòu)

0 引 言 VDMOS與雙極晶體管相比,它的開關(guān)速度快,開關(guān)損耗小,輸入電阻高,驅(qū)動

發(fā)表于 01-11 10:24

?1876次閱讀

用虛擬制造設(shè)計低壓功率VDMOS

隨著高壓器件和功率器件需求的不斷發(fā)展,大功率VDMOS器件的特有作用正日益顯現(xiàn)出來。VDMOS主要應(yīng)用在高電壓和大電流兩種情況,在一些特殊的

發(fā)表于 06-23 16:55

?32次下載

功率VDMOS電機可靠性試驗及失效分析

本文闡述了一種電機用功率 VDMOS 器件的可靠性試驗方案和試驗過程。對不同驅(qū)動電壓下VDMOS器件所能承受的最人供電電壓進行了測試,分別在輕、重負載下對

發(fā)表于 07-22 11:32

?37次下載

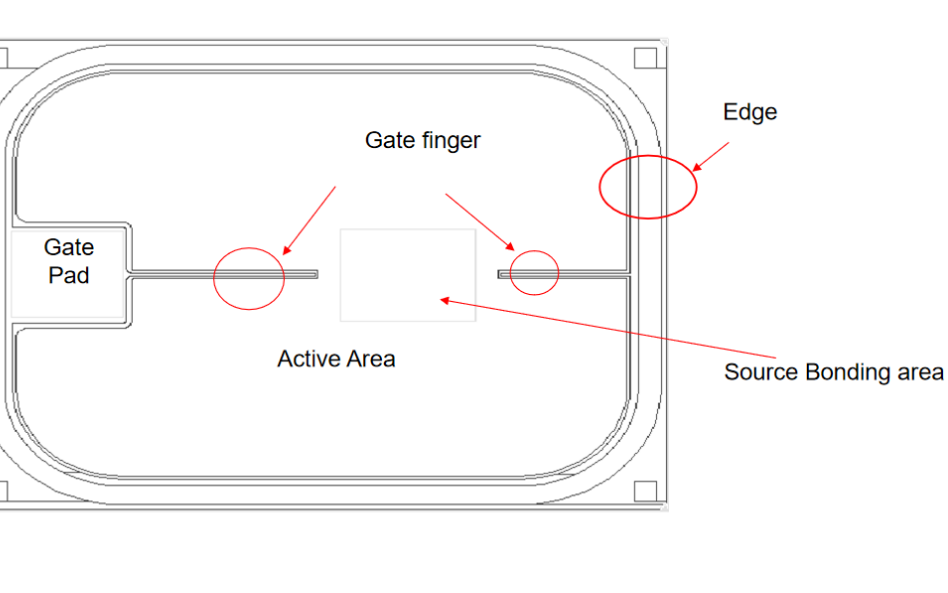

VDMOS器件結(jié)構(gòu)

VDMOS兼有雙極晶體管和普通MOS器件的優(yōu)點,無論是開關(guān)應(yīng)用還是線形應(yīng)用,VDMOS都是理想的功率器件,VDMOS主要應(yīng)用于電機調(diào)速、逆變

發(fā)表于 12-01 14:09

?115次下載

VDMOS原理介紹

VDMOS接近無限大的靜態(tài)輸入阻抗特性,非常快的開關(guān)時間,導(dǎo)通電阻正溫度系數(shù),近似常數(shù)的跨導(dǎo), 高dV/dt。

發(fā)表于 12-01 14:11

?180次下載

功率VDMOS器件的參數(shù)漂移與失效機理

功率VDMOS 器件的工作條件通常惡劣,因此其可靠性研究格外重要。本文總結(jié)了目前眾多VDMOS 器件可靠性研究的結(jié)果,著重討論了功率VDMOS

發(fā)表于 12-16 15:28

?78次下載

基于VDMOS縱向電場的影響研究

本課題的研究目的旨在從改變功率VDMOS的結(jié)構(gòu)參數(shù)入手得到外延層厚度和柵源電壓對功率VDMOS縱向電場的影響,并且在結(jié)構(gòu)參數(shù)變化的范圍內(nèi)分析出最大電場位置的變化,為優(yōu)化器件的性能起到指

發(fā)表于 11-01 18:01

?7次下載

平面VDMOS器件工藝流程和基本電參數(shù)的詳細資料說明

本文檔的主要內(nèi)容詳細介紹的是平面VDMOS器件工藝流程和基本電參數(shù)的詳細資料說明。

發(fā)表于 04-01 08:00

?27次下載

vdmos器件的具體應(yīng)用

場效應(yīng)晶體管)是一種基于MOSFET(金屬-氧化物-半導(dǎo)體場效應(yīng)晶體管)結(jié)構(gòu)的功率晶體管。它具有較寬的通道和漏極區(qū)域,能夠承受更大的電流和功率,并具備電壓阻斷功能。以下是VDMOS器件的具體應(yīng)用: 一、電子設(shè)備

vdmos和mos有什么區(qū)別

Vdmos(垂直雙擴散金屬氧化物半導(dǎo)體)和MOS(金屬氧化物半導(dǎo)體)是兩種不同類型的半導(dǎo)體器件,它們在結(jié)構(gòu)、工作原理、應(yīng)用等方面都有所區(qū)別。 1. 結(jié)構(gòu)差異 Vdmos Vdmos是一

vdmos是什么型器件

和源極之間的電流。VDMOS器件具有垂直結(jié)構(gòu),這意味著其漏極、源極和柵極之間的連接是垂直的,而不是水平的。這種結(jié)構(gòu)有助于實現(xiàn)更高的電流密度和更低的導(dǎo)通電阻。 2. VDMOS

VDMOS技術(shù)概述和特點

在過去的二十年間,MOSFET作為開關(guān)器件發(fā)展迅速。然而,由于MOSFET的通態(tài)功耗較高,導(dǎo)通電阻受擊穿電壓限制而存在一個極限,被稱為“硅極限”。為了突破這一限制,研發(fā)人員便引入了一種新型的半導(dǎo)體工藝——垂直雙擴散金屬氧化物半導(dǎo)體(VD

vdmos器件厚度對電阻的影響

vdmos器件厚度對電阻的影響

評論