人工智能(AI)近年來已廣泛應用,并迅速成為一項具有變革性的技術。AI依托于機器學習(ML)算法,而這些算法需要強大的計算能力。傳統上,開發者們依賴圖形處理器(GPU)來運行這些ML算法。GPU最初為圖形渲染而設計,但已證明在執行人工智能所需的矩陣和向量運算方面非常有效。然而,AI硬件領域的格局正在經歷巨大變革。計算需求的日益復雜和對能效提升的需求促使一些專注于特定領域AI處理器的初創公司涌現。這些公司開發的AI處理器針對ML算法進行了架構優化,與通用GPU相比,它們的性能功耗比顯著提高。

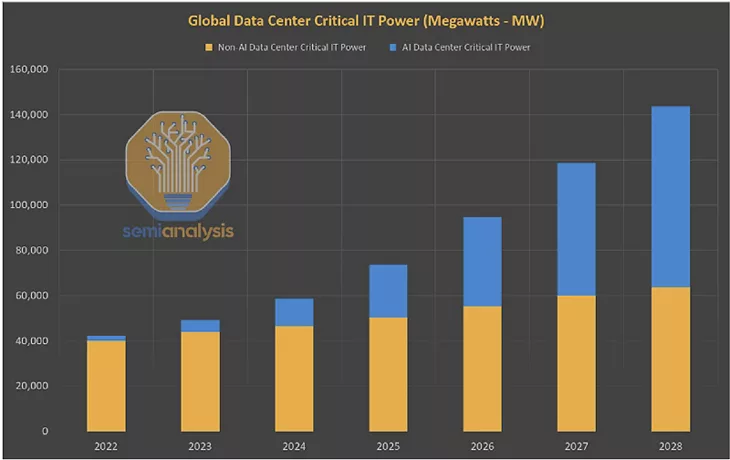

隨著AI技術的不斷發展,對更強計算能力和更高能效的需求將持續上升。根據Semianalysis的分析,預計到2028年,AI數據中心的電力需求將超過非AI數據中心,占全球數據中心總電力消耗的一半以上,而目前這一比例還不到20%。

▲圖1AI數據中心和非AI數據中心的電力需求

數據中心行業正在努力減輕電力負荷,逐步摒棄傳統的空氣冷卻方式,轉而采用成本較高但效果顯著的液冷技術。然而,單靠外部冷卻技術的進步遠遠不夠。為了應對不斷攀升的電力需求,人工智能硬件開發商還需在系統設計層面進行創新,深入挖掘全面的電力優化策略。

新思科技Foundation IP如何推動低功耗開發

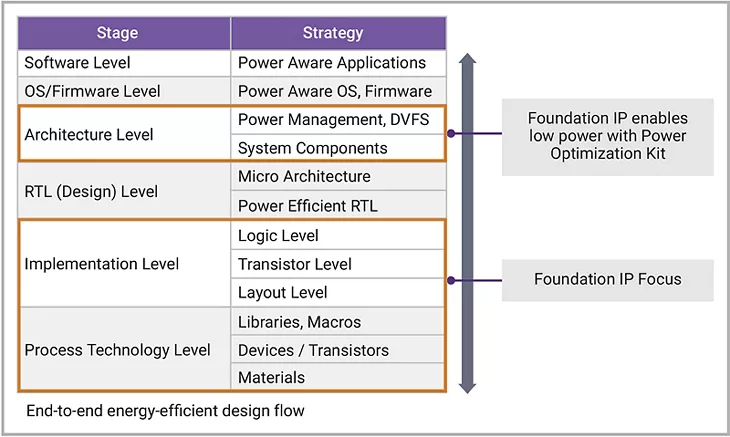

在設計系統級芯片(SoC)時,開發者可以在設計的不同階段,包括架構層次、實現層次以及底層技術層次,進行功耗優化。新思科技Foundation IP能夠助力開發者針對這些關鍵領域進行優化。SoC的功耗主要源于電路切換引起的動態功耗以及漏電(或稱靜態)功耗。動態功耗在處理器執行指令任務時產生,與CV2f成正比,這里的C代表開關電容,V為工作電壓,f是電路時鐘頻率。無論處理器處于空閑還是活躍狀態,漏電功耗都會發生,并且隨閾值電壓、晶體管尺寸和溫度而變化。在架構層面,通過采用電源門控、動態電壓頻率調整(DVFS)等電源管理技術來降低整體功耗。在實現和工藝技術層面,通過設計優化以及對邏輯單元和嵌入式存儲器操作條件的精細管理,直接影響功耗。讓邏輯單元和存儲器在維持所需性能的前提下盡可能在更低電壓下工作,同時通過專門設計的單元減少活躍節點上的電容,這些都能顯著促進功耗的降低。

新思科技憑借多代Foundation IP優化積累的深厚經驗和強大能力,在AI SoC的功耗優化中扮演著關鍵角色。新思科技Foundation IP提供的先進解決方案包括經過硅驗證的高度優化的邏輯庫、通用輸入輸出(GPIO)及嵌入式存儲器。新思科技的邏輯庫和IO與新思科技的電子設計自動化(EDA)工具協同優化,充分利用工藝技術的優勢,以實現功耗、性能和面積(PPA)的最佳平衡。新思科技的存儲器集成了針對機器學習算法的關鍵特性,為AI芯片帶來了顯著的面積及功耗節省。

▲圖2端到端的能效設計流程

讓我們深入探討新思科技Foundation IP如何幫助降低功耗,特別是針對AI處理器。

針對AI處理器的專用邏輯單元與新思科技存儲器的間距匹配

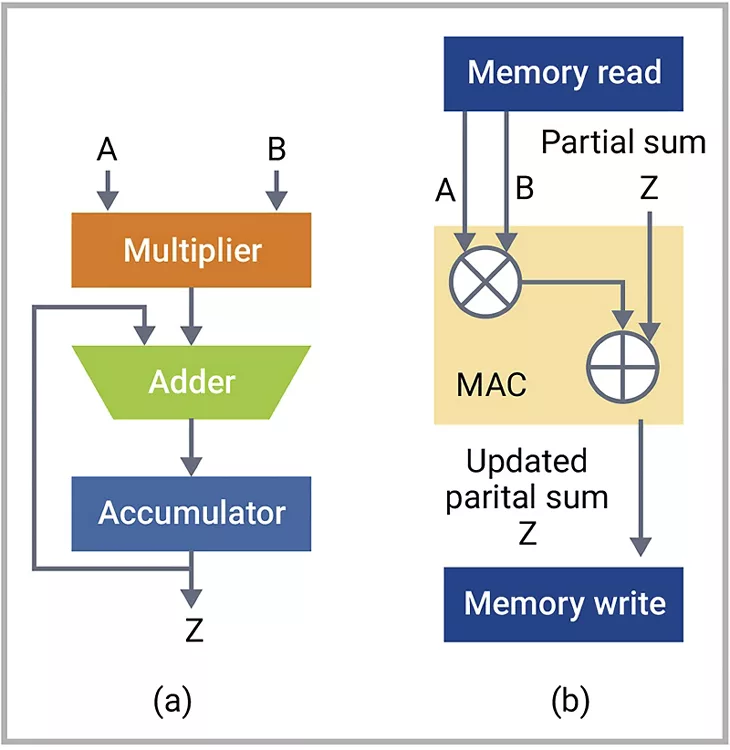

在AI處理器中,無論是訓練還是推理任務,大量的計算活動(70-90%或更多)都致力于乘累加(MAC)操作,這是矩陣乘法和卷積的基礎。新思科技提供的邏輯庫包含了專為AI處理器設計的復雜邏輯,支持MAC功能。這些單元具備如融合乘加能力等特性,有助于減少設計的凈長度和整體電容,從而顯著降低動態功耗。對于AI芯片而言,集成高效能存儲器同樣重要。在機器學習模型中,特別是在推理任務中,參數權重存儲在存儲器中,并頻繁被MAC單元訪問以進行計算(見圖3)。新思科技提供了與MAC單元間距匹配的嵌入式存儲器。這意味著存儲器和邏輯單元的物理布局在尺寸和間距上進行了協同優化。這種集成設計策略帶來了更短的互連,某些應用中已證明能減少33%的功耗。

▲圖3(a)MAC單元框圖(b)MAC單元的存儲器讀寫

可定制的超低電壓庫

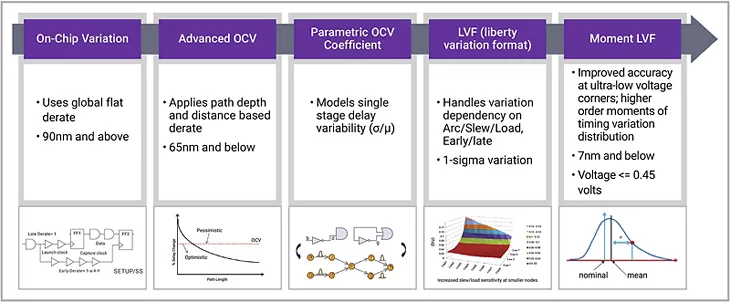

在先進技術中,設計在超低供電電壓下運行的芯片,特別是在0.5V以下,極具挑戰性,需要非常細致的設計和驗證。然而,使用低供電電壓的功耗效益可能是巨大的,因為降低電壓會對動態功耗產生二次方減少效應。AI處理器通常依賴于巨大的并行性來提高性能,不需要在高頻下運行。它們特別可以從使用超低電壓庫中受益。新思科技通過其可定制的超低電壓邏輯庫支持低功耗芯片設計。這些庫基于高質量和詳盡的驗證,采用先進的表征技術,在廣泛的工藝、電壓和溫度(PVT)條件下進行測試。低電壓帶來的挑戰包括降低的噪聲裕度和對制造變異的敏感性增加。隨著供電電壓的降低,信號改變電路下一階段狀態的能力減弱。這可能導致信號更像脈沖,通過電路傳播的時間更長。這種延遲可能會影響電路的關鍵時序方面,包括建立時間和保持時間。為了解決這個問題,開發者應考慮額外的因素,如軌到軌脈沖檢查、針對芯片內變異(OCV)的額外時序裕度、保持時序的高西格瑪要求以及時鐘偏斜建議。新思科技Foundation IP的開發者在開發單元時會考慮到這些變異,單元會經過高西格瑪蒙特卡羅模擬以進行穩健性驗證,而謹慎使用基于矩的庫變異格式(LVF)允許對制造變異的概率特性進行精確和詳細的建模

▲圖4低供電電壓導致的片上變異復雜性提升

具有分數驅動強度的邏輯單元

具有更高驅動強度的邏輯單元消耗更多功耗,并且由于其更大的晶體管而傾向于有更高的漏電。對于非關鍵路徑,已經通過使用高閾值電壓(VT)單元進行了功耗優化,可以通過使用具有分數驅動強度的單元來進一步降低功耗。新思科技邏輯庫組合包括一系列這樣的分數驅動強度單元,包括驅動強度小于一的單元。

功耗優化套件

為了增強功耗節省,新思科技在其標準單元平臺中提供了功率優化套件(POK)。該套件包括各種專用邏輯單元,旨在實現先進的電源管理技術。這包括幫助減少靜態功耗的電源開關和隔離單元,通過在不需要時啟用塊關閉。該套件還包括電平轉換器,通過允許不同塊根據其性能要求在不同的電壓下運行,協助動態功耗降低。此外,POK還具有多比特版本的隔離單元、保持觸發器和電平轉換器,有助于減少凈長度和整體單元面積。

超低漏電IO

在具有AI芯片的SoC中,雖然片上組件在低電壓下運行,但這些需要連接到在更高電壓下運行的片外組件。設計支持如此電壓范圍的GPIO極具挑戰性,大多數公司轉而使用電平轉換器,給設計增加了不必要的面積和功耗。新思科技提供了一套全面的超低漏電IO,支持低至0.5V的電壓。這些相同的IO還支持1.8V IO供電,提高整體系統可靠性。具有AI芯片的SoC也更大,需要嚴格的靜電放電(ESD)保護標準。新思科技提供的IO解決方案包括強大的ESD保護,能夠處理高達CDM 7A的電流。這轉化為更高效、可靠和具有成本效益的AI SoC設計。

非易失性存儲器和基于鎖存的存儲器

新思科技提供了一系列先進的內存解決方案,包括嵌入式磁阻隨機存取存儲器(MRAM)和電阻隨機存取存儲器(RRAM),它們提供的密度顯著高于傳統的SRAM。對于以讀取為主的應用,例如存儲訓練數據,用MRAM或RRAM替換SRAM或片外DRAM可以顯著提高系統級PPA。這些非易失性存儲器(NVM)減少了硅面積和所需組件的數量。此外,由于它們不需要恒定功率來維持其數據狀態──與DRAM不同──它們消除了頻繁刷新周期的需要,從而降低了靜態功耗并減少了漏電流。新思科技還提供基于鎖存的存儲器,為較小的內存實例節省了大量面積。這些對于特定的AI功能特別有用,如激活和池化,這些功能需要許多小的內存實例。此外,新思科技提供了專門的多端口存儲器,能夠同時處理多個內存訪問請求,有助于緩解內存瓶頸并提高整體性能。

存儲器中的稀疏性和轉置支持

在許多機器學習模型中,要計算的數據中有相當一部分是零值字,可以在讀/寫操作期間跳過以節省功率。為了利用這種數據稀疏性,新思科技在其存儲器中引入了一項名為WAZ(Word All Zero)的創新功能。該功能通過檢測并跳過零值,可以將功耗降低高達60%。此外,新思科技開發了一種在存儲器中以轉置格式存儲數據的方法。這意味著矩陣元素在存儲器中對齊,以匹配其在計算期間的訪問模式。結果,矩陣操作執行更快,節省了能源,提高了整體效率。

總結

隨著應用需求與AI技術的持續演進,開發具備強大計算能力且高效節能的AI處理器已成為普遍需求。傳統的基于GPU架構以及新興的優化AI架構正將能效推向極致。傳統上為CPU及早期GPU優化的庫和存儲器方案,已難以滿足當下AI SoC設計嚴苛且特定的需求。作為基礎IP領域的佼佼者,新思科技憑借二十余年的創新歷程,始終致力于最優PPA的研發,持續推出專業解決方案,以滿足半導體行業不斷變化且極具挑戰的設計需求。在強大的研發團隊與技藝精湛的應用工程師共同支持下,新思科技發揮其在邏輯庫、IO及嵌入式存儲器領域的深厚專長,提供獨具特色的可調解決方案,全面提升AI芯片的性能范疇。

-

處理器

+關注

關注

68文章

19865瀏覽量

234454 -

存儲器

+關注

關注

38文章

7644瀏覽量

166976 -

AI

+關注

關注

88文章

34890瀏覽量

277738 -

人工智能

+關注

關注

1806文章

48940瀏覽量

248352

原文標題:新思科技Foundation IP:AI芯片低功耗設計必選項

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

新思科技攜手微軟借助AI技術加速芯片設計

能效比達2TOPS/W!解密邊緣AI芯片低功耗設計之法

芯片為什么要做低功耗設計?

芯原推出低功耗AI降噪與AI超分辨率系列IP

聆思科技獲得Ceva-Waves Wi-Fi 6 IP授權

AN-1111: 使用ADuCM360/ADuCM361時的降低功耗選項

新思科技Foundation IP:AI芯片低功耗設計必選項

新思科技Foundation IP:AI芯片低功耗設計必選項

評論