帶Serdes的高速以太網(wǎng)接口流片后如果功能不正常,可以采用帶有相同接口類(lèi)型的FPGA進(jìn)行測(cè)試定位問(wèn)題。本文簡(jiǎn)單的介紹一種通過(guò)FPGA來(lái)對(duì)基于四通道serdes的40G/10G以太網(wǎng)接口PMA和PCS層進(jìn)行鏈路連接測(cè)試的方法,歡迎大家留言討論指導(dǎo)。

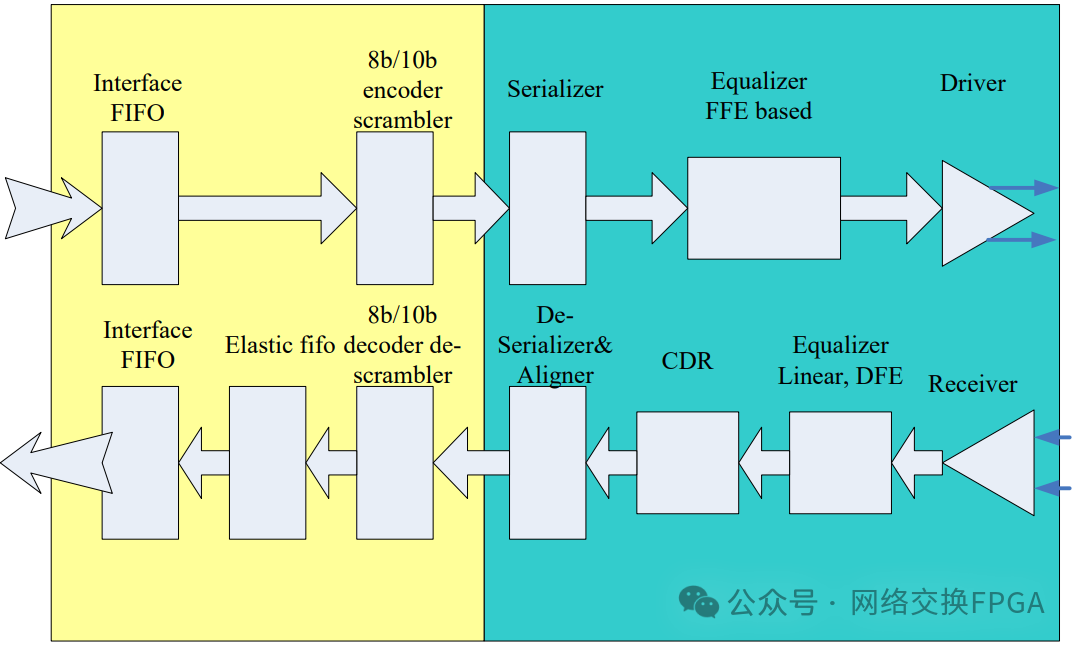

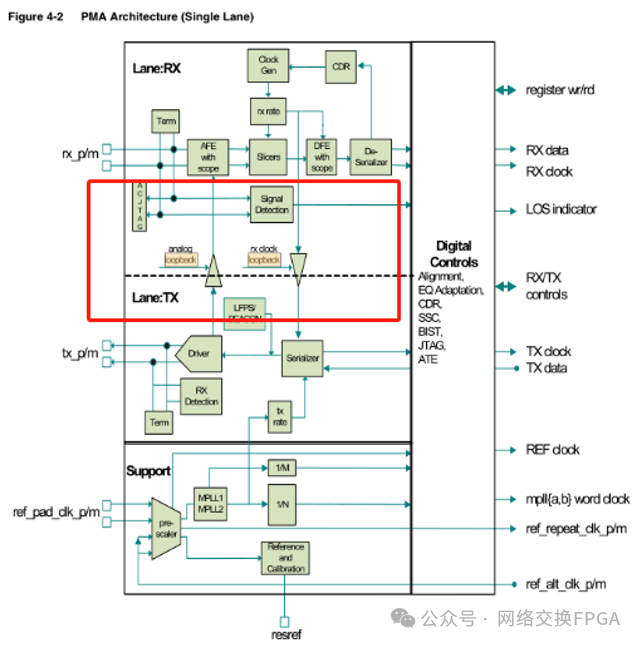

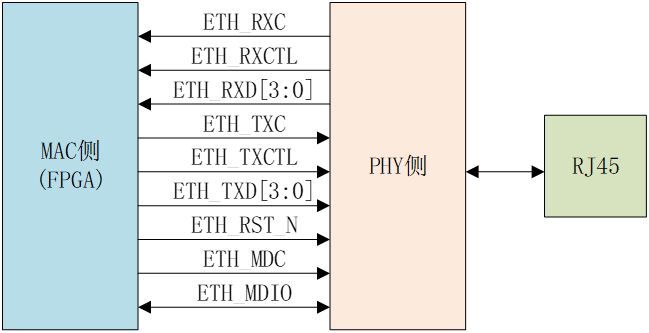

SERDES 是英文 SERializer(串行器)/DESerializer(解串器)的簡(jiǎn)稱(chēng)。它是一種時(shí)分多路復(fù)用(TDM)、點(diǎn)對(duì)點(diǎn)的通信技術(shù),即在發(fā)送端多路低速并行信號(hào)被轉(zhuǎn)換成高速串行信號(hào),經(jīng)過(guò)傳輸媒體(光纜或銅線(xiàn)),最后在接收端高速串行信號(hào)重新轉(zhuǎn)換成低速并行信號(hào)。這種點(diǎn)對(duì)點(diǎn)的串行通信技術(shù)充分利用傳輸媒體的信道容量,減少所需的傳輸信道和器件引腳數(shù)目,從而減少了傳輸線(xiàn)之間的干擾,增大了背板傳輸距離,并且大大降低通信成本。同時(shí)帶來(lái)了諸如減少布線(xiàn)沖突、降低開(kāi)關(guān)噪聲、更低的功耗和封裝成本等許多好處。而 SERDES 技術(shù)的主要缺點(diǎn)是需要非常精確、超低抖動(dòng)的元件來(lái)提供用于控制高數(shù)據(jù)速率串行信號(hào)所需的參考時(shí)鐘。即使嚴(yán)格控制元件布局,使用長(zhǎng)度短的信號(hào)并遵循信號(hào)走線(xiàn)限制,這些接口的抖動(dòng)余地仍然是非常小。 SERDES 主要由物理介質(zhì)相關(guān)( PMD)子層、物理媒介附加(PMA)子層和物理編碼子層( PCS )所組成。PMD 是負(fù)責(zé)串行信號(hào)傳輸?shù)?a href="http://www.tjjbhg.com/v/tag/2364/" target="_blank">電氣層,PMA 負(fù)責(zé)串化/解串化,PCS 負(fù)責(zé)數(shù)據(jù)流的編碼/解碼,在 PCS 的上面是上層數(shù)字 IP 功能。一般的高速接口均是由 2 個(gè) IP(時(shí)鐘域)組成,上層是數(shù)字 IP,一般執(zhí)行接口協(xié)議相關(guān)的處理,下層為 SERDES 層,主要執(zhí)行串并,并串轉(zhuǎn)換的處理。 如下圖所示,藍(lán)色背景子模塊為 PCS 層,是標(biāo)準(zhǔn)的可綜合 CMOS 數(shù)字邏輯,可以硬邏輯實(shí)現(xiàn)。褐色背景的子模塊是 PMA 層,是數(shù)模混合 CML/CMOS 電路,是理解 SERDES 區(qū)別于并行接口的關(guān)鍵,也是本文要討論的內(nèi)容。

發(fā)送方向(Tx)信號(hào)的流向: 處理器軟邏輯(fabric)送過(guò)來(lái)的并行信號(hào),通過(guò)接口FIFO(Interface FIFO),送給 8B/10B 編碼器(8B/10B encoder)或擾碼器(scrambler),以避免數(shù)據(jù)含有過(guò)長(zhǎng)連零或者連一,之后送給串行器(Serializer)進(jìn)行 并->串 轉(zhuǎn)換,串行數(shù)據(jù)經(jīng)過(guò)均衡器(equalizer)調(diào)理,由驅(qū)動(dòng)器(driver)發(fā)送出去。 接收方向(Rx)信號(hào)的流向, 外部串行信號(hào)由線(xiàn)性均衡器(Linear Equalizer)或判決反饋均衡器(Decision Feedback Equalizer)調(diào)理,去除一部分確定性抖動(dòng)(Deterministic jitter)。CDR 從數(shù)據(jù)中恢復(fù)出采樣時(shí)鐘,經(jīng)解串器變?yōu)閷?duì)齊的并行信號(hào)。8B/10B 解碼器(8B/10B decoder)或解擾器(descambler)完成解碼或者解擾。如果是異步時(shí)鐘系統(tǒng)(plesio-synchronous system),在用戶(hù) FIFO 之前還應(yīng)該有彈性 FIFO 來(lái)補(bǔ)償頻差。 在測(cè)試前,可以先搭建仿真驗(yàn)證環(huán)境,對(duì)FPGA和芯片版本的40G/10G接口進(jìn)行仿真。

仿真目的:

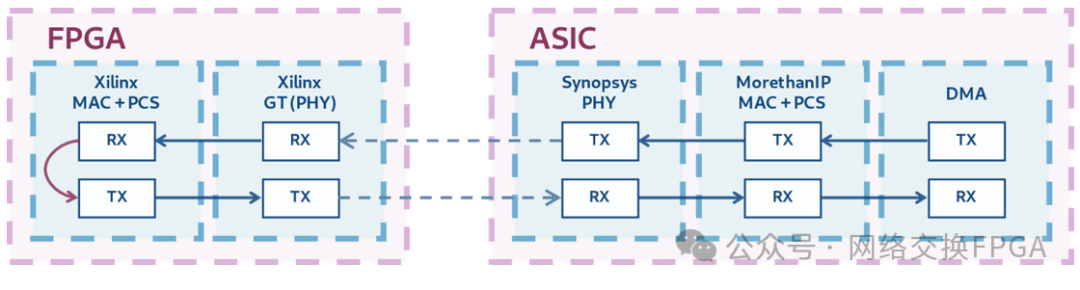

確定FPGA在10GBASE-KR與10GBASE-R模式下與ASIC連接鏈路的穩(wěn)定,以及鏈路具體狀態(tài)。

連接關(guān)系與數(shù)據(jù)通路:

FPGA與ASIC兩側(cè)的PCS均顯示每個(gè)bus的四個(gè)lane進(jìn)入鎖定狀態(tài)(xl_block_lock為高),但四個(gè)lane對(duì)齊的標(biāo)志位xl_align_done為0。與實(shí)際測(cè)試表現(xiàn)一致。

通過(guò)仿真進(jìn)行異常定位:通過(guò)FPGA側(cè)的PCS RTL信號(hào)追查鏈路無(wú)法對(duì)齊、aligndone標(biāo)志無(wú)法產(chǎn)生的原因。

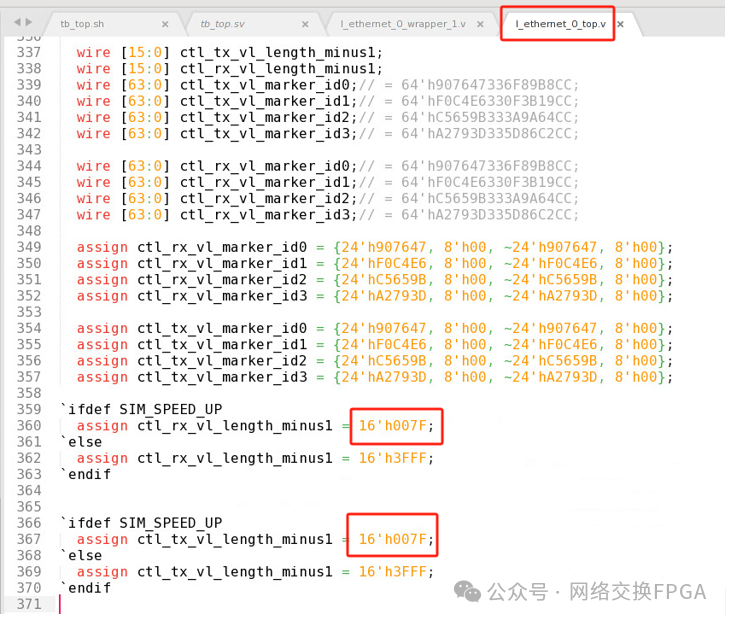

在FPGA的PCS的對(duì)齊邏輯中發(fā)現(xiàn)其檢查對(duì)齊標(biāo)志(alignmarker)之前,需要lane保持同步鎖定一定時(shí)間,該時(shí)間由代碼如下位置指定:

(1)當(dāng)仿真環(huán)境未添加SIM_SPEED_UP宏定義,仿真中PCS檢查align marker的時(shí)間間隔設(shè)置為3FFF(16383)個(gè)block,RTL仿真跑到這個(gè)時(shí)間間隔需要花費(fèi)極大的時(shí)間。另外觀(guān)察到,F(xiàn)PGA一側(cè)添加SIM_SPEED_UP宏定義后,上述參數(shù)為3F(原代碼中),該參數(shù)與ASIC中PCS的vl_intvl寄存器配置的7F值非常像,而且結(jié)合PCS手冊(cè)描述和網(wǎng)表反推,vl_intvl同樣是與對(duì)齊標(biāo)志間隔相關(guān)的寄存器,該寄存器在實(shí)際上板、仿真時(shí)應(yīng)當(dāng)設(shè)置不一樣的值:對(duì)于滿(mǎn)足802.3的40GBASE-R標(biāo)準(zhǔn)的情況,需要設(shè)置為16383,對(duì)于仿真,需要減小該數(shù)值以縮短仿真的鏈路對(duì)齊時(shí)間。

(2)在FPGA中打開(kāi)SIM_SPEED_UP宏定義進(jìn)行仿真。FPGA側(cè)對(duì)齊標(biāo)志間隔參數(shù)(ctl_Xx_vl_length_minus1)設(shè)置為3F,ASIC的vl_intvl寄存器保持7F值。進(jìn)行仿真,追查對(duì)齊相關(guān)信號(hào),找到FPGA側(cè)PCS查找align marker的邏輯,PCS找到第一個(gè)marker后,在下一個(gè)應(yīng)當(dāng)檢測(cè)到marker的位置沒(méi)有繼續(xù)找到marker,因此PCS的連接狀態(tài)從ALIGNING(對(duì)齊中)和IDLE(失去對(duì)齊)中反復(fù)跳轉(zhuǎn),無(wú)法進(jìn)入ALIGNED(已對(duì)齊)狀態(tài)。該現(xiàn)象直接說(shuō)明了對(duì)端(ASIC側(cè))的PCS在鏈路中插入align marker的間隔與FPGA側(cè)的不一致,因此兩設(shè)備無(wú)法建立對(duì)齊鏈路。

(3)將仿真中的FPGA的ctl_Xx_vl_length_minus1與ASIC的vl_intvl寄存器設(shè)置為同樣的值(7F),讓兩側(cè)的PCS在相同的7F個(gè)block間隔后插入或檢測(cè)align marker。仿真觀(guān)察到FPGA的PCS對(duì)齊狀態(tài)機(jī)成功進(jìn)入ALIGNED狀態(tài),表明4個(gè)lane的對(duì)齊基本條件能夠滿(mǎn)足。結(jié)合以上仿真結(jié)果,可以得知之前ASIC側(cè)的vl_intvl寄存器值配置為7F為快速仿真設(shè)置,與802.3要求的3FFFF(16384)不符,實(shí)際芯片測(cè)試中需要將vl_intvl寄存器配置為3FFF進(jìn)行測(cè)試。

40G線(xiàn)速仿真:通常在A(yíng)SIC IP核中,PHY和MAC接口處寄存器用來(lái)配置是否工作在40G線(xiàn)速狀態(tài),如MAC沒(méi)有配置tx_ipg_comp_reg寄存器,該寄存器用于補(bǔ)償PCS插入對(duì)齊標(biāo)志造成的40G滿(mǎn)速時(shí)的線(xiàn)速損耗,那么MAC就無(wú)法運(yùn)行在40G線(xiàn)速模式。此時(shí),對(duì)齊標(biāo)志占比1/16384,導(dǎo)致?lián)p失速率的實(shí)際速率為0.999938*40Gbps,實(shí)際芯片測(cè)試中,最高速率能夠達(dá)到0.999928*40Gbps不丟幀,該比例與對(duì)齊標(biāo)志損耗接近。若配置相關(guān)寄存器后,則鏈路中對(duì)齊標(biāo)志就會(huì)刪除,此時(shí)芯片實(shí)際測(cè)試可以跑滿(mǎn)40G線(xiàn)速。如下視頻是A芯片實(shí)際測(cè)試40G打流99%不丟幀的視頻:

由于仿真無(wú)法百分百跟真實(shí)場(chǎng)景對(duì)應(yīng),尤其是PMAC側(cè)數(shù)模混合部分,在仿真環(huán)境中往往被簡(jiǎn)化模型替代,仿真通過(guò),但實(shí)際上板或流片則可能會(huì)有問(wèn)題。以下介紹FPGA與ASIC實(shí)際上板測(cè)試情況。

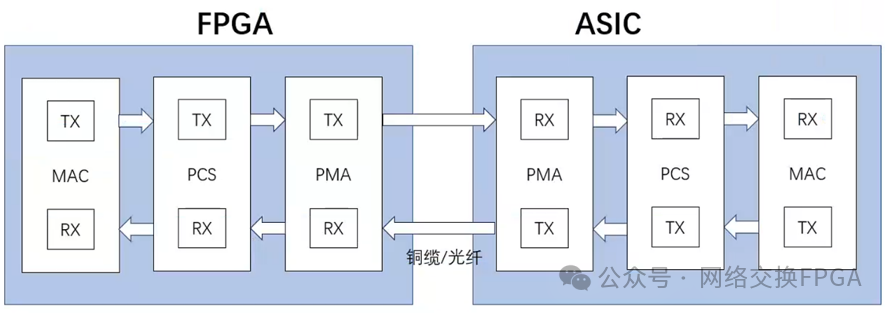

1、硬件連接方式

使用銅纜或者光纖將FPGA和ASIC側(cè)的光口進(jìn)行連接。ASIC側(cè)的IP需要根據(jù)需求或者手冊(cè)配置成正常工作模式。FPGA側(cè)只用例化相關(guān)IP,并進(jìn)行管腳約束。FPGA側(cè)可使用IP參考第二部分。

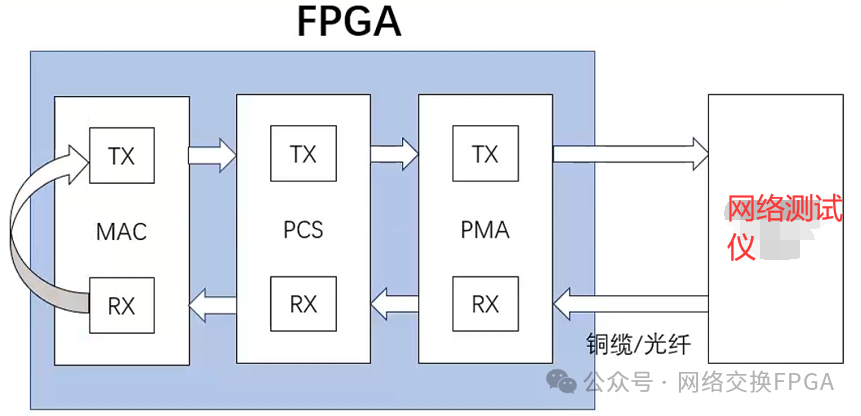

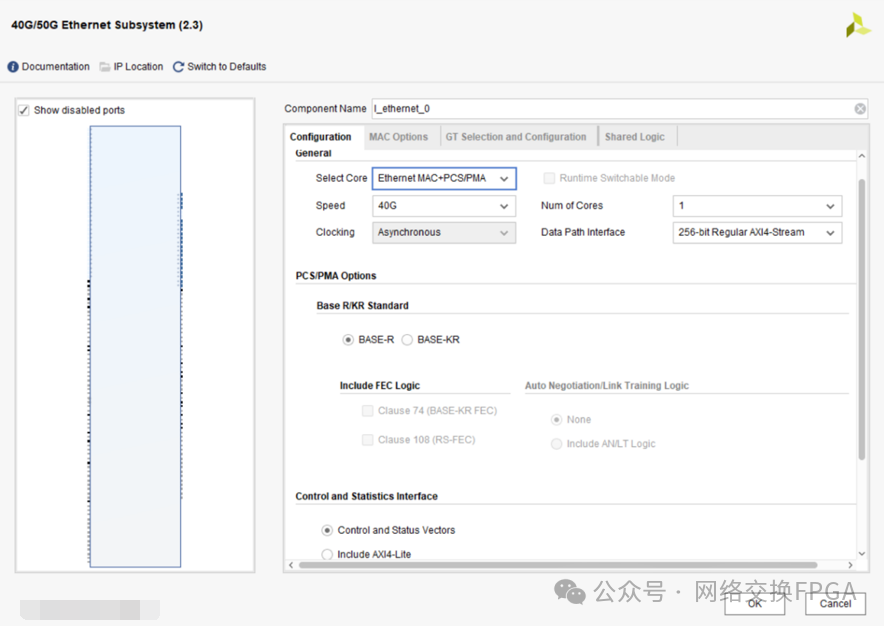

使用上述方式進(jìn)行監(jiān)測(cè)時(shí)首先要保證FPGA側(cè)正常工作。可以通過(guò)連接網(wǎng)絡(luò)測(cè)試儀進(jìn)行打流回環(huán)來(lái)驗(yàn)證。如下圖所示。本文針對(duì)40G/10G高速以太網(wǎng)接口利用FPGA對(duì)同樣接口速率的40G/10G以太網(wǎng)接口serdes和PCS層進(jìn)行互連互通,進(jìn)而對(duì)流片后的serdes芯片進(jìn)行調(diào)試(也可能是芯片的serdes或PCS工作模式配置不正確)或故障定位。FPGA側(cè)40G/10G可以參考xilinx官方的兩個(gè)文檔pg211和ug578,其中pg211介紹40g/50g的MAC+PCS等相關(guān)的知識(shí)點(diǎn),ug578介紹GTY的知識(shí),具體可以到官網(wǎng)下載,學(xué)習(xí)查看。FPGA側(cè)40G/10G接口工作是否正常可以參考文章:UltraScale+FPGA中Serdes的多l(xiāng)ane對(duì)齊異常解決方案。

同時(shí)由于PCS的工作機(jī)制,其必須在鏈路正常穩(wěn)定的情況下才能對(duì)數(shù)據(jù)進(jìn)行正常傳輸。所以如果鏈路有問(wèn)題,PCS部分會(huì)有相關(guān)寄存器反映當(dāng)前狀態(tài)。具體寄存器或者內(nèi)部信號(hào)參考第三部分。

2、FPGA使用IP

1)對(duì)端是40G以太網(wǎng)接口(4lane 40)

示例工程如下:(略)

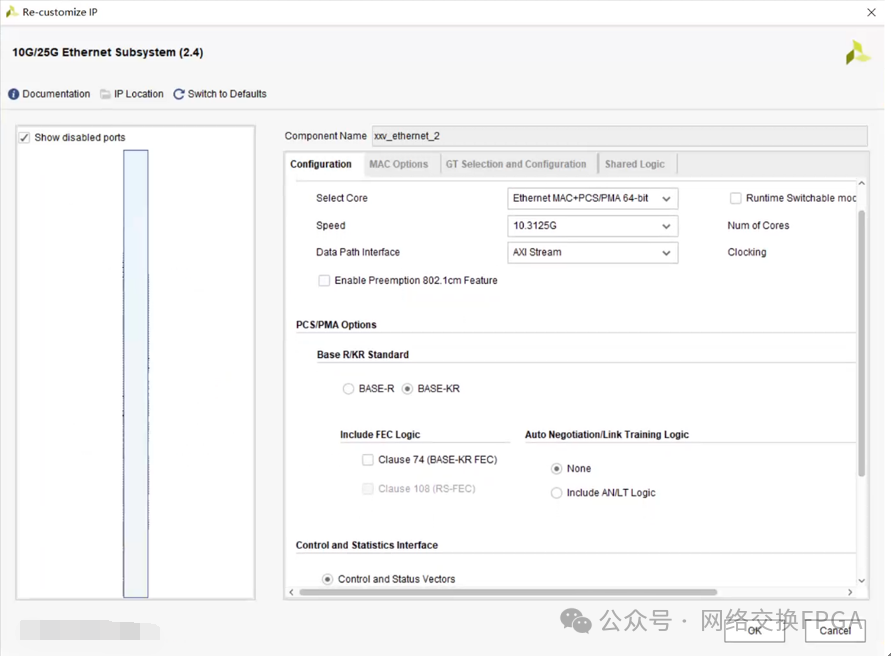

2)對(duì)端是10G以太網(wǎng)接口(單lane 10)

3)對(duì)端是10G以太網(wǎng)接口(4lane 10)

3、信號(hào)抓取說(shuō)明

1)如果使用40G/50G Ethernet Subsystem或者10G/25G Ethernet Subsystem,直接監(jiān)測(cè)相關(guān)狀態(tài)寄存器。

| RX PCS通道對(duì)齊狀態(tài) | ||

| 寄存器 | 含義 | 備注 |

| stat_rx_synced[3:0] | 字邊界已同步。這些信號(hào)用于指示 PCS 通道是否已完成字邊界同步。值為 1 表示對(duì)應(yīng) PCS 通道已實(shí)現(xiàn)字邊界同步,并且已接收到 PCS 通道標(biāo)記。對(duì)應(yīng)于第 82.3 條中所定義的管理數(shù)據(jù)輸入/輸出 (MDIO) 寄存器位 3.52.7:0 和 3.53.11:0。此輸出對(duì)電平敏感。 | |

| stat_rx_synced_err[3:0] | 字邊界同步錯(cuò)誤。這些信號(hào)用于指示在相應(yīng)的 PCS 通道內(nèi)進(jìn)行字邊界同步期間,是否發(fā)生錯(cuò)誤。值為 1 表示由于同步報(bào)頭成幀位錯(cuò)誤或者從未收到 PCS 通道標(biāo)記,對(duì)應(yīng) PCS 通道已丟失字邊界同步。此輸出對(duì)電平敏感。 | |

| stat_rx_mf_len_err[3:0] | PCS 通道標(biāo)記長(zhǎng)度錯(cuò)誤。這些信號(hào)用于指示相應(yīng)通道內(nèi)是否發(fā)生了 PCS 通道標(biāo)記不匹配(即,接收到的 PCS 通道標(biāo)記間隔字?jǐn)?shù)并非 ctl_rx_vl_length_minus1)。值為 1 表示對(duì)應(yīng)通道接收 PCS 通道標(biāo)記的間隔錯(cuò)誤。它將保持高電平,直至消除錯(cuò)誤狀況為止。 | |

| stat_rx_mf_repeat_err[3:0] | PCS 通道標(biāo)記字錯(cuò)誤。這些信號(hào)用于表示在相應(yīng)通道內(nèi)檢測(cè)到構(gòu)成的 PCS 通道標(biāo)記字錯(cuò)誤。值為 1 表示發(fā)生了錯(cuò)誤。此輸出將脈沖 1 個(gè)時(shí)鐘周期,以指示錯(cuò)誤狀況。脈沖可在不間斷的連續(xù)周期內(nèi)發(fā)生。 | |

| stat_rx_mf_err[3:0] | 當(dāng) stat_rx_aligned 值為 1 時(shí),表示全部通道都已對(duì)齊/去歪斜,并且接收器已準(zhǔn)備好接收包數(shù)據(jù)。 | |

| stat_rx_aligned_err |

當(dāng) stat_rx_aligned_err 值為 1 時(shí),將發(fā)生以下 2 種情況之一: ? 通道對(duì)齊經(jīng)多次嘗試后失敗。 ? 通道對(duì)齊已丟失(stat_rx_aligned 斷言有效,隨后被取反) |

|

| stat_rx_misaligned | 對(duì)齊錯(cuò)誤。此信號(hào)表示通道對(duì)齊器并未在所有通道上都接收到期望的 PCS 通道標(biāo)記。在所有通道上都至少接收到 1 個(gè) PCS 通道標(biāo)記并且至少接收到 1 個(gè)錯(cuò)誤的通道標(biāo)記后,此信號(hào)才會(huì)斷言有效。此狀況的發(fā)生比錯(cuò)誤晚 1 個(gè)元幀。如果從未正確接收到任何通道標(biāo)記,則此信號(hào)不會(huì)斷言有效。通道標(biāo)記錯(cuò)誤通過(guò)對(duì)應(yīng)的 stat_rx_mf_err 信號(hào)來(lái)指示。此輸出將脈沖 1 個(gè)時(shí)鐘周期,以指示錯(cuò)誤狀況。脈沖可在不間斷的連續(xù)周期內(nèi)發(fā)生。 | |

|

stat_rx_framing_err_[3:0][3:0] stat_rx_framing_err_valid_[3:0] |

這組總線(xiàn)旨在用于保留同步報(bào)頭錯(cuò)誤記錄。每個(gè) PCS 通道都有一對(duì)輸出。 stat_rx_framing_err_[PCSL_LANES-3:0] 輸出總線(xiàn)用于指示已接收到的同步報(bào)頭錯(cuò)誤數(shù)量,當(dāng)對(duì)應(yīng) stat_rx_framing_err_valid_[PCSL_LANES-3:0] 采樣為 1 時(shí),此輸出總線(xiàn)合格(即,僅限在此情況下其值才有效)。 | |

| stat_rx_vl_number[3:0][1:0] | 每個(gè)總線(xiàn)所指示的特定 PCS 通道的狀態(tài)反映在特定狀態(tài)管腳上。例如,stat_rx_vlane_number_0 所指示的 PCS 通道的狀態(tài)反映在其它狀態(tài)信號(hào)的管腳 0 上。這些總線(xiàn)可用于檢測(cè)是否尚未找到 PCS 通道或者是否某一 PCS 通道已映射到多個(gè)狀態(tài)管腳。 | |

| stat_rx_vl_demuxed[3:0] | 在每個(gè)通道上都達(dá)成字邊界同步后,如果該總線(xiàn)的位為 1,則表示已正確查找到對(duì)應(yīng) PCS 通道,并且已對(duì)其正確完成逆多路復(fù)用。 | |

| stat_rx_block_lock[3:0] | 每個(gè) PCS 通道的塊鎖定狀態(tài)。值為 1 表示對(duì)應(yīng)通道已達(dá)到第 82 條中定義的塊鎖定狀態(tài)。對(duì)應(yīng)于第 82.3 條中所定義的 MDIO 寄存器位 3.50.7:0 和 3.51.11:0。此輸出對(duì)電平敏感。 | |

| stat_rx_aligned | 所有 PCS 通道均已對(duì)齊/去歪斜。此信號(hào)表示是否所有 PCS 通道均已對(duì)齊并去歪斜。值為 1 表示所有 PCS 通道均已對(duì)齊并去歪斜。當(dāng)此信號(hào)為 1 時(shí),表示 RX 路徑已對(duì)齊并且可接收包數(shù)據(jù)。當(dāng)此信號(hào)為 0 時(shí),表示存在本地故障狀況。這也對(duì)應(yīng)于第 82.3 條中所定義的 MDIO 寄存器位3.50.12。此輸出對(duì)電平敏感 | |

| stat_rx_hi_ber | 誤碼率 (BER) 過(guò)高指示符。設(shè)置為 1 時(shí),BER 過(guò)高(根據(jù) IEEE 802.3-2015 標(biāo)準(zhǔn)的定義)。對(duì)應(yīng)于第 82.3 條中所定義的 MDIO 寄存器位 3.32.1。此輸出對(duì)電平敏感。 | |

| stat_rx_status | PCS 狀態(tài)。值為 1 表示 PCS 已對(duì)齊且未處于 hi_ber 狀態(tài)。對(duì)應(yīng)于第 82.3 條中所定義的 MDIO 寄存器位 3.32.12。此輸出對(duì)電平敏感。當(dāng) stat_rx_aligned 為 1 且 stat_rx_hi_ber 為 0 時(shí),此輸出設(shè)置為 1。此設(shè)置由 IEEE 802.3-2015 標(biāo)準(zhǔn)定義。 | |

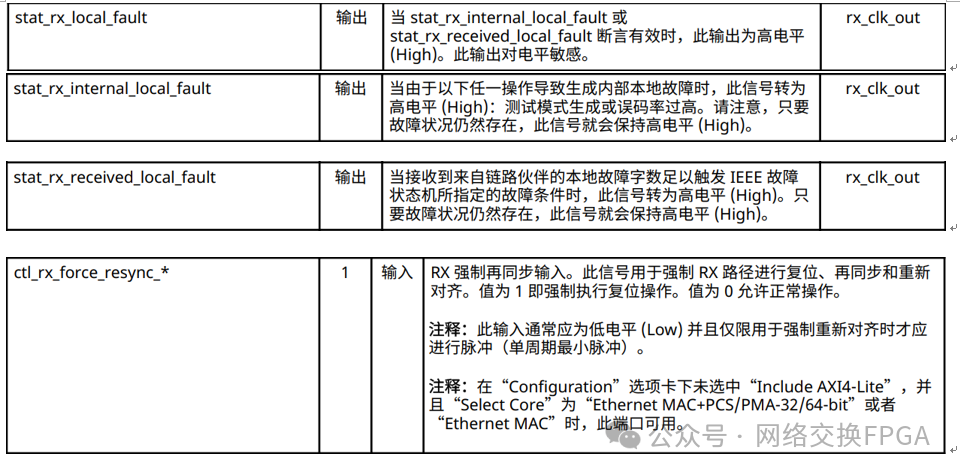

| stat_rx_local_fault | 當(dāng)stat_rx_received_local_fault 或stat_rx_internal_local_fault 斷言有效時(shí),此輸出設(shè)置為 1。此輸出對(duì)電平敏感。 | |

| RX錯(cuò)誤狀態(tài) | ||

| stat_rx_bad_fcs | 當(dāng)此信號(hào)值為 1 時(shí),表示錯(cuò)誤檢測(cè)邏輯已在接收到的包中發(fā)現(xiàn)接收的 CRC32 值與期望的值不匹配。當(dāng)檢測(cè)到 CRC32 錯(cuò)誤時(shí),接收到的包將被標(biāo)記為包含錯(cuò)誤,并隨在上一次傳輸(即 rx_eopout 斷言有效的周期)期間斷言有效的 rx_errout 一起發(fā)送,但 ctl_rx_ignore_fcs 斷言有效的情況下除外。每次檢測(cè)到 CRC32 錯(cuò)誤時(shí),都將斷言此信號(hào)有效并保持 1 個(gè)時(shí)鐘周期。 | |

| stat_rx_bad_code[1:0] | 此信號(hào)用于指示RX PCS 接收狀態(tài)機(jī)處于IEEE 802.3-2015 標(biāo)準(zhǔn)所定義的 RX_E 狀態(tài)的周期數(shù)。 | |

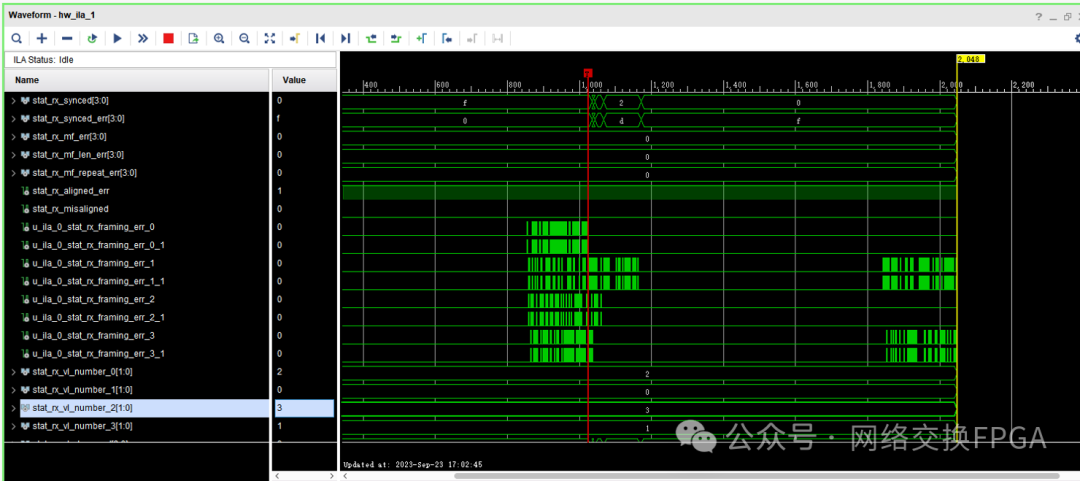

下圖為A芯片 40G接口的實(shí)測(cè)截圖。stat_rx_synced應(yīng)始終保持4’hF,不穩(wěn)定說(shuō)明信號(hào)質(zhì)量太差。一定程度上反映ASIC側(cè)的時(shí)鐘質(zhì)量問(wèn)題。

2)如果40G PCS部分使用相關(guān)代碼,可以基于以下信號(hào)展開(kāi)監(jiān)測(cè):

40G PCS和對(duì)端鏈路建立過(guò)程主要有ABC三個(gè)階段:

A、同步頭鎖定:

監(jiān)測(cè)信號(hào):

/i_RX_CORE/i_RX_LANE0/i_RX_WD_SYNC_0/align_status[1:0]

/i_RX_CORE/i_RX_LANE0/i_RX_WD_SYNC_1/align_status[1:0]

/i_RX_CORE/i_RX_LANE1/i_RX_WD_SYNC_0/align_status[1:0]

/i_RX_CORE/i_RX_LANE1/i_RX_WD_SYNC_1/align_status[1:0]

正常情況下恒為1。

0表示復(fù)位,2表示鎖定失敗

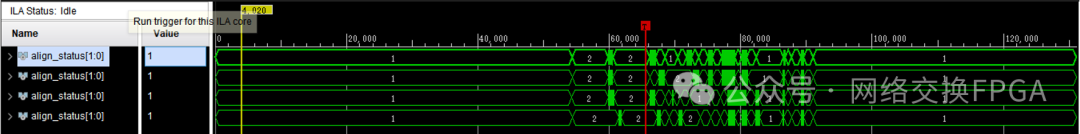

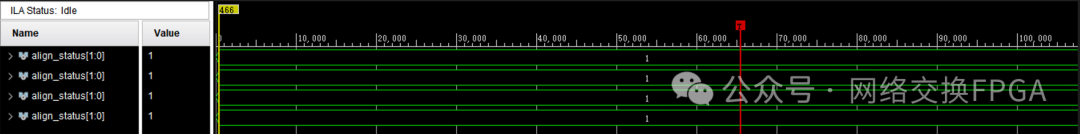

下圖為A芯片40G接口的實(shí)測(cè)截圖。alian_status應(yīng)始終保持2’b1,不穩(wěn)定說(shuō)明信號(hào)質(zhì)量太差。

FPGA連接網(wǎng)絡(luò)測(cè)試儀,正常鏈路情況下的截圖。

B、四通道各自鎖定

監(jiān)測(cè)信號(hào)

/i_RX_TOP/i_RX_CORE/i_RX_LANE0/i_AFINDER_0/word_synced

/i_RX_TOP/i_RX_CORE/i_RX_LANE0/i_AFINDER_1/word_synced

/i_RX_TOP/i_RX_CORE/i_RX_LANE1/i_AFINDER_0/word_synced

/i_RX_TOP/i_RX_CORE/i_RX_LANE1/i_AFINDER_1/word_synced

正常情況下恒為1

0表示復(fù)位或鎖定失敗

C、四通道實(shí)現(xiàn)對(duì)齊

監(jiān)測(cè)信號(hào)

/i_RX_CORE/i_RX_DESTRIPER/i_RX_LANE_ALIGNER/aligned

正常情況下恒為1

0表示復(fù)位或?qū)R失敗

B芯片40G接口芯片測(cè)試時(shí),四通道的align_status和word_synced信號(hào)一直保持為1,說(shuō)明同步頭鎖定和四通道各自鎖定沒(méi)有問(wèn)題,但是aligned信號(hào)沒(méi)有拉高過(guò),說(shuō)明四個(gè)通道沒(méi)有實(shí)現(xiàn)過(guò)對(duì)齊。

繼續(xù)抓取四通道對(duì)齊的前一級(jí)模塊(四個(gè)緩存模塊)的相關(guān)信號(hào),發(fā)現(xiàn)四個(gè)通道彼此間的數(shù)據(jù)延時(shí)差異過(guò)大,通常一個(gè)通道的數(shù)據(jù)緩存FIFO溢出時(shí),其余通道仍然沒(méi)有數(shù)據(jù)進(jìn)入緩存模塊,導(dǎo)致下一步通道間對(duì)齊無(wú)法進(jìn)行。

后續(xù)發(fā)現(xiàn)PCS的模式配置寄存器有誤,默認(rèn)情況下為10GBASE-CX4,將PCS正確配置為40GBASE-CR4后對(duì)齊標(biāo)志可以成功拉高且保持穩(wěn)定。

前面的四通道數(shù)據(jù)延時(shí)差異過(guò)大也是因?yàn)檫@種配置模式下對(duì)端單lane 3.125Gbps的數(shù)據(jù)在FPGA側(cè)單lane 10.3125Gbps的數(shù)據(jù)通道上傳輸導(dǎo)致的。

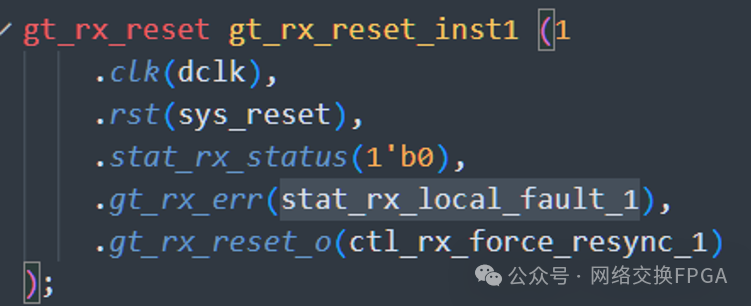

另外,如果FPGA自身四通道就沒(méi)有對(duì)齊,那大概率也是由于復(fù)位沒(méi)有做好,或者是復(fù)位的順序和復(fù)位時(shí)間,以及代碼中看門(mén)狗方式復(fù)位代碼有問(wèn)題。

擴(kuò)展:FPGA版本10Gbps以上速率以太網(wǎng)光口熱插拔問(wèn)題。

在較復(fù)雜的測(cè)試環(huán)境下,即交換機(jī)光口始終有分組進(jìn)入時(shí),對(duì)交換機(jī)進(jìn)行上下電或進(jìn)行光口拔插,會(huì)導(dǎo)致交換機(jī)的40G MAC IP核會(huì)出現(xiàn)卡死和輸出錯(cuò)幀的現(xiàn)象,若沒(méi)有錯(cuò)幀過(guò)濾模塊,錯(cuò)幀可能會(huì)導(dǎo)致交換機(jī)可編程解析器模塊不能正常工作,也可能會(huì)導(dǎo)致地址學(xué)習(xí)表短時(shí)間內(nèi)學(xué)習(xí)到大量的錯(cuò)誤的MAC地址和端口號(hào),因此,需要“看門(mén)狗系統(tǒng)”主動(dòng)復(fù)位交換機(jī)出錯(cuò)的40G IP的MAC和GT,以及過(guò)濾MAC給出的錯(cuò)幀(利用rx_user信號(hào))。

a、rx側(cè)的時(shí)鐘需要恢復(fù)訓(xùn)練,在連接上光纖后,tx數(shù)據(jù)中帶有時(shí)鐘信息,rx接收到tx的時(shí)鐘信息后,需要從高速串行流中恢復(fù)時(shí)鐘(鎖相環(huán)穩(wěn)定時(shí)鐘),待時(shí)鐘穩(wěn)定后才能正常傳輸數(shù)據(jù)。

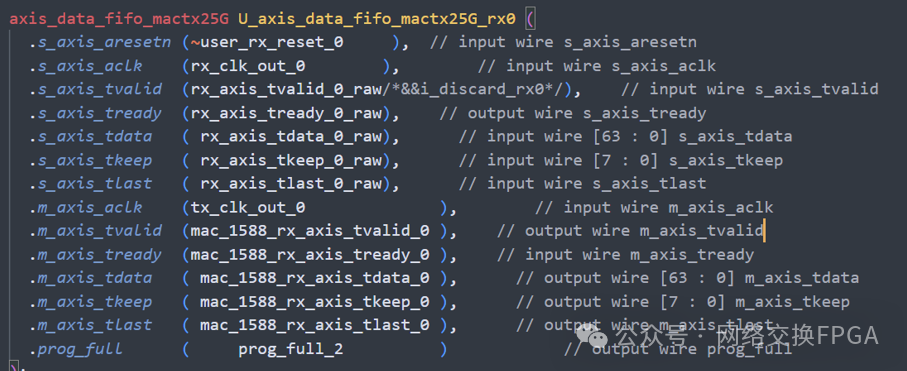

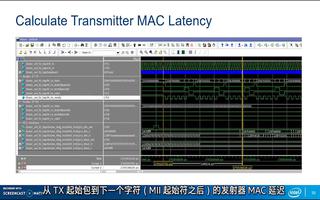

基于10G源碼作者Alex(著名開(kāi)源項(xiàng)目Corundum網(wǎng)卡的作者)的代碼,我們?cè)趓x側(cè)出來(lái)的axi data接異步時(shí)鐘fifo,輸入用rx時(shí)鐘,輸出用tx時(shí)鐘。因?yàn)閠x時(shí)鐘由本地晶振給出,保持穩(wěn)定,不需要訓(xùn)練,如下圖。

b、環(huán)境比較差的時(shí)候,做光口拔插實(shí)驗(yàn),會(huì)有l(wèi)ink狀態(tài)的問(wèn)題,link是單方向的rx link,查看手冊(cè)找到復(fù)位邏輯,做檢錯(cuò)復(fù)位,以及l(fā)ink狀態(tài)丟失的主動(dòng)復(fù)位,主動(dòng)復(fù)位時(shí)間比較長(zhǎng)持續(xù)100ms,1s內(nèi)不會(huì)重復(fù)觸發(fā)。

復(fù)位模塊如下:

在拔插的時(shí)候?qū)τ陔娐穪?lái)說(shuō)不是單純的拔插,不論是拔動(dòng)作還是插動(dòng)作link狀態(tài)都會(huì)有0-1 1-0的變化,而link狀態(tài)時(shí)斷時(shí)續(xù),在拉高時(shí)會(huì)有錯(cuò)幀進(jìn)入,需要加入錯(cuò)幀過(guò)濾邏輯(判斷rx_user信號(hào))。

c、打流過(guò)程中復(fù)位會(huì)產(chǎn)生進(jìn)入錯(cuò)幀的問(wèn)題,也就是gt側(cè)在link狀態(tài)拉高的時(shí)候,同步并不是直接正常的,剛開(kāi)始的時(shí)候會(huì)有一些內(nèi)容和長(zhǎng)度有問(wèn)題的幀,大概10幀,對(duì)于2層交換機(jī)來(lái)說(shuō)會(huì)地址自學(xué)習(xí)產(chǎn)生錯(cuò)誤的mac地址,需要在link狀態(tài)穩(wěn)定時(shí)讓幀進(jìn)入邏輯,加入端口使能。加入端口使能,不往該端口發(fā)幀和不讓該端口的幀進(jìn)交換,同時(shí)交換機(jī)有狀態(tài)信息統(tǒng)計(jì)也同步停止更新或者打開(kāi),這樣可以保護(hù)交換機(jī)內(nèi)部邏輯不會(huì)受到影響。

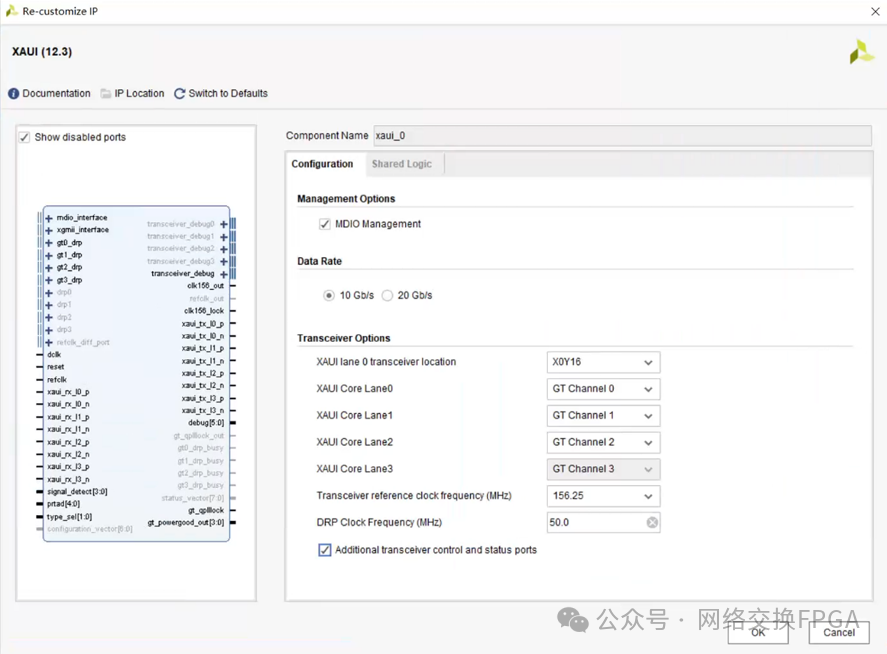

3)如果使用XAUI

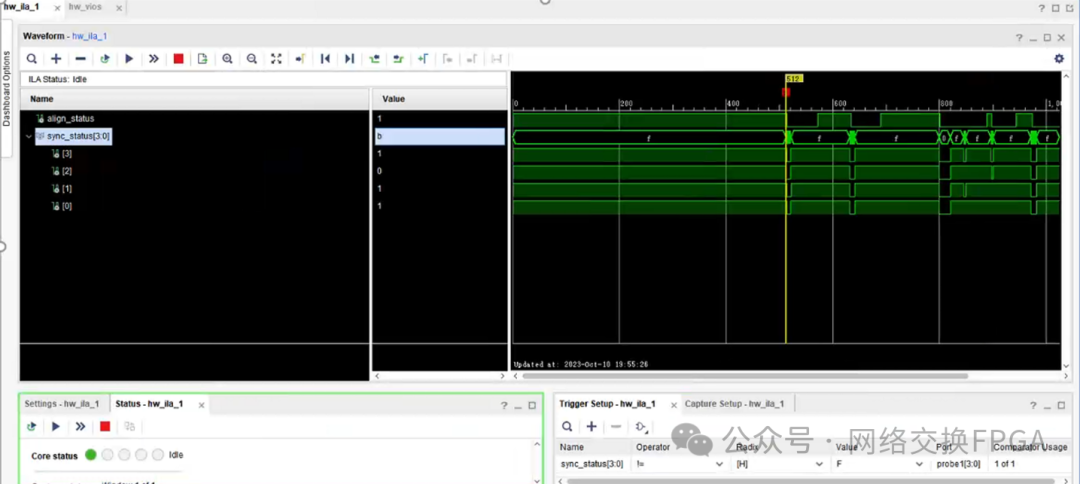

主要監(jiān)測(cè)align_status和sync_status[3:0]。

下圖為A芯片10G以太網(wǎng)接口實(shí)測(cè)截圖。

ILA顯示align_status不恒為1,sync_status不恒為F,說(shuō)明10G的鏈路也不穩(wěn)定。

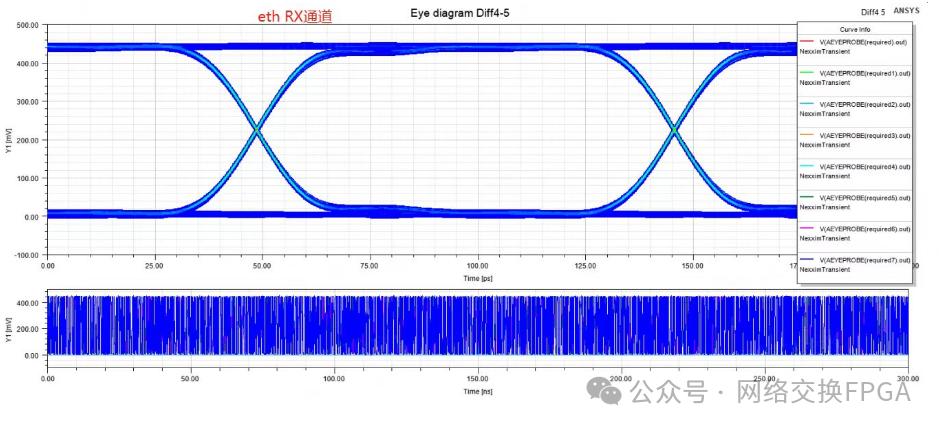

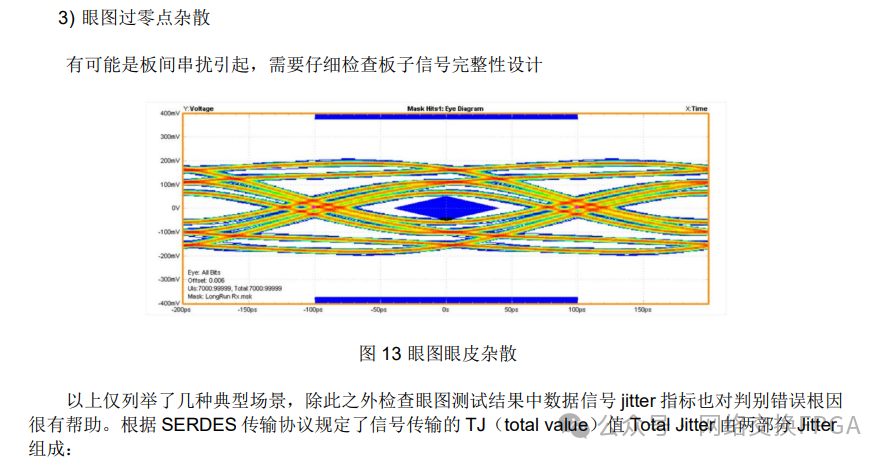

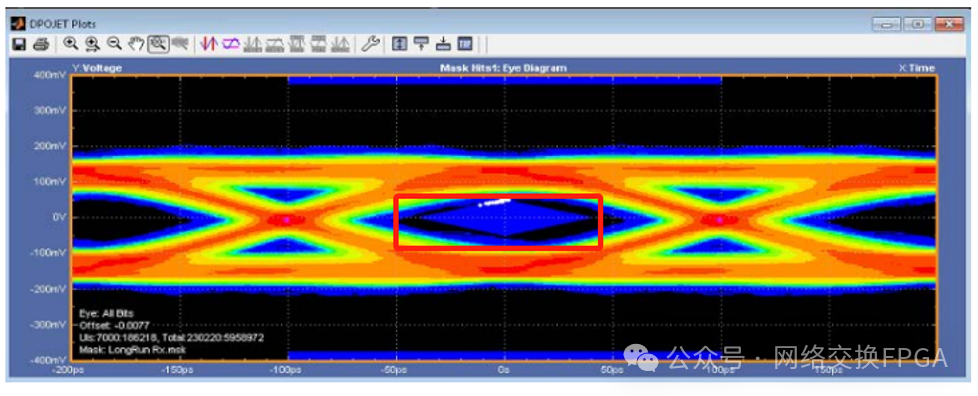

若ASIC側(cè)Serdes測(cè)試有問(wèn)題,則也可能是封裝和基板帶來(lái)的問(wèn)題。封裝時(shí)要考慮多l(xiāng)ane之間共地,die外圍共享電阻的連接方式。同時(shí),還要注意serdes時(shí)鐘是片內(nèi)還是片外,在使用片內(nèi)時(shí)鐘(on-chip clock)時(shí),需要將片外時(shí)鐘接地或者懸空。在使用片外時(shí)鐘時(shí),也需要將片內(nèi)時(shí)鐘接地或者懸空。另外,基板也需要進(jìn)行SI、PI等仿真,如果眼圖仿真結(jié)果不好,則有可能阻抗不連續(xù),過(guò)孔要考慮;還有等長(zhǎng)走線(xiàn),雖然走了等長(zhǎng),有可能兩條線(xiàn)沒(méi)有一起繞蛇形等多種可能。以下是仿真較好的情況:

通過(guò)眼圖判斷serdes的情況也很重要,如下圖:

正常情況下,圖中眼睛區(qū)域可被包住即可。除了用專(zhuān)用設(shè)備看眼圖外,一般IP供應(yīng)商會(huì)提供MATLAB或者Python的程序,可以通過(guò)讀取實(shí)際Serdes測(cè)試時(shí)對(duì)應(yīng)相關(guān)寄存器的狀態(tài),繪制出對(duì)應(yīng)的眼圖。

4、ASIC版serdes故障定位

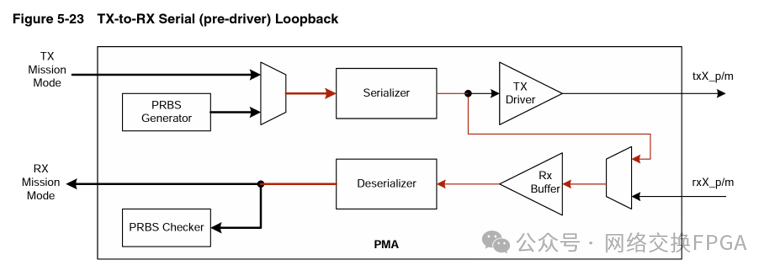

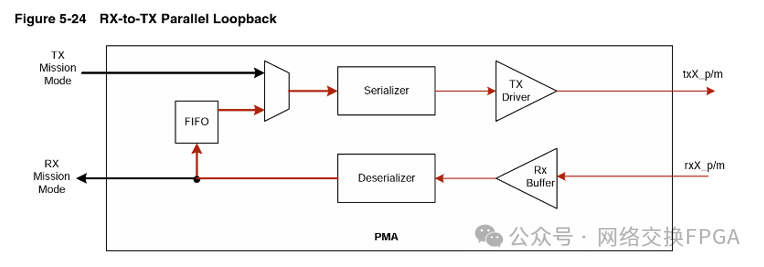

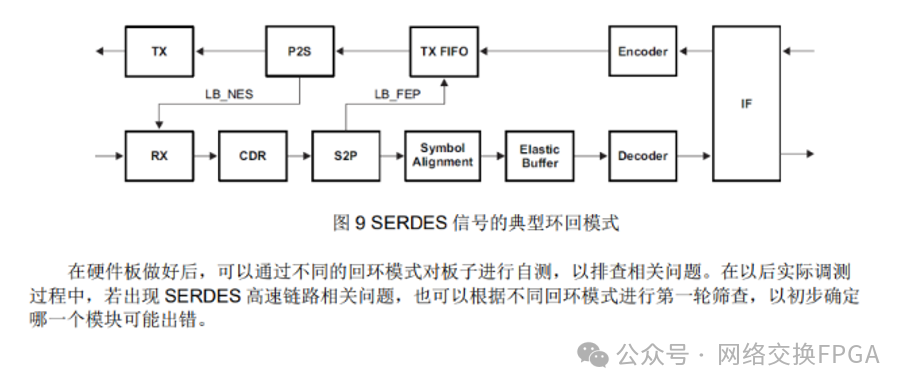

若SERDES高速鏈路存在問(wèn)題,可通過(guò)多種回環(huán)模式進(jìn)行第一輪篩查,以初步排查問(wèn)題。

主要使用兩種模式:

(1) 近端回環(huán)LB_NES模式,即測(cè)試芯片PHY的tx2rx loopback,PRBS;

(2)遠(yuǎn)端回環(huán)LB_FEP模式,即測(cè)試芯片PHY的rx2tx loopback;

若在近端回環(huán)模式下,BER值(誤碼率)較高,主要可以檢測(cè)SERDES 輸入時(shí)鐘相關(guān)設(shè)置,如果遠(yuǎn)端回環(huán)模式下 BER 值較高,則主要檢測(cè)發(fā)送端幅值,衰減設(shè)置,發(fā)送側(cè)濾波器參數(shù)設(shè)置,接收端DFE 設(shè)置,CDR 設(shè)置以及和時(shí)鐘相位偏移相關(guān)的設(shè)置。

PRBS:串行總線(xiàn)的物理層測(cè)試通常分為發(fā)射機(jī)測(cè)試和接收機(jī)測(cè)試,又稱(chēng)為 TX 測(cè)試和 RX 測(cè)試。發(fā)射機(jī)測(cè)試通常包括眼圖、抖動(dòng)、信號(hào)波形、幅度、上升下降時(shí)間等測(cè)試項(xiàng)目,接收機(jī)測(cè)試通常包括誤碼率、抖動(dòng)容限、接收機(jī)靈敏度等測(cè)試項(xiàng)目。對(duì)于眼圖測(cè)試、誤碼率和抖動(dòng)容限測(cè)試,最常用的測(cè)試碼是 PRBS,主要有 PRBS7、PRBS15、PRBS23 和 PRBS31。

PRBS7 是目前 10Gbps 以下的串行總線(xiàn)中最常用的測(cè)試碼型,在 ITU-TV.29 規(guī)范中規(guī)定。PRBS7 屬于短偽隨機(jī)碼型,與 8b10b NRZ 編碼的數(shù)據(jù)流很相似,所以,在 PCIe、SATA、XAUI、1000BASE-LX、FC、SAS 等采用 8b10b 編碼的串行總線(xiàn)中,PRBS7 是最常用的測(cè)試碼型,支持這些總線(xiàn)的芯片通常都可以輸出 PRBS7 測(cè)試碼型,用于眼圖、抖動(dòng)或誤碼率測(cè)量。PRBS31是一種較長(zhǎng)的偽隨機(jī)碼型,其多項(xiàng)式為X31+X28+1,碼長(zhǎng)為2^31-1個(gè)比特。PRBS31的碼流中最長(zhǎng)的連1為31個(gè),最長(zhǎng)的連0為30個(gè),包含了相當(dāng)多的低頻成分,因此適用于像SONET/SDH信號(hào)那樣包含了很多低頻成分的物理層測(cè)量。PRBS31也是10 Gigabit Ethernet推薦的測(cè)試碼型之一。

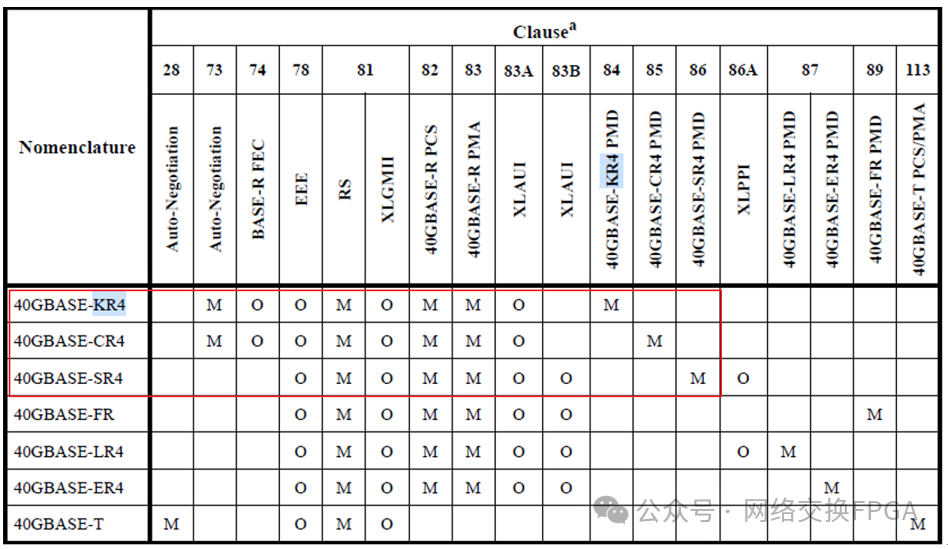

KR:背板傳輸;CR:銅線(xiàn)互聯(lián);SR:短距光纖傳輸。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22033瀏覽量

617753 -

SerDes

+關(guān)注

關(guān)注

7文章

217瀏覽量

35769 -

以太網(wǎng)接口芯片

+關(guān)注

關(guān)注

0文章

38瀏覽量

6770

原文標(biāo)題:使用FPGA對(duì)40G以太網(wǎng)接口芯片Serdes進(jìn)行測(cè)試的方法

文章出處:【微信號(hào):HXSLH1010101010,微信公眾號(hào):FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

基于FPGA的以太網(wǎng)ARP通信測(cè)試(二)

基于FPGA的萬(wàn)兆以太網(wǎng)接口的設(shè)計(jì)與實(shí)現(xiàn)

40G QSFP+光模塊的完美鏈接-Cisco Nexus 6004交換機(jī)

解密易飛揚(yáng)40G QSFP+ PSM4光模塊

基于FPGA的10G以太網(wǎng)光接口設(shè)計(jì)

40G光模塊選購(gòu)指南

超遠(yuǎn)程40G以太網(wǎng)子系統(tǒng)的遠(yuǎn)端回路問(wèn)題如何解決

Serdes到Serdes 10G以太網(wǎng)連接是T2080上的一個(gè)功能選項(xiàng),通過(guò)光纖或跨背板時(shí)會(huì)失敗的原因?

基于FPGA的萬(wàn)兆以太網(wǎng)接口設(shè)計(jì)

基于FPGA的萬(wàn)兆以太網(wǎng)接口的設(shè)計(jì)與實(shí)現(xiàn)

分析25G以太網(wǎng)架構(gòu)能否取代40G

部署40G以太網(wǎng)時(shí)要考慮哪些因素?

詳解FPGA的10G以太網(wǎng)接口調(diào)試

40G以太網(wǎng)光模塊解決方案

使用FPGA對(duì)40G以太網(wǎng)接口芯片Serdes進(jìn)行測(cè)試的方法

使用FPGA對(duì)40G以太網(wǎng)接口芯片Serdes進(jìn)行測(cè)試的方法

評(píng)論