捷多邦小編結(jié)合多年行業(yè)經(jīng)驗(yàn),總結(jié)出工程師在設(shè)計(jì)PCB時(shí)最容易忽視的五大問題,助你提前避坑,高效完成設(shè)計(jì)!

錯(cuò)誤一:忽視布局規(guī)劃,導(dǎo)致信號(hào)干擾

忽略了對(duì)關(guān)鍵元件的合理布局。例如,將高頻信號(hào)模塊靠近模擬電路、電源模塊隨意擺放等,都會(huì)引發(fā)信號(hào)串?dāng)_或電磁干擾(EMI)。

避坑建議:

分區(qū)布局:按功能劃分區(qū)域(如電源區(qū)、數(shù)字區(qū)、模擬區(qū)),并預(yù)留隔離帶。

關(guān)鍵信號(hào)優(yōu)先:優(yōu)先布置高頻信號(hào)線、時(shí)鐘線,盡量縮短走線路徑。

避免“跨區(qū)干擾”:敏感元件(如傳感器)遠(yuǎn)離大電流或發(fā)熱器件。

錯(cuò)誤二:電源設(shè)計(jì)“偷工減料”

因追求緊湊布局而簡化電源設(shè)計(jì),例如忽略去耦電容、地線設(shè)計(jì)不合理等,導(dǎo)致系統(tǒng)供電不穩(wěn)或噪聲超標(biāo)。

避坑建議:

添加足夠的去耦電容:在電源入口和芯片供電腳附近布置不同容值的電容。

采用星型接地:避免地線環(huán)路,降低共模干擾。

電源線寬計(jì)算:根據(jù)電流大小計(jì)算銅箔寬度,避免過熱或壓降過大。

錯(cuò)誤三:盲目追求“最小化”,忽略可制造性

為了節(jié)省成本,工程師可能將焊盤尺寸、線距線寬設(shè)計(jì)得過于極限,卻未考慮生產(chǎn)工藝的容差,導(dǎo)致批量生產(chǎn)時(shí)良率暴跌。

避坑建議:

遵循DFM規(guī)則:

預(yù)留安全間距:元件與板邊、過孔與走線之間保留足夠余量。

標(biāo)注特殊要求:如阻抗控制、沉金工藝等,需在設(shè)計(jì)文件中明確標(biāo)出。

錯(cuò)誤四:散熱設(shè)計(jì)“后知后覺”

高功耗元件(如CPU、電源芯片)的散熱問題常被低估,僅通過增加散熱孔或敷銅處理,可能導(dǎo)致設(shè)備長期運(yùn)行不穩(wěn)定。

避坑建議:

早期規(guī)劃散熱路徑:在布局階段預(yù)留散熱片位置或風(fēng)扇安裝空間。

合理利用敷銅:對(duì)發(fā)熱元件所在層進(jìn)行局部敷銅,并通過多過孔連接至內(nèi)層散熱區(qū)。

模擬驗(yàn)證:使用熱仿真工具提前分析溫度分布。

錯(cuò)誤五:跳過設(shè)計(jì)驗(yàn)證,直接投產(chǎn)

未充分進(jìn)行電氣規(guī)則檢查(DRC)、信號(hào)完整性仿真或?qū)嵨餃y試,可能埋下隱性故障。

避坑建議:

利用EDA工具自查:徹底執(zhí)行DRC和ERC檢查,修復(fù)開路、短路等基礎(chǔ)錯(cuò)誤。

小批量試產(chǎn):通過捷多邦的“24小時(shí)加急打樣”服務(wù)快速驗(yàn)證設(shè)計(jì),測試實(shí)際功能。

極端環(huán)境測試:在高低溫、振動(dòng)等條件下評(píng)估PCB的可靠性。

審核編輯 黃宇

-

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

396文章

4793瀏覽量

90085 -

PCB

+關(guān)注

關(guān)注

1文章

2090瀏覽量

13204

發(fā)布評(píng)論請先 登錄

電商API的五大應(yīng)用場景:解鎖增長新機(jī)遇

原理圖和PCB設(shè)計(jì)中的常見錯(cuò)誤

DDR模塊的PCB設(shè)計(jì)要點(diǎn)

PCB設(shè)計(jì)中容易遇到的問題

PCB設(shè)計(jì)常見問題有哪些

如何在PCB中選擇平衡成本與性能?

不可忽視!四層PCB打樣設(shè)計(jì)中的關(guān)鍵細(xì)節(jié)大盤點(diǎn)!

不可忽視!PCB設(shè)計(jì)中線寬的“微”妙之處

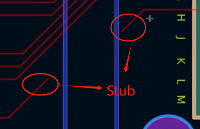

PCB設(shè)計(jì)中的Stub對(duì)信號(hào)傳輸?shù)挠绊?/a>

PCB設(shè)計(jì)時(shí)別忽視,這11個(gè)細(xì)節(jié)!

PCB設(shè)計(jì)中常見的DFM問題

高速PCB設(shè)計(jì)指南

省成本還是增風(fēng)險(xiǎn)?PCB設(shè)計(jì)中不能忽視的五大細(xì)節(jié)?

省成本還是增風(fēng)險(xiǎn)?PCB設(shè)計(jì)中不能忽視的五大細(xì)節(jié)?

評(píng)論