本文實現的CPU是一個五級流水線的精簡版CPU(也叫PCPU,即pipeline),包括IF(取指令)、ID(解碼)、EX(執行)、MEM(內存操作)、WB(回寫)。

指令集:RISC

指令集大小:2^5 = 32

數據寬度:16bit

數據內存:2^8×16bit = 256個16bit

指令內存:2^8×16bit = 256個16bit

通用寄存器:8×16bit

標志寄存器:NF(negative flag)、ZF(zero flag)、CF(carry flag)

控制信號:clock、reset、enable、start

1.介紹與設計

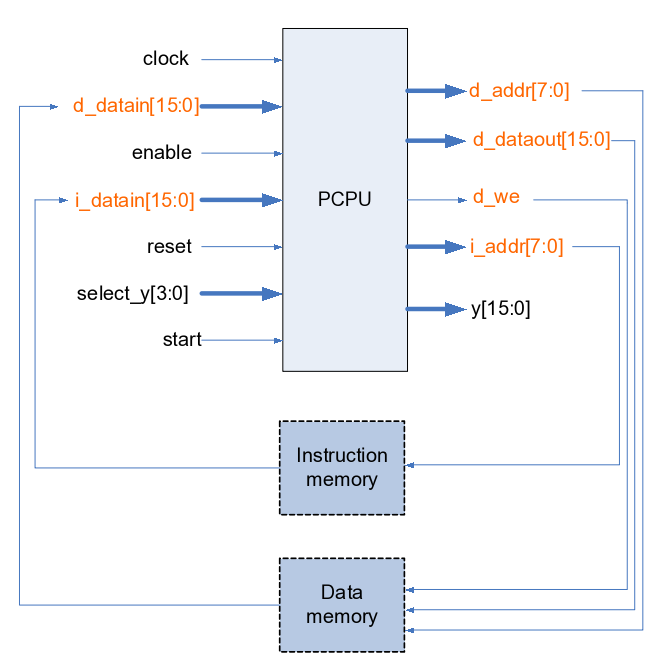

1.1.CPU頂層視圖

第一步只要求實現簡單的五級流水線,不要求實現指令內存、數據內存模塊,因此CPU內部與內存有關的信號都簡化為輸入輸出信號了,CPU的頂層視圖看起來應該如下圖,其中select_y、y信號是跟CPU板級測試有關的,這一步暫且沒用到。

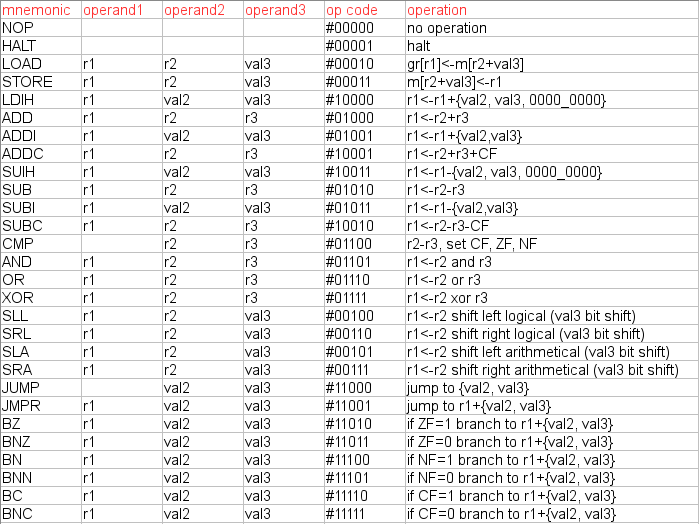

1.2.指令集

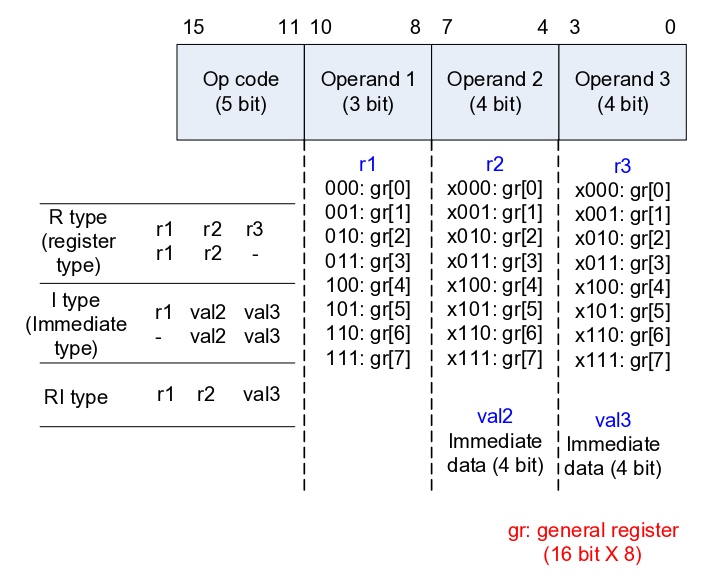

指令為三地址格式,操作碼長度5bit,根據操作數的不同可以把指令分為三種類型,即寄存器類型R type、立即數類型I type、混合類型RI type,不過后面在代碼編寫的時候,為了方便,會依據其它標準進行劃分。

規范一下表示方式,r1或者gr[r1]表示訪問寄存器r1,m[r2+val3]表示訪問r2+val3這個地址,{val2,val3}表示立即數訪問,val2為MSB,val3為LSB。

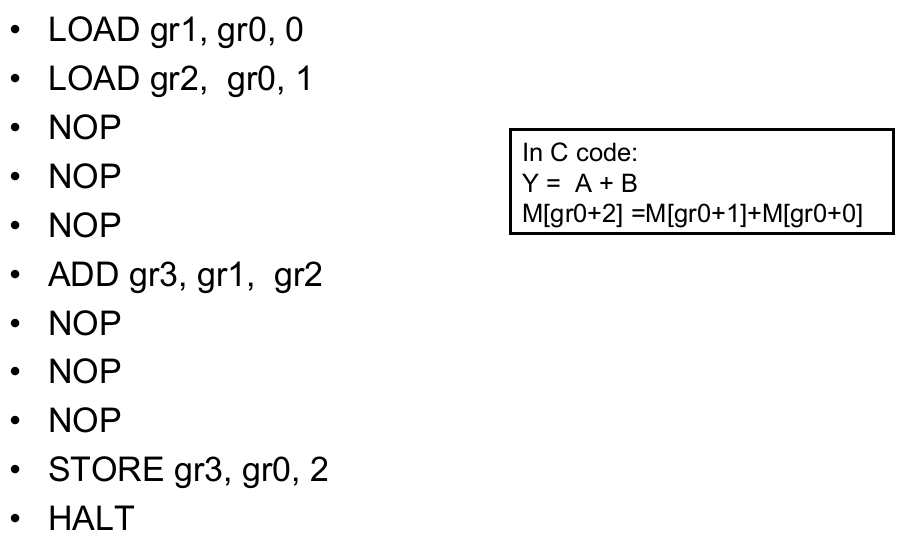

匯編代碼示例:

本文設計一共實現了28條機器指令,剩下未用的4個操作碼(10100,10101,10110,10111)可自行補充為其它操作,比如自增INC、自減DEC。這里指令的編碼是比較隨意的,而且由于代碼實現中使用了宏定義,因此可以任意更改指令的編碼,不過如果想做進一步的優化,就要仔細考慮編碼方式了。以下是指令集的具體格式與操作,設計CPU的時候有兩張圖是必須時刻看著的,我都把它們打印出來,這是其中一張。

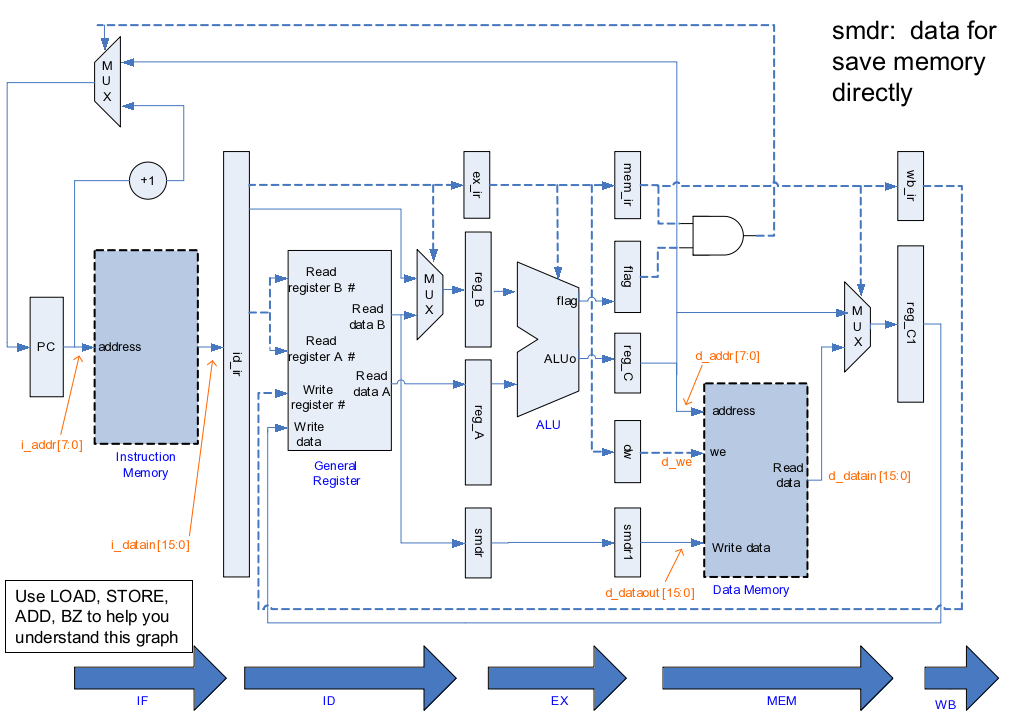

1.3.五級流水線

除了指令集之外,設計CPU最重要的就是下面這張CPU塊級電路圖,五級流水線的代碼實現都必須依賴于這張圖,因此必須理解圖中每一步的作用。

圖中所有矩形框標出來的都是CPU內部的寄存器,整個電路圖展示了CPU內部指令以及數據的流動方向。每到時鐘上升沿,上一級流水線的寄存器的數據就會經過中間的組合邏輯電路流動到下一級流水線的寄存器,因此,5個時鐘周期之后一條機器指令便執行完畢了。

簡單描述一條指令的執行過程就是,

●首先根據PC的值到內存中取一條指令,

●解碼指令提取兩個操作數

●進行運算,

●根據指令功能以及運算結果決定是否訪問數據內存以及如何訪問,

●最后同樣根據指令功能決定是否要進行回寫操作,即修改寄存器的值。

下面將分別講解CPU控制以及五級流水線每一級的行為,為了簡單起見,這里僅考慮NOP、HALT、LOAD、STORE、ADD、CMP、BZ、BN這幾條指令,明白了流水線的行為之后再加上其它的指令也是一樣的道理

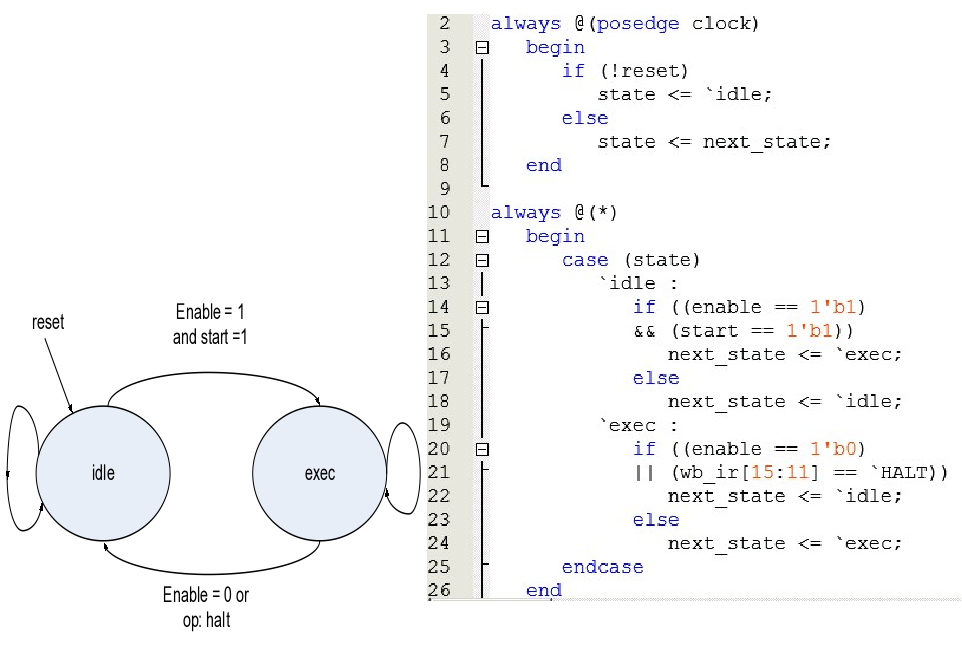

1.4.CPU控制

CPU控制自然是基于狀態機,只有兩個狀態idle和exec,CPU在idle狀態下只有enable、start同時使能才會進入exec狀態。

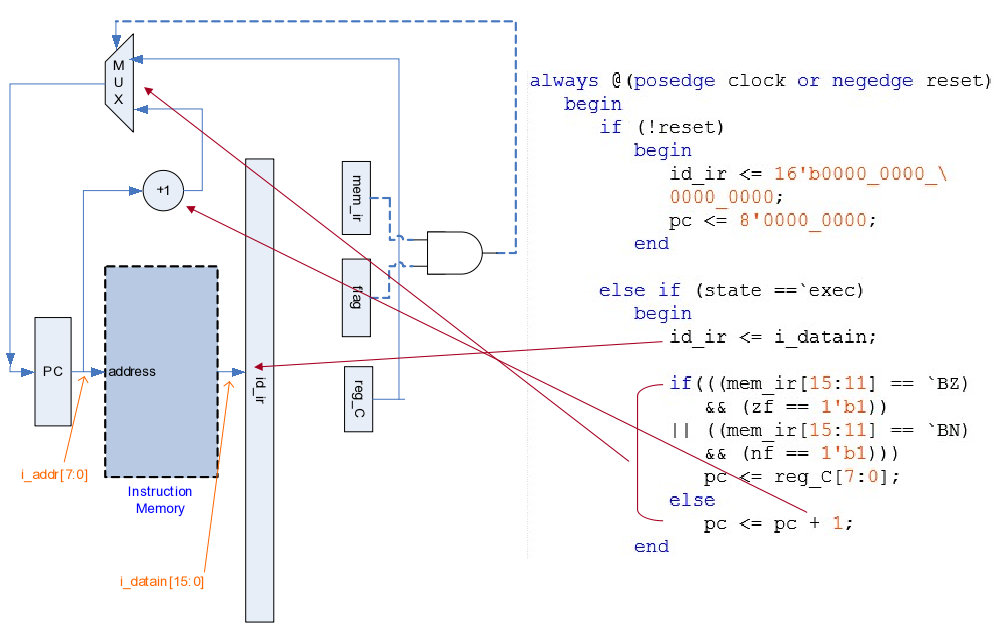

1.5.IF

IF階段的任務就是要根據PC的值從指令內存中讀取一條指令,并且設置下一周期PC的值(指令可以順序執行,也可以跳轉到某個特定的地址)。因為讀取內存是內存模塊實現的功能,因此這里CPU只需要給出指令地址i_addr就能得到對應的指令i_datain。

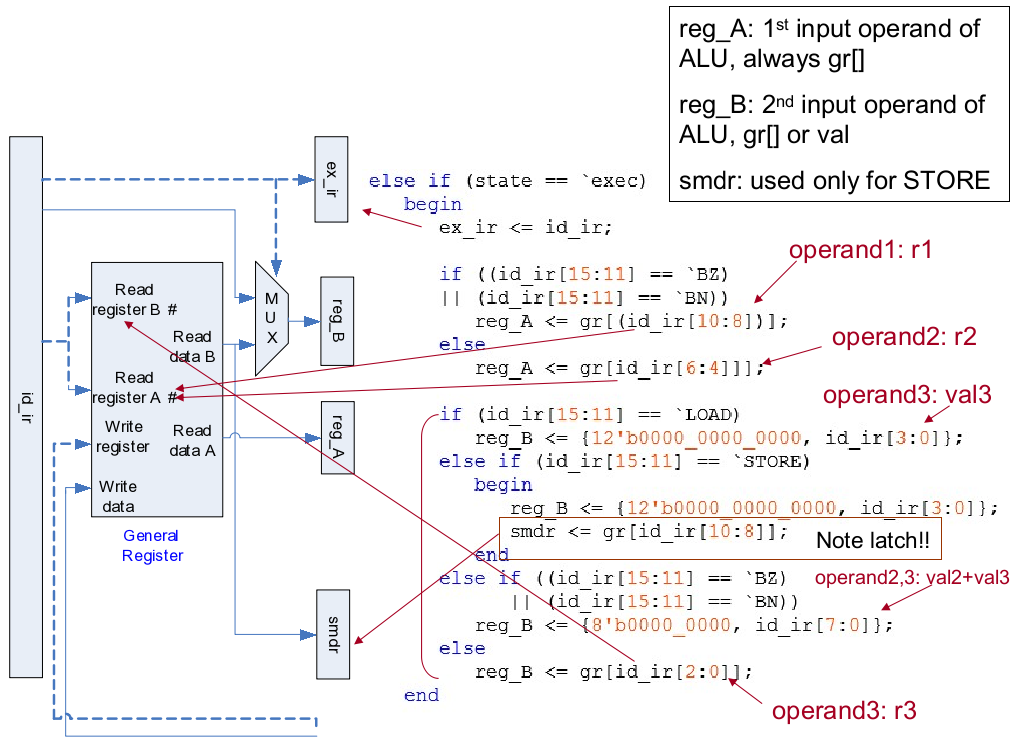

1.6.ID

ID階段要根據指令的功能(即操作碼)從指令中提取對應的操作數,操作數可能來自通用寄存器r0-r7,也可能是立即數。另外如果指令是STORE指令,也要準備好要存儲到內存中的數據。

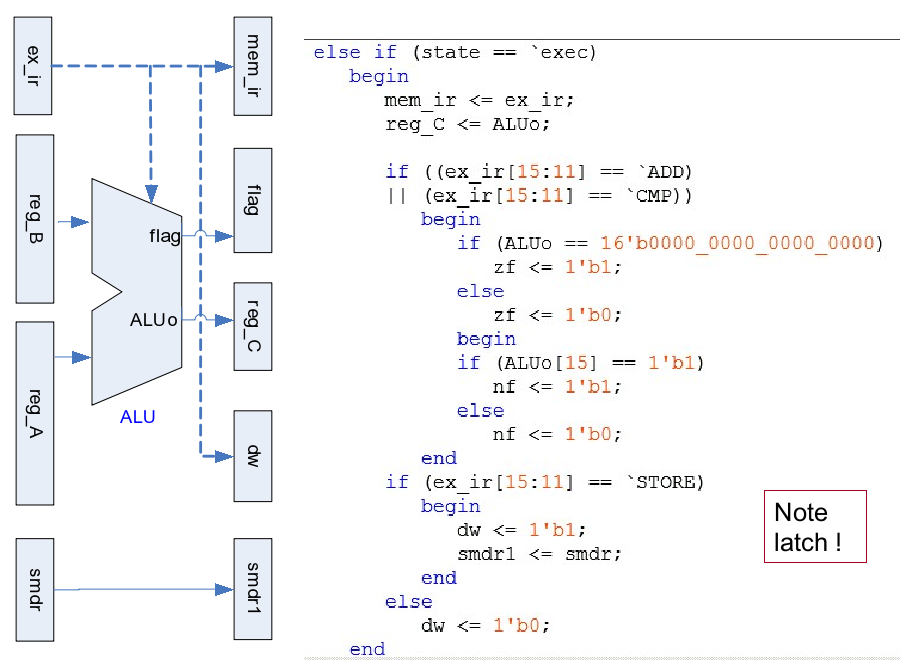

1.7.EX

EX階段執行的是ALU運算和標志寄存器設置,另外如果是STORE指令也要給出內存寫的使能信號dw以及將要寫到內存中的數據smdr1。

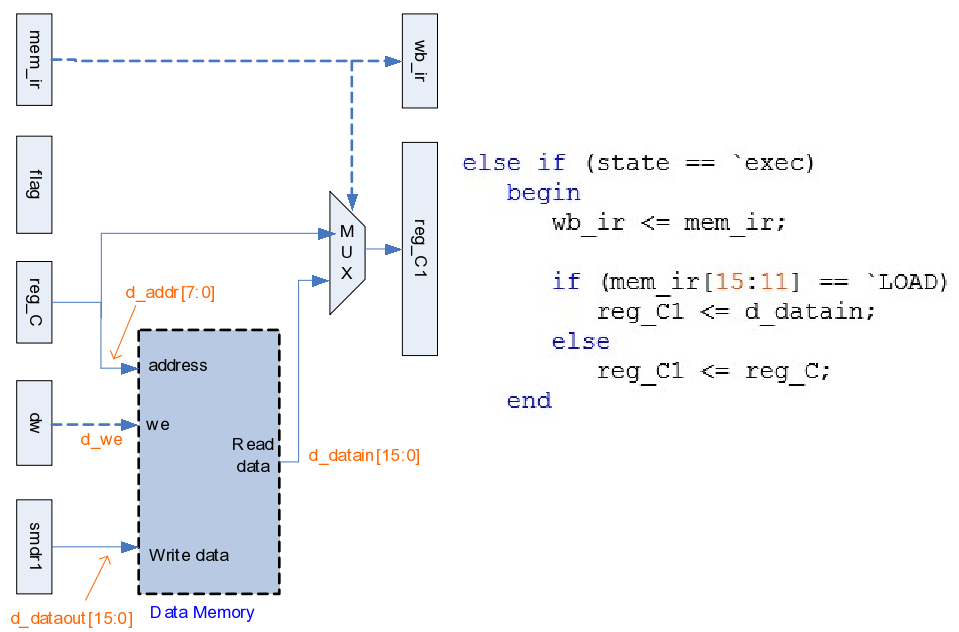

1.8.MEM

MEM階段要根據指令功能和上一階段的運算結果(內存操作的時候作為內存地址)決定是否要訪問內存以及如何訪問,只對需要內存操作的指令有效。

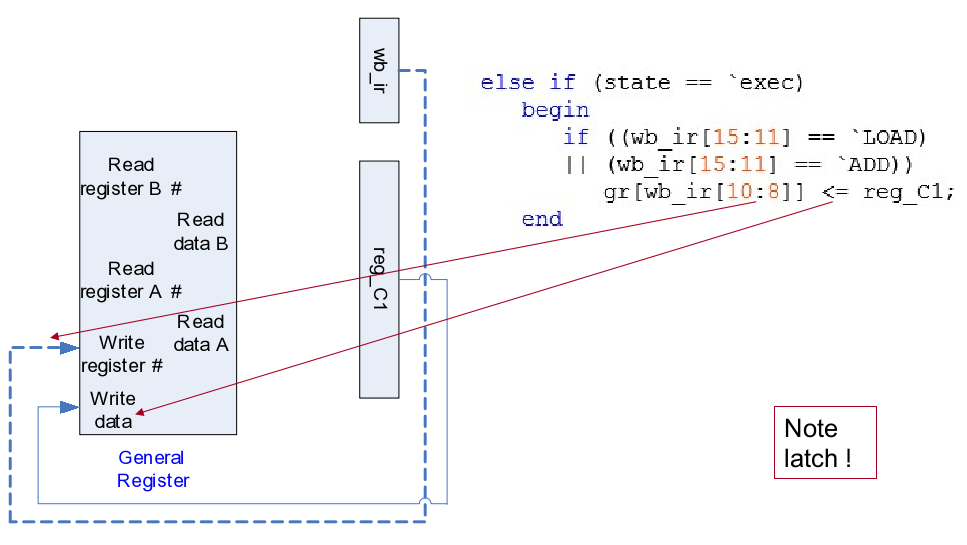

1.9.WB

WB階段同樣根據指令的功能以及上一階段的結果決定是否要修改寄存器的值以及如何修改,只對需要修改寄存器值的指令有效。

CPU仿真(通過內存實現)

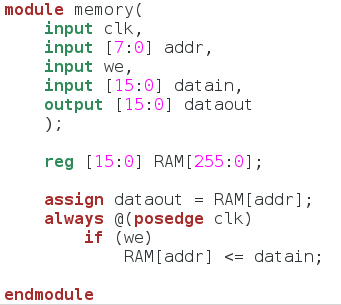

內存其實就是一個 reg 數組,讀內存用組合邏輯電路,寫內存用時序電路,如下圖代碼所示。對內存的初始化可以通過 reset 信號,或者軟件仿真的時候可以直接在 test bench 文件的 initial 里面初始化。

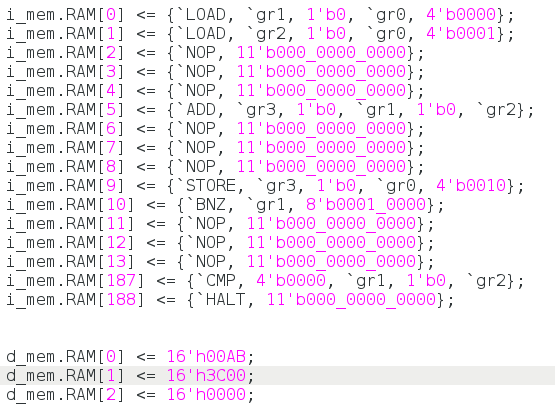

這時候,pcpu的測試文件就要另外再通過memory.v實例化兩個內存模塊i_mem、d_mem分別用作指令內存和數據內存了,pcpu模塊與內存有關的所有信號(i_datain、d_datain等等)都要連接到這兩個模塊。initial初始化內存的方式如下圖:

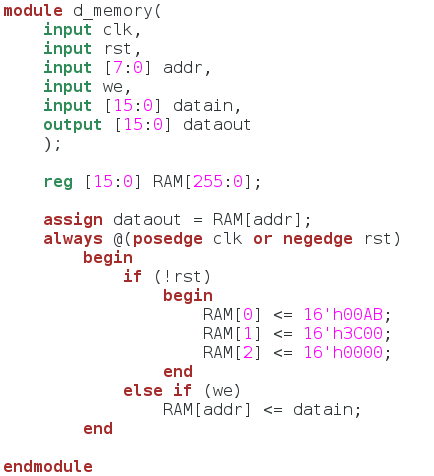

另外一種reset信號初始化內存的方式需要分開定義指令內存i_memory.v和數據內存d_memory.v,然后在pcpu的測試文件里面實例化這兩個文件的模塊。d_memory.v大致如下

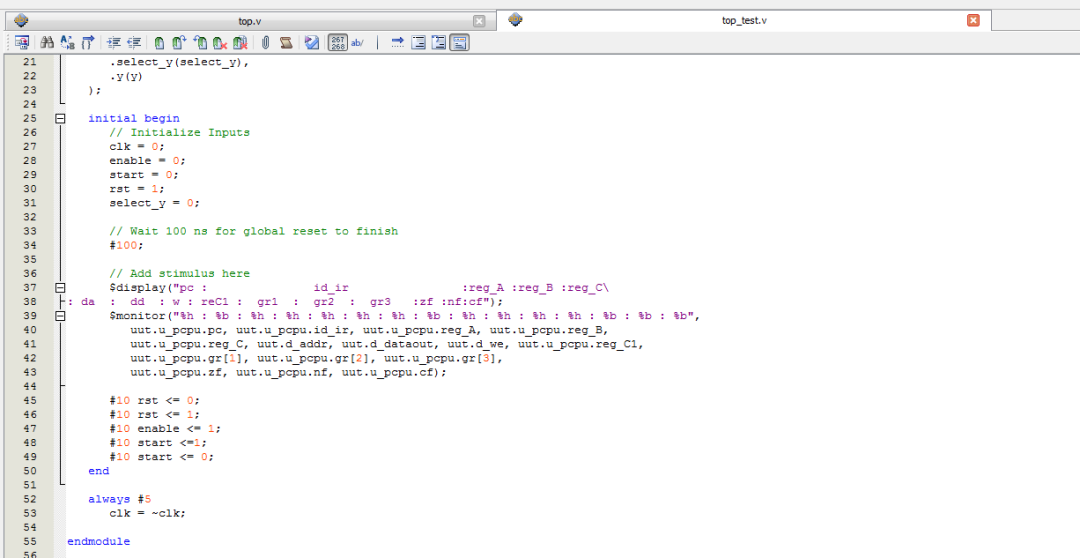

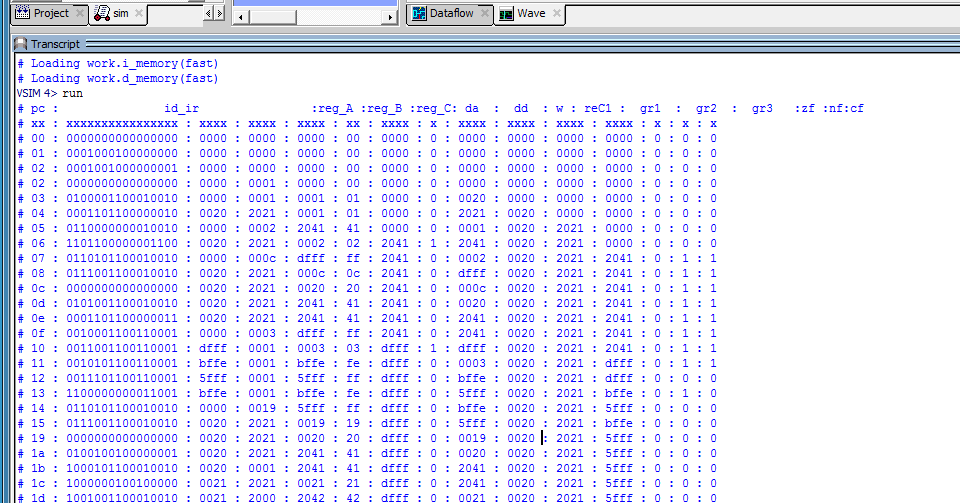

Testbench:

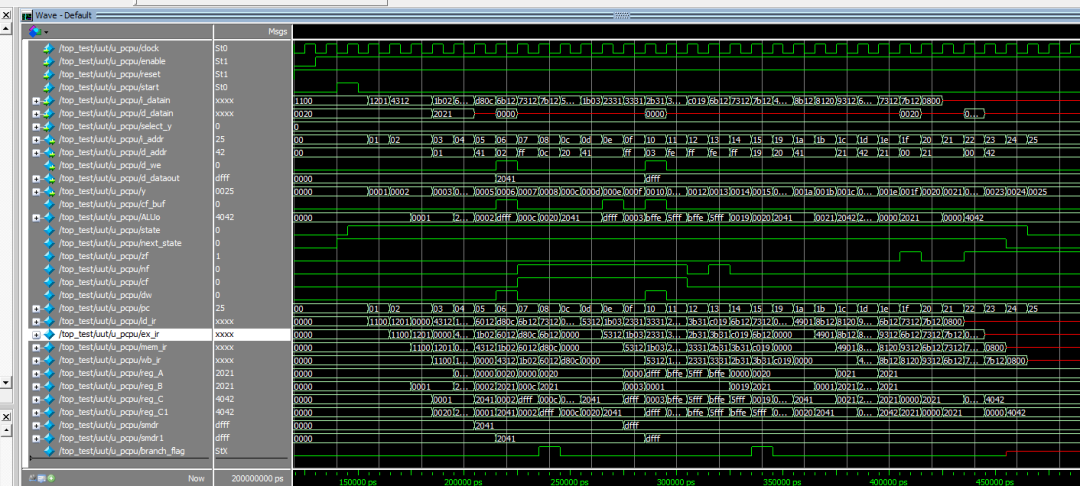

仿真圖

原文連接:https://tencentcloud.csdn.net/678a0cacedd0904849a6618d.html

-

寄存器

+關注

關注

31文章

5433瀏覽量

124256 -

cpu

+關注

關注

68文章

11073瀏覽量

216825 -

內存

+關注

關注

8文章

3119瀏覽量

75204 -

五級流水線

+關注

關注

0文章

2瀏覽量

1571

原文標題:RISC_v五級流水線CPU設計

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

RISC-V五級流水線CPU設計

RISC-V五級流水線CPU設計

評論