概述

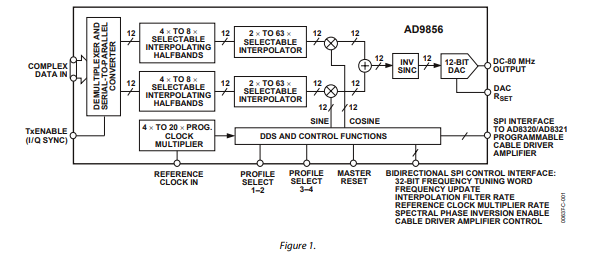

AD9856在單芯片上集成了一個高速直接數字頻率合成器(DDS)、一個高性能、高速12位數模轉換器(DAC)、時鐘乘法器電路、數字濾波器以及其它DSP功能,構成一個完整的正交數字上變頻器。它主要用作通用上行與下行I/Q調制器,適合視成本、尺寸、功耗和動態性能為關鍵因素的交互式HFC電纜網絡應用。

數據表:*附件:AD9856 CMOS 200MHz正交數字上變頻器技術手冊.pdf

特性

- 通用低成本調制器解決方案,適合通信應用

- 輸出帶寬:DC至80 MHz

- 集成12位數模轉換器

- 可編程采樣速率插值濾波器

- 可編程基準時鐘乘法器

- SIN(x)/x內部補償濾波器

- 無雜散動態范圍(SFDR):大于52 dB (40 MHz AOUT)

- +3 V單電源供電

- 無雜散動態范圍(SFDR):大于48 dB (70 MHz AOUT)

- 窄帶無雜散動態范圍(SFDR):大于80 dB (70 MHz AOUT)

- 節省空間的表面貼裝封裝

- 雙向控制總線接口

框圖

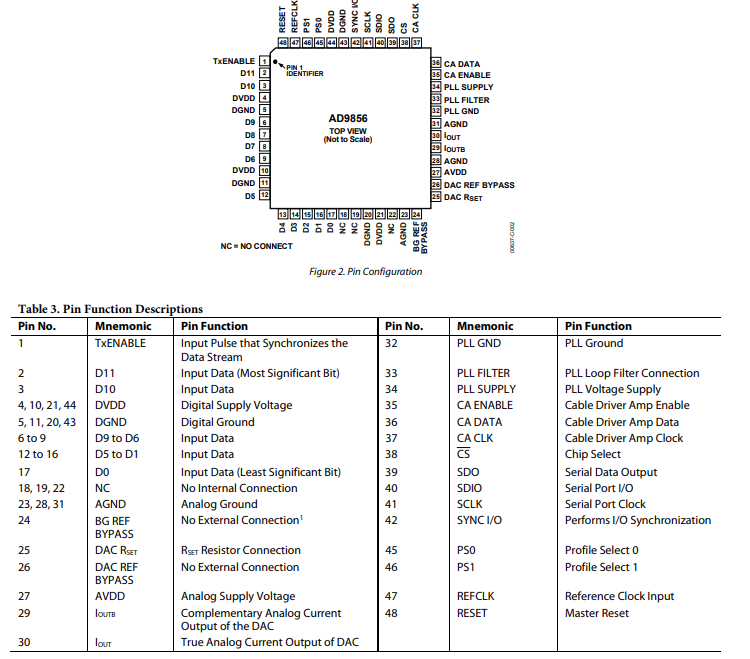

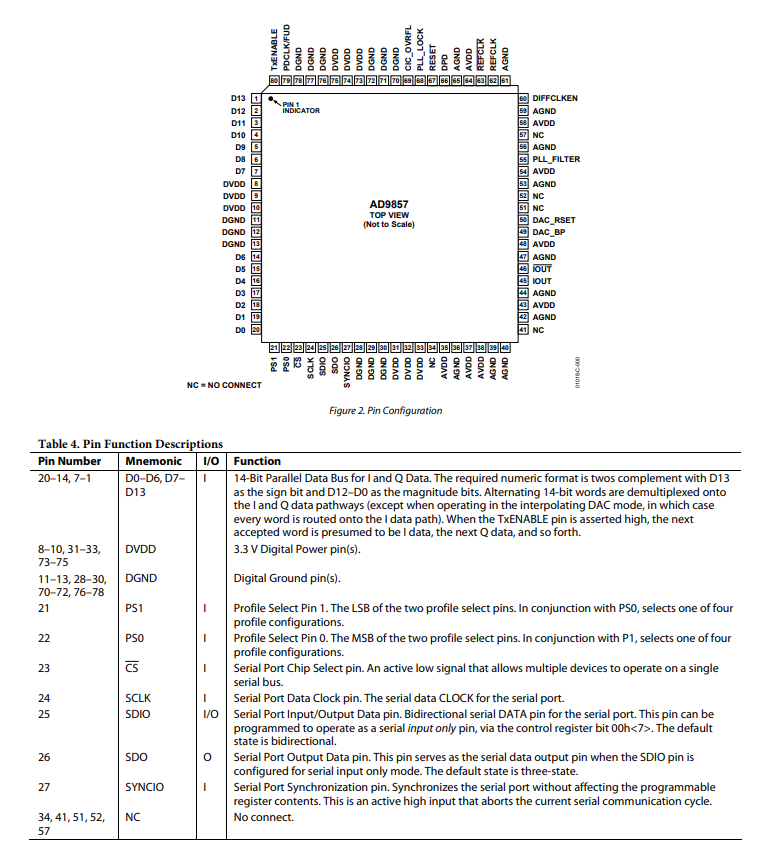

引腳配置描述

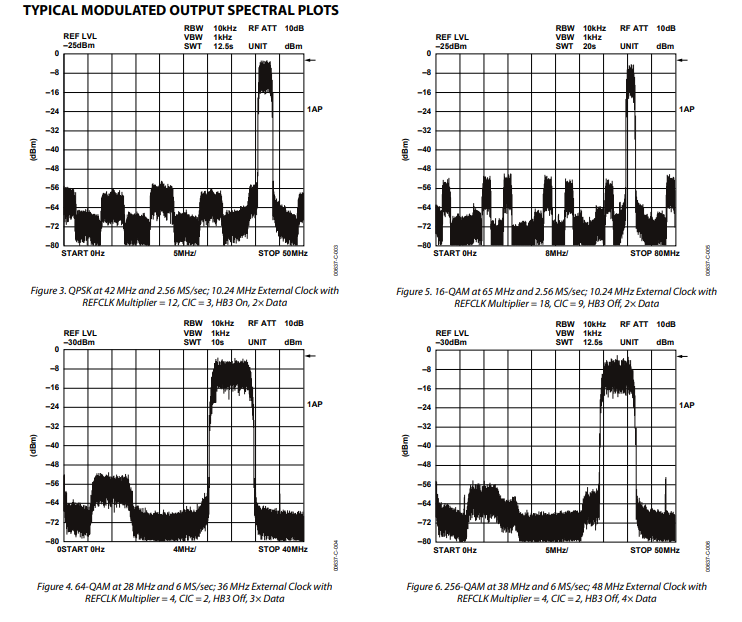

典型性能特征

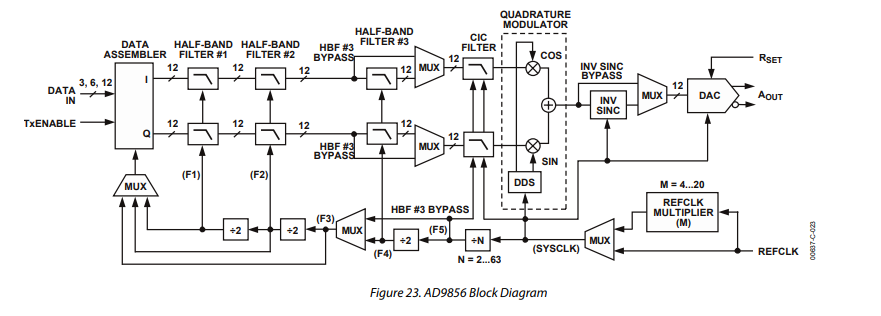

為了大致了解AD9856的功能,參考圖23(該器件架構框圖)會有所幫助。以下是對該器件功能的一般性描述。后續章節將詳細介紹各個數據路徑構建模塊。

調制模式操作

AD9856接收12位數據字,這些數據字通過內部時鐘選通進入數據匯編器。輸入引腳TxENABLE起到閥門的作用,可根據數據匯編器的狀態決定接受或忽略數據。用戶可以選擇將12位數據字作為單個12位字、雙個6位字或四個3位字輸入到AD9856中,這為用戶提供了根據需求靈活使用較少接口引腳的方式。此外,輸入到數據匯編器的交替12位字被視為符號的同相(I)和正交(Q)分量。

12位字輸入到AD9856的速率稱為輸入采樣率(f_{IN})。需注意,**f_{IN}**與基帶數據的固定速率不同。相反,用戶的基帶數據在輸入到AD9856之前至少需要進行兩倍(×2)的上采樣,以盡量減少與級聯積分梳狀(CIC)濾波器級相關的頻率相關衰減(詳見級聯積分梳狀濾波器部分)。

數據匯編器將輸入的數據字對拆分為獨立的I/Q數據流。I/Q數據字對出現在數據匯編器輸出端的速率稱為I/Q采樣率(f_{IQ})。由于兩個12位輸入數據字用于構建離散的I和Q數據路徑,所以輸入采樣率是I/Q采樣率的兩倍(即,f_{IN} = 2 × f_{IQ})。

數據匯編器的用戶可以選擇將12位數據字輸出到AD9856,其輸出采樣率為$8 × f_{IQ}$ 。

一旦通過數據匯編器,I/Q數據流會輸入到兩個半帶濾波器(半帶濾波器1和2)。這兩個濾波器的組合使采樣率提高四倍(×4)。因此,在半帶濾波器2的輸出端,采樣率為$4 × f_{IQ}** 。除了提高采樣率之外,半帶濾波器還提供低通濾波特性,這是抑制上采樣過程產生的頻譜鏡像所必需的。進一步的上采樣可通過可選的第三個半帶濾波器(半帶濾波器3)實現。啟用該濾波器時,總上采樣因子為八(×8)。因此,如果選擇半帶濾波器3,輸出采樣率為$8 × f_{IQ}** 。

通過半帶濾波器級后,I/Q數據流會輸入到級聯積分梳狀(CIC)濾波器。該濾波器配置為插值濾波器,可實現2到63(含)之間任意整數倍的進一步上采樣。與半帶濾波器類似,CIC濾波器具有低通特性,同樣用于抑制上采樣過程產生的頻譜鏡像。

CIC濾波器之后的數字正交調制器級用于將輸入數據流的基帶頻譜向上變頻到所需的載波頻率(此過程稱為上變頻)。載波頻率由直接數字合成器(DDS)進行數字控制。DDS使用其內部參考時鐘(SYSCLK)以高精度生成所需的載波頻率。載波以正交方式(90°相位偏移)應用于I和Q乘法器并求和,從而產生已調制載波的數據流。請注意,輸入數據的采樣率已從輸入采樣率**f_{IN}**轉換為SYSCLK的輸出采樣率(見圖23)。

-

dac

+關注

關注

43文章

2397瀏覽量

193357 -

DDS

+關注

關注

22文章

672瀏覽量

154250 -

上變頻器

+關注

關注

0文章

9瀏覽量

7578

發布評論請先 登錄

數字上變頻器IC調制復雜調制

數字正交上變頻器AD9857

AD9856 CMOS 200 MHz正交數字上變頻器

AD9957:內置18位I/Q數據路徑和14位DAC的1GSPS正交數字上變頻器 數據手冊

AN-0996: 在點對點微波發射系統中使用正交數字上變頻器(QDUC)的優勢

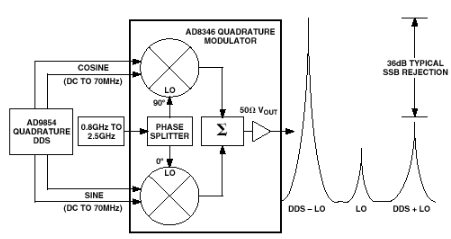

正交DDS信號至800至2500MHz頻段的單邊帶上變頻

AD9857 CMOS 200 MSPS、14位正交數字上變頻器技術手冊

AD9856 CMOS 200MHz正交數字上變頻器技術手冊

AD9856 CMOS 200MHz正交數字上變頻器技術手冊

評論