文章來源:老虎說芯

原文作者:老虎說芯

本文介紹了當(dāng)半導(dǎo)體技術(shù)從FinFET轉(zhuǎn)向GAA(Gate-All-Around)時工藝面臨的影響。

當(dāng)半導(dǎo)體技術(shù)從FinFET轉(zhuǎn)向GAA(Gate-All-Around)時,會對蝕刻、清洗、CVD/PVD等制造工藝產(chǎn)生一系列影響。

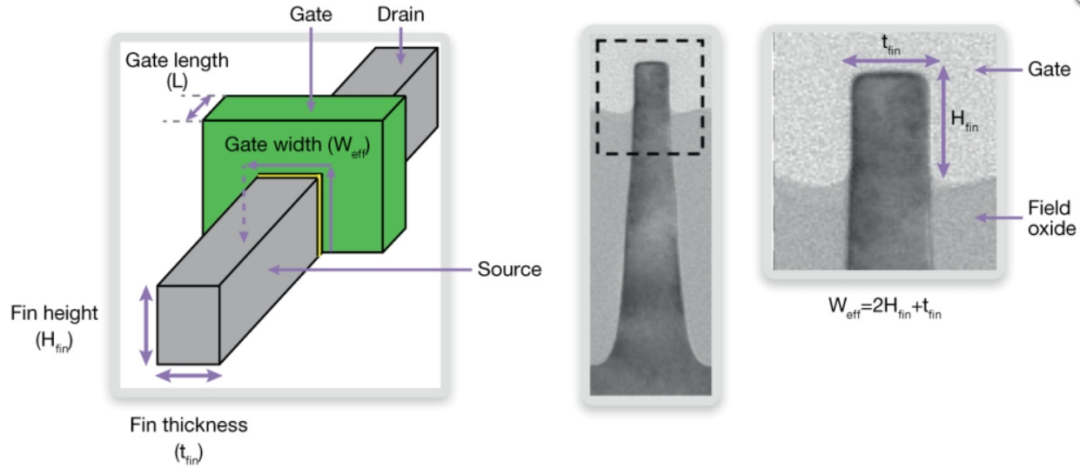

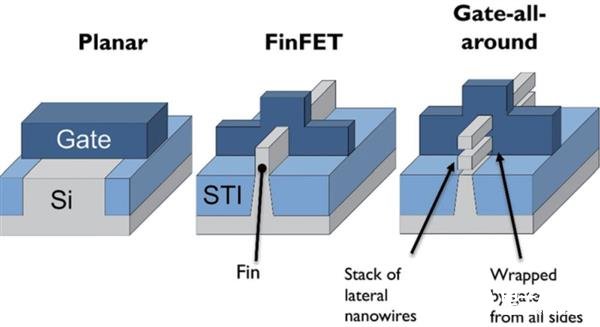

FinFET與GAA結(jié)構(gòu)的差異

FinFET結(jié)構(gòu):FinFET是一種三維結(jié)構(gòu),柵極圍繞著從襯底突出出來的硅鰭狀結(jié)構(gòu)。

GAA結(jié)構(gòu):GAA是一種更高級的三維結(jié)構(gòu),柵極完全包圍著納米線或納米片,從而提供更好的電氣控制。

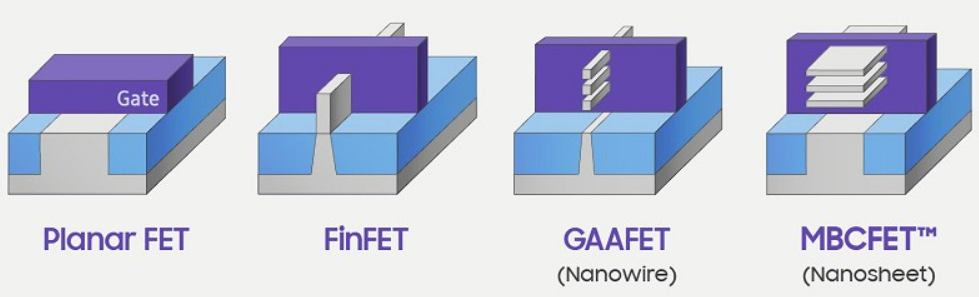

圖:FinFET和GAAFET示意

對蝕刻工藝的影響

FinFET中的蝕刻:需要高各向異性蝕刻工藝來形成鰭狀結(jié)構(gòu)。在形成鰭結(jié)構(gòu)的過程中,需要高選擇性蝕刻來避免損壞周圍的材料。

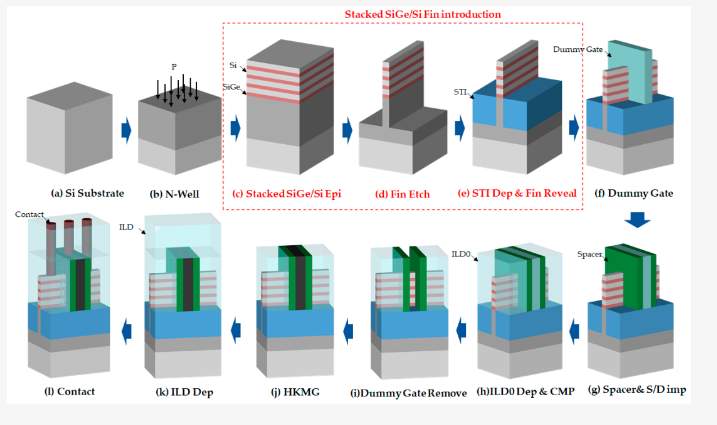

圖:SiGe/Si Channel FinFET device生產(chǎn)工藝

GAA中的蝕刻:由于GAA中納米線或納米片的精細(xì)尺寸,蝕刻工藝需要更高的精度。需要對多層材料進(jìn)行選擇性蝕刻,以確保納米線或納米片的完整性。可能需要引入新型蝕刻氣體或等離子體,以實現(xiàn)對納米結(jié)構(gòu)的高保真度蝕刻。

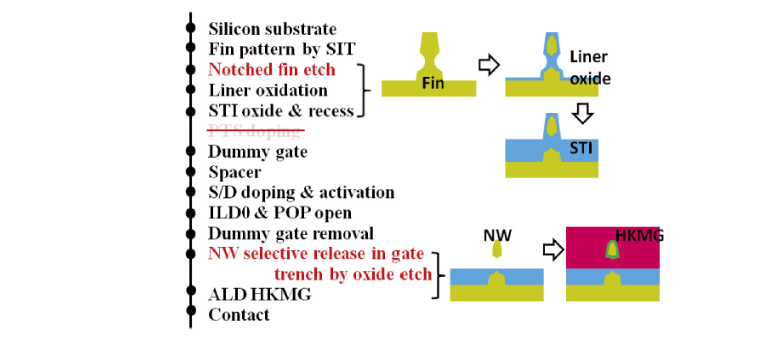

圖:GAA-SNWT的生產(chǎn)工藝

對清洗工藝的影響

FinFET中的清洗:主要針對鰭結(jié)構(gòu)的清洗,重點在于去除光刻膠和蝕刻殘留物。

GAA中的清洗:由于GAA結(jié)構(gòu)更加復(fù)雜,清洗工藝需要避免對納米線或納米片的損傷。需要引入更溫和、更有效的清洗溶劑和方法,以防止對細(xì)小結(jié)構(gòu)的腐蝕和損傷。

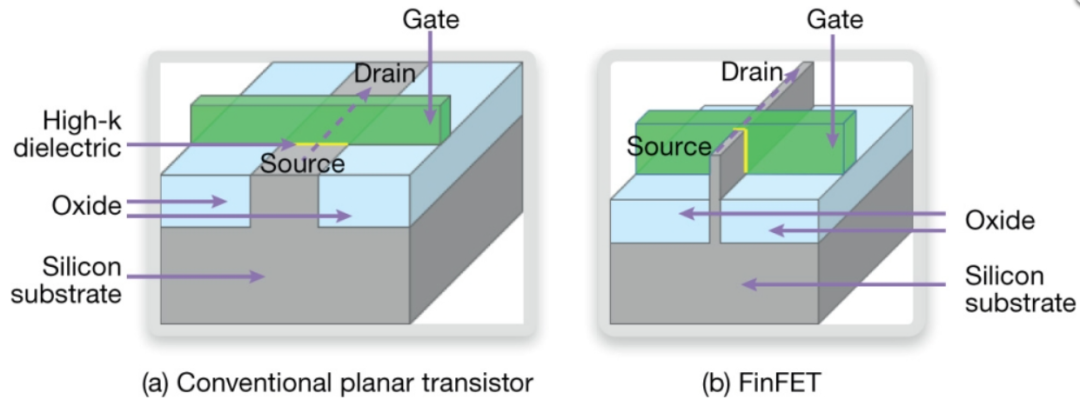

圖:傳統(tǒng)FET跟FinFET對比

對CVD/PVD工藝的影響

FinFET中的CVD/PVD:CVD(化學(xué)氣相沉積)和PVD(物理氣相沉積)主要用于鰭結(jié)構(gòu)的柵極材料沉積和絕緣層沉積。要求良好的沉積均勻性和填充性。

GAA中的CVD/PVD:由于GAA結(jié)構(gòu)需要完全包圍納米線或納米片,CVD/PVD工藝需要具備更高的沉積均勻性和精確控制能力。需要開發(fā)新的沉積材料和工藝,以適應(yīng)納米線或納米片的包覆要求。可能需要使用ALD(原子層沉積)等更精細(xì)的沉積技術(shù),以確保每一層材料的均勻性和厚度控制。

圖:FinFET器件的尺寸示意

其他相關(guān)工藝的影響

光刻:GAA結(jié)構(gòu)對光刻技術(shù)提出了更高的要求,需要更高分辨率的光刻技術(shù)來定義精細(xì)結(jié)構(gòu)。可能需要引入EUV(極紫外光刻)技術(shù),以滿足更小尺寸的需求。

材料選擇:由于GAA結(jié)構(gòu)中的納米線或納米片對材料性能的敏感性,需要選擇具有更高電氣性能和熱穩(wěn)定性的材料。

封裝技術(shù):GAA結(jié)構(gòu)的復(fù)雜性對后續(xù)的封裝技術(shù)也提出了新的挑戰(zhàn),需要確保納米結(jié)構(gòu)在封裝過程中的完整性和功能性。

總結(jié)來說,從FinFET到GAA的轉(zhuǎn)變對半導(dǎo)體制造的各個方面都提出了更高的要求,特別是在蝕刻、清洗和CVD/PVD等關(guān)鍵工藝上,需要進(jìn)行技術(shù)的改進(jìn)和創(chuàng)新,以適應(yīng)新結(jié)構(gòu)的制造需求。

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28832瀏覽量

236375 -

晶圓

+關(guān)注

關(guān)注

53文章

5142瀏覽量

129629 -

制造工藝

+關(guān)注

關(guān)注

2文章

204瀏覽量

20340 -

FinFET

+關(guān)注

關(guān)注

12文章

257瀏覽量

91104

原文標(biāo)題:半導(dǎo)體器件從FinFET轉(zhuǎn)向GAA時對晶圓制造工藝的影響

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

體硅FinFET和SOI FinFET的差異

FinFET(鰭型MOSFET)簡介

無刷直流電機(jī)(BLDC)與永磁同步電機(jī)(PMSM)結(jié)構(gòu)及其物理特性有何差異?

什么是FinFET?FinFET的工作原理是什么?

三星計劃2021年量產(chǎn)GAA電晶體

5nn重奪領(lǐng)導(dǎo)地位 GAA工藝性能提升將會更明顯

Intel放棄FinFET晶體管轉(zhuǎn)向GAA晶體管 GAA工藝性能提升或更明顯

FinFET到了歷史的盡頭?

曝英特爾5nm制程放棄FinFET電晶體轉(zhuǎn)向GAA

剖析晶體管結(jié)構(gòu)新變革以及GAA機(jī)遇與挑戰(zhàn)

芯片工程師,是時候了解GAA晶體管了

GAA器件集成工藝與關(guān)鍵挑戰(zhàn)

三星3nm GAA完整晶圓遭遇難產(chǎn),良率僅50%

SiGe外延工藝及其在外延生長、應(yīng)變硅應(yīng)用及GAA結(jié)構(gòu)中的作用

FinFet Process Flow—啞柵極的形成

FinFET與GAA結(jié)構(gòu)的差異及其影響

FinFET與GAA結(jié)構(gòu)的差異及其影響

評論