概述

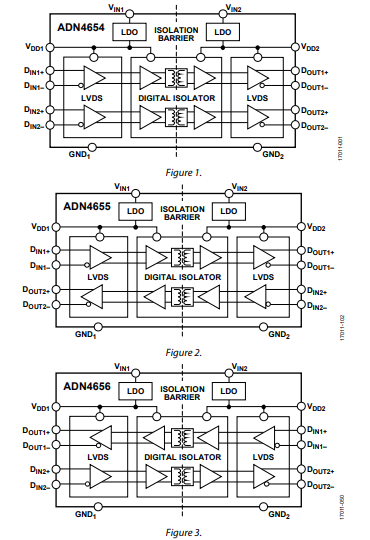

[ADN4654]/[ADN4655]/ADN4656^1^ 是信號隔離式低電壓差分信號 (LVDS) 緩沖器,能夠以低抖動在高達 1.1 Gbps 的數據速率下運行。這些器件集成了 ADI 公司的 iCoupler^?^ 技術,已針對高速運行進行增強,可以為符合 TIA/EIA-644-A 標準的 LVDS 驅動器和接收器提供電氣隔離。利用該集成,可實現 LVDS 信號鏈的嵌入式隔離。

ADN4654/ADN4655/ADN4656 包含多種通道配置,ADN4655 和 ADN4656 上的 LVDS 接收器包含一個故障安全機制,可在輸入懸空、短路或端接但未驅動時確保相應的 LVDS 驅動器輸出為邏輯 1。

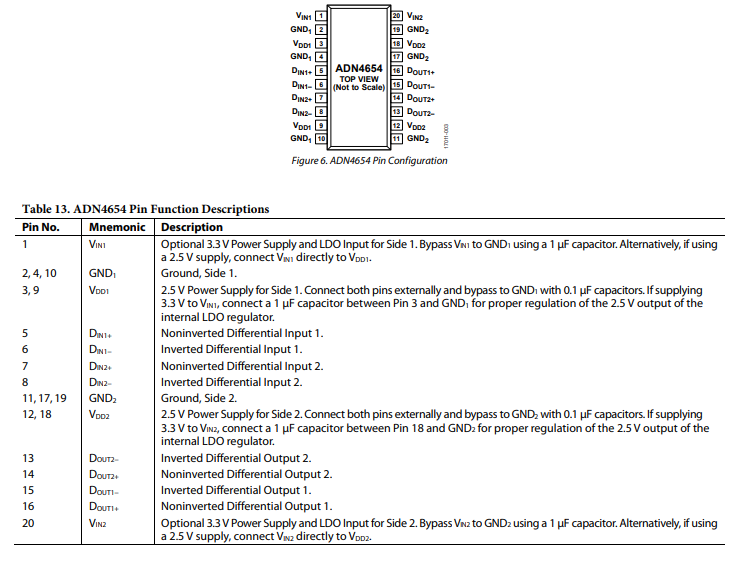

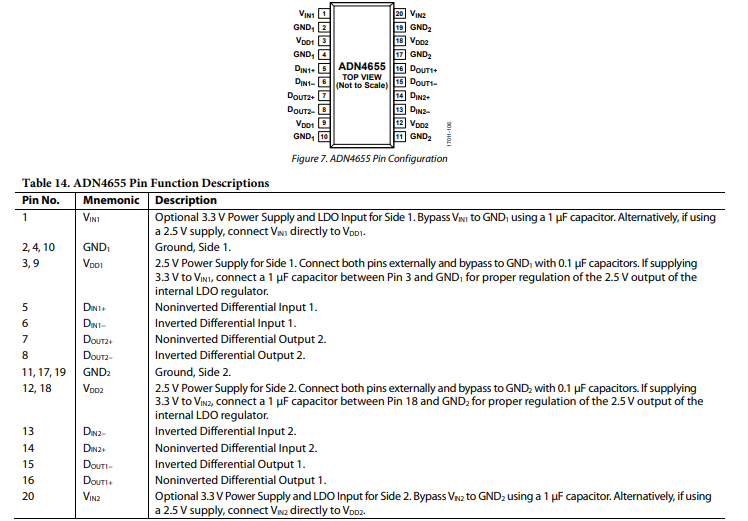

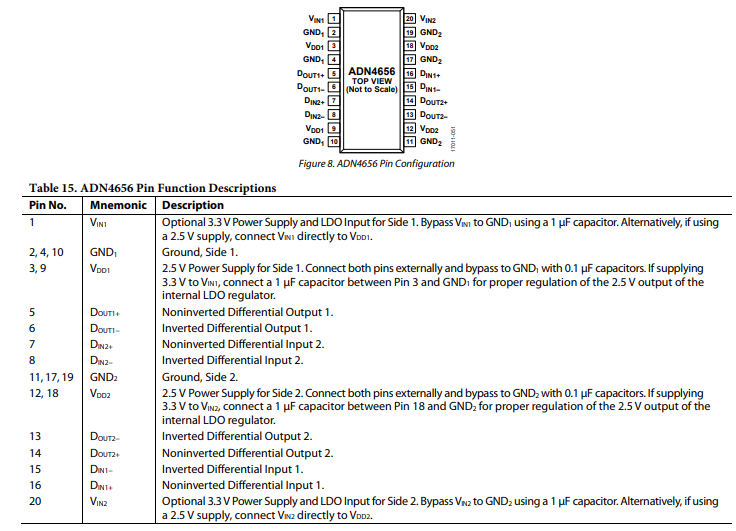

對于低抖動條件下的高速運行,LVDS 和隔離器電路依賴于 2.5 V 電源。集成的片內低壓差 (LDO) 穩壓器可以通過外部 3.3 V 電源提供所需的 2.5 V 電壓。這些器件完全適合在廣泛的工業溫度范圍內使用,采用具有 5 kV rms 隔離的 20 引腳寬體 SOIC_W 封裝,或采用具有 3.75 kV rms 隔離的 20 引腳 SSOP 封裝。

數據表:*附件:ADN4654 ADN4655 ADN4656 5kV RMS 3.75 kV RMS、雙通道LVDS千兆位隔離器技術手冊.pdf

應用

特性

- 5 kV rms 和 3.75 kV rms LVDS 隔離器

- 符合 TIA/EIA-644-A LVDS 標準

- 多種雙通道配置

- 能以高達 1.1 Gbps 的任意數據速率進行切換,具有低抖動

- 傳播延遲 4 ns(典型值)

- 隨機抖動 2.6 ps rms(典型值)

- 1.1 Gbps 時峰到峰總抖動 90 ps(典型值)

- 2.5 V 或 3.3 V 電源

- ?75 dBc 電源紋波抑制,相位雜散水平

- 抗干擾性

- ±8 kV IEC 61000-4-2 ESD 跨隔離柵保護

- 高共模瞬變抗擾度:>25 kV/μs

- 超越 EN 55022 B 級輻射發射限制,PRBS 為 1.1 Gbps

- 安全和監管審批(20 引腳 SOIC_W 封裝)

- UL(申請中):5000 V rms 持續 1 分鐘,符合 UL 1577 標準

- CSA 組件驗收通知 5A(申請中)

- VDE 符合性證書(申請中)

- DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

- V

IORM= 424 VPEAK

- 在開路、短路和端接輸入條件下故障安全輸出高電平 (ADN4655/ADN4656)

- 工作溫度范圍:?40°C 至 +125°C

- 7.8 mm 最小爬電距離和凈空

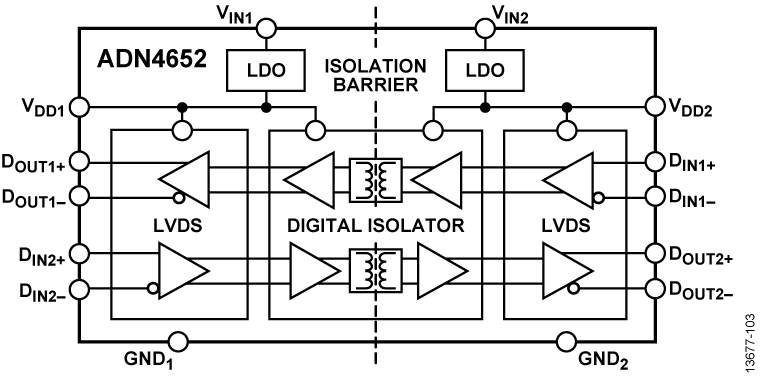

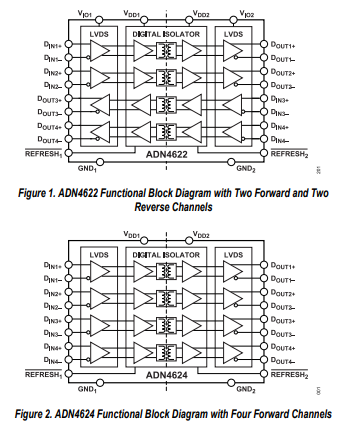

框圖

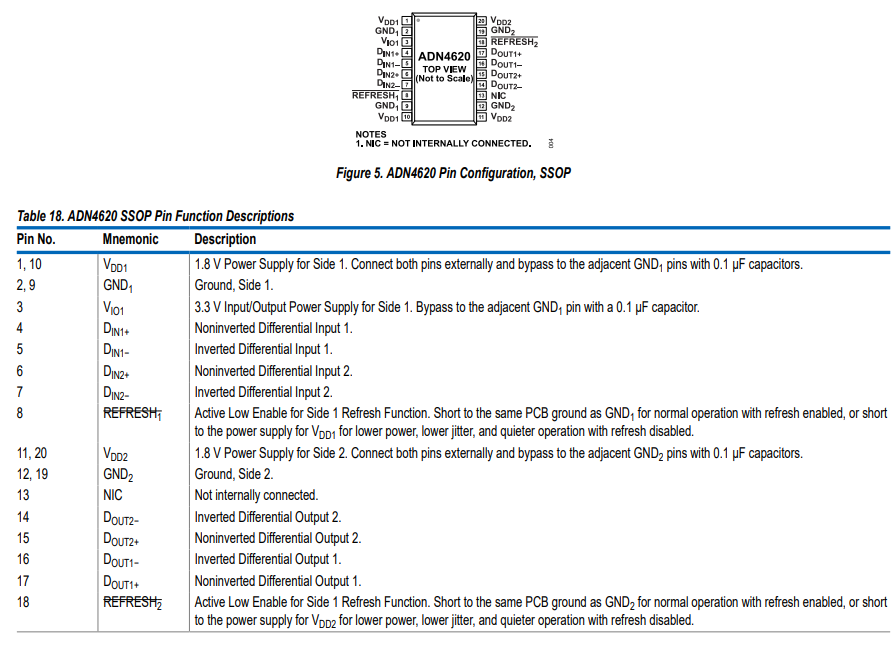

引腳配置描述

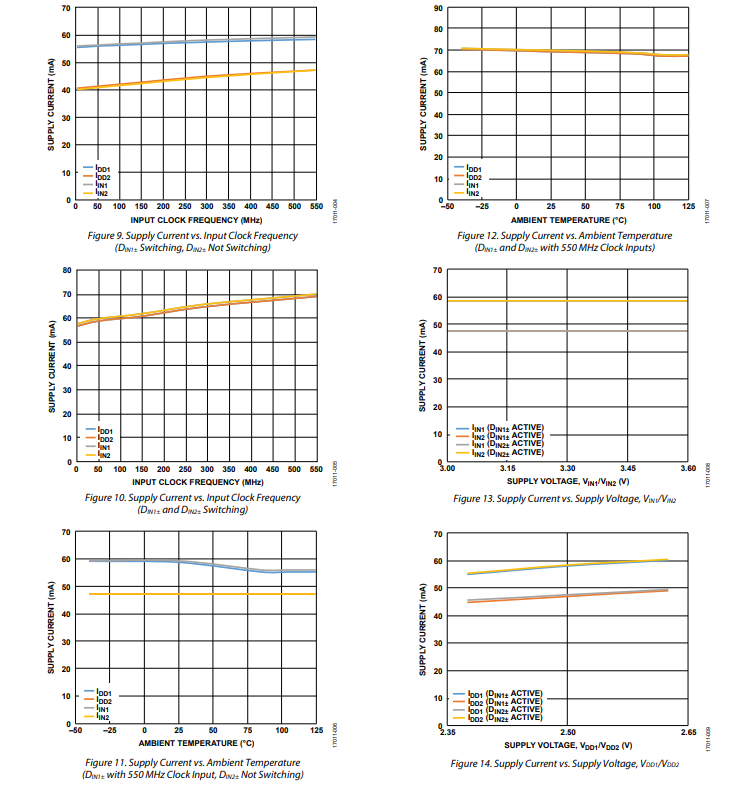

典型性能特征

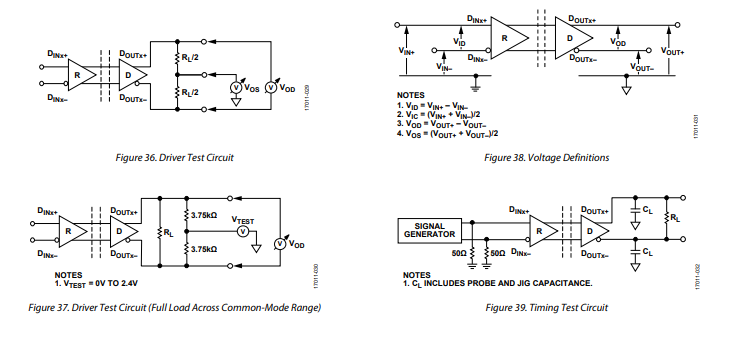

測試電路和開關特性

應用信息

印刷電路板(PCB)布局

ADN4654/ADN4655/ADN4656可以在高達0.55 GHz時鐘頻率下處理高速低壓差分信號(LVDS),并且在零歸位(NRZ)數據下可達到1.1 Gbps,可對LVDS走線應用最佳的端接和匹配規范。在盡可能靠近接收器的位置放置100 Ω終端電阻,跨接在(D_{IN+})和(D_{IN-})引腳上。

為確保信號完整性、降低系統抖動并將電磁干擾(EMI)降至最低,LVDS信號線上需要50 Ω的受控阻抗。走線寬度、相鄰走線之間的橫向距離以及接地層下方的距離都必須適當。通過將PCB接地層之間的過孔對緊密放置,也可以將相鄰走線對之間的串擾降至最低。

ADN4654/ADN4655/ADN4656符合EN 55022 B級輻射限制標準,在隔離器以高達1.1 Gbps PRBS數據速率運行時,無需額外考慮。在隔離高速時鐘(例如1.05 Gbps)時,可能需要20引腳小外形集成電路(SOIC)_W模型隔離間隙二極管效應,以確保在B級輻射限制標準下有足夠的裕量。

在使用ADN4654/ADN4655/ADN4656的應用中,最佳的高速PCB設計可避免PCB產生的其他輻射。配置高速連接時需注意,切換瞬變會出現在高速LVDS信號(尤其是時鐘信號)中。可采用共模扼流圈,以減少輻射排放。使用共模磁珠、鐵氧體或其他濾波器,或在LVDS連接器處采用合適的屏蔽,以及將電纜屏蔽層或PCB接地連接至地平面。

ADN4654/ADN4655/ADN4656要求(V_{IN})引腳使用100 nF的去耦電容。如果使用集成的LDO穩壓器,且電源電壓為2.5 V,直接將合適的(V_{IN})引腳連接到電源,并參考圖40(以ADN4654為例)。

當使用集成的LDO穩壓器時,在(V_{IN})引腳上以及最靠近(V_{OUT})引腳(LDO輸出)處需要1 μF的旁路電容,如圖41所示。

應用示例

- 模擬前端(AFE)的高速LVDS接口 :處理器間通信,或視頻與圖像數據可通過ADN4654等隔離器在隔離的電路板之間、板間或電纜接口進行傳輸。ADN4654提供電氣隔離,以及強大的外部端口,其低抖動和高驅動強度允許設備通過短電纜進行通信。高共模抑制能力確保在惡劣環境下的通信完整性,并且隔離功能可防止電磁兼容性(EMC)瞬變,如高達±8 kV的靜電放電(ESD)、電快速瞬變(EFT)和浪涌。ADN4654可隔離各種圖像協議,包括使用物理層共模抑制(CML)而非LVDS的協議。例如高清多媒體接口(HDMI),其中交流耦合和緩沖以及終端電阻網絡用于將CML(用于過渡最小化差分信號,TMDS數據和時鐘通道)轉換為ADN4654所需的LVDS電平。還可使用其他模擬器件隔離器組件,如ADuM1250/ADuM1251電容隔離器,隔離控制信號和電源(ADuM5020 isoPower集成隔離式直流 - 直流轉換器)。這可實現高達720p的分辨率。

- 其他電路 :其他電路可使用ADN4654隔離移動行業處理器接口(MIPI)CSI - 2、DisplayPort和基于LVDS的協議(如FPD - Link)。使用現場可編程門陣列(FPGA)或特定集成電路(ASIC)(如串行器/解串器(SERDES))通過多個ADN4654設備擴展帶寬,以支持1080p或4K視頻分辨率,為短距離光纖鏈路提供替代方案。

-

接收器

+關注

關注

15文章

2570瀏覽量

73843 -

緩沖器

+關注

關注

6文章

2048瀏覽量

46977 -

lvds

+關注

關注

2文章

1126瀏覽量

67432

發布評論請先 登錄

ADN4654 5 kV RMS 雙通道 LVDS 千兆比特隔離器

ADN4652 5 kV/3.75 kV rms、600 Mbps雙通道LVDS隔離器

ADN4650/ADN4651/ADN4652: 5 kV RMS、600 Mbps雙通道LVDS隔離器

UG-933:評估ADN4650 5 kV rms、600 Mbps LVDS隔離器(SOIC_W)

UG-900:評估ADN4651/ADN4652 5 kV rms、600 Mbps LVDS隔離器(SOIC_W)

ADN4654/ADN4655/ADN4656:5 kV RMS和3.75 kV RMS,雙通道LVDS Gigabit Sigabit數據Sheet

UG-第1373:評估ADN4654/ADN4655/ADN4656 5 kV rms雙通道LVDS千兆隔離器

ADN4622/ADN4624 5.7 kV rms/1.5 kV rms、四通道 LVDS 2.5 千兆位隔離器技術手冊

ADN4620/ADN4621 7.5 kV RMS/3.75 kV rms雙通道LVDS 2.5 Gbps隔離器技術手冊

ADN4654/ADN4655/ADN4656 5kV RMS/3.75 kV RMS、雙通道LVDS千兆位隔離器技術手冊

ADN4654/ADN4655/ADN4656 5kV RMS/3.75 kV RMS、雙通道LVDS千兆位隔離器技術手冊

評論