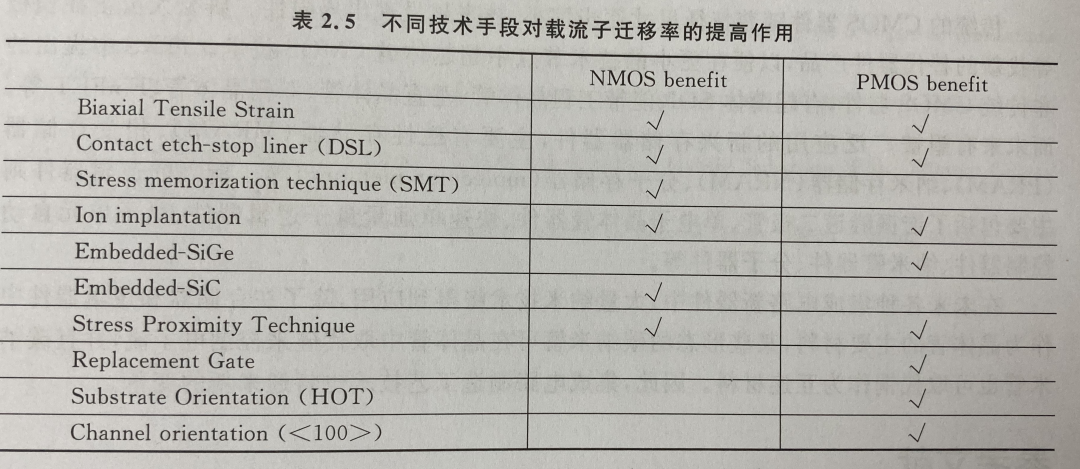

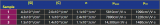

在高k金屬柵之外,另一種等效擴充的方法是增加通過器件溝道的電子或空穴的遷移率。表2.5列舉了一些提高器件載流子遷移率的手段及其對 PMOS或者 NMOS的作用。

應力技術是提高MOS 晶體管速度的有效途徑,它可改善NMOS晶體管電子遷移率和PMOS晶體管空穴遷移率,并可降低MOS 晶體管源/漏的,應變硅可通過如下3種方法獲得:①局部應力工藝,通過晶體管周圍薄膜和結構之間形成應力;②在器件溝道下方嵌入SiGe層;③對整個晶圓進行處理。

局部應力工藝已經被廣泛應用來提升CMOS 器件性能。源漏區嵌入式鍺硅技術產生的壓應力已經被證明可以有效提高 PMOS 器件的驅動電流。另外,源漏區嵌入式碳硅技術產生的拉應力可以提高 NMOS 器件的驅動電流。應力記憶技術在 NMOS 器件性能提升中得到使用。金屬前通孔雙極應力刻蝕阻擋層技術也是有效的局部應力工藝,拉應力可以提高 NMOS 的器件性能,而壓應力可以提高PMOS的器件性能。

對于 PMOS,眾所周知,具有(110)晶面取向的襯底比具有(100)晶面取向的襯底的空穴遷移率性能更高。而對于 NMOS,具有(110)晶面取向的襯底比具有(100)晶面取向的襯底的電子遷移率要差。晶向重排可以通過改變 PMOS 晶體管排版設計(layout)或者是在標準<100>晶體表面進行通道方向重新排列完成。

混合取向技術(Hybrid Orientation Technology, HOT)將PMOS 做在(110)晶面襯底,NMOS 做在(100)晶面襯底上,從而在改進PMOS 空穴遷移率的同時,不損害NMOS 的電子遷移率。IBM 公司在2003年IEDM上提出利用晶圓鍵合和選擇性外延技術,得到(110)晶面上的PMOS 和(100)晶面上的NMOS,報告顯示將其應用于 90nm CMOS, PMOS 性能可以提高40%。

硅直接鍵合(Direct Silicon Bonding,DSB) 晶片(一種鍵合(100)和(110)襯底的大塊CMOS 混合型晶片)是公認的推進這一方法的候選方案。IBM 曾將(100)層的面旋轉45°并將(110)襯底的DSB 層變薄來獲得標準的(100)晶片,成功地將環形振蕩器的延遲比傳統的DSB 襯底0°(100)晶片—它鍵合到一個具有兩個硅襯底,即(100)和(110)襯底的晶片上——的結果改進了10%,并將這一成果與技術集成到一起。新發展將環形振蕩器延遲比標準(100)晶片改進了30%。這一成果可以與能達到更高進展的技術集成到一起。

-

NMOS

+關注

關注

3文章

357瀏覽量

35425 -

晶體管

+關注

關注

77文章

9990瀏覽量

140865 -

PMOS

+關注

關注

4文章

266瀏覽量

30369

原文標題:載流子遷移率提高技術

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

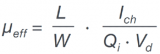

如何精準提取MOSFET溝道遷移率

載流子平衡的低壓高效有機白光器件

請問Beaglebone Black裝Linux系統都有哪些步驟啊?

載流子遷移率測量方法總結

載流子輸運現象之散射率、遷移率、電阻率、砷化鎵

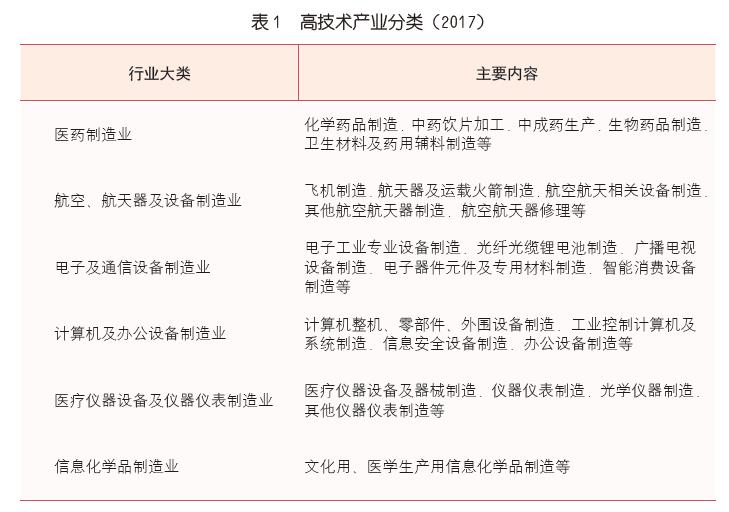

高技術制造業快速增長 高技術制造業包括哪些行業

8.2.10.3 4H-SiC反型層遷移率的實驗結果∈《碳化硅技術基本原理——生長、表征、器件和應用》

8.2.10.1 影響反型層遷移率的機理∈《碳化硅技術基本原理——生長、表征、器件和應用》

8.2.10.2 反型層遷移率的器件相關定義∈《碳化硅技術基本原理——生長、表征、器件和應用》

如何通過霍爾效應測量半導體中電子和空穴的遷移率?

高電子遷移率晶體管介紹

載流子遷移率提高技術詳解

載流子遷移率提高技術詳解

評論