電子發(fā)燒友綜合報道 作為HBM和3D NAND的核心技術(shù)之一,混合鍵合在近期受到很多關(guān)注,相關(guān)設(shè)備廠商尤其是國產(chǎn)設(shè)備廠商的市場前景巨大。那么混合鍵合是什么?

混合鍵合是一種結(jié)合介電層鍵合和金屬直接鍵合的先進封裝技術(shù),其核心目標(biāo)是實現(xiàn)芯片間高密度、低電阻的垂直互聯(lián)。

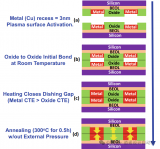

在工藝過程中,需要經(jīng)過對準(zhǔn)和鍵合、后鍵合處理等幾個流程。在對晶圓表面進行化學(xué)機械拋光(CMP)和清洗之后,通過光學(xué)或電子束對準(zhǔn)系統(tǒng)實現(xiàn)亞微米級(通常<200nm)的芯片間精準(zhǔn)對齊,尤其在芯片到晶圓(D2W)鍵合中,對準(zhǔn)誤差需接近零。

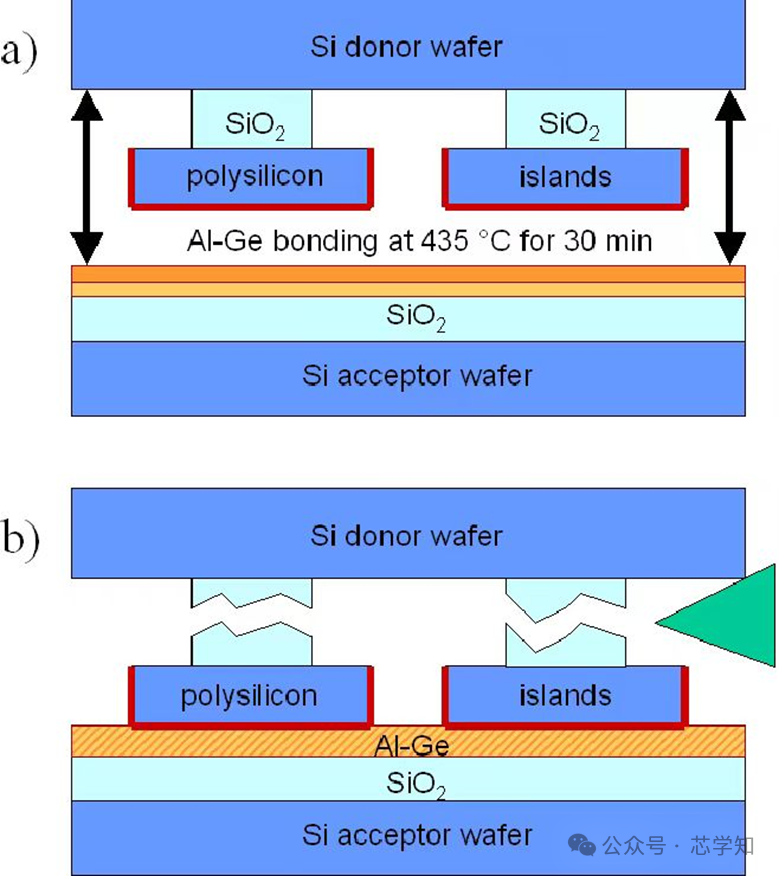

鍵合的方式有晶圓到晶圓W2W和芯片到晶圓D2W兩種,在鍵合過程中,銅觸點與介電層(如SiO?)同時接觸,通過熱壓或<400°C的低溫退火實現(xiàn)金屬-金屬和介電層-介電層的同步鍵合。

在鍵合后,還需要通過CMP工藝調(diào)整銅層高度,確保銅觸點略微凹陷于介電層表面(通常為50-100nm),以避免短路并提升鍵合強度;同時鍵合過程中產(chǎn)生的熱量需通過散熱結(jié)構(gòu)(如嵌入式熱沉)快速導(dǎo)出,防止局部熱應(yīng)力導(dǎo)致晶圓變形。

其中技術(shù)難點,主要有5點。首先從前面的工藝流程可以看到對準(zhǔn)精度是非常重要的,混合鍵合的互聯(lián)密度可達(dá)1000-5000 PPI,要求對準(zhǔn)誤差小于200nm,這對設(shè)備(如高精度對準(zhǔn)機)和工藝穩(wěn)定性提出了極高挑戰(zhàn);

其次是銅觸點的凹陷深度需高度均勻,否則會導(dǎo)致鍵合界面接觸不良或介電層破裂,這需要CMP工藝參數(shù)和設(shè)備的能力去實現(xiàn);

鍵合表面的粗糙度需控制在1nm以下,且必須避免任何有機或金屬污染,對清洗技術(shù)提出極高要求;

鍵合后的低溫退火(通常<400°C)需在保護氣氛(如氮氣)中進行,以消除界面缺陷并增強鍵合強度,但過高的熱應(yīng)力可能導(dǎo)致晶圓翹曲或材料疲勞;

最后,多次鍵合/解鍵合載體的使用、高精度設(shè)備投入及工藝復(fù)雜性顯著推高成本。此外,微小缺陷可能導(dǎo)致整片晶圓失效,需通過在線檢測技術(shù)提升良率。

相對應(yīng)地,混合鍵合工藝中,涉及到多種關(guān)鍵設(shè)備包括CMP、等離子體活化與清洗設(shè)備、高精度對準(zhǔn)與鍵合設(shè)備、退火設(shè)備、檢測與分析設(shè)備、電鍍ECU設(shè)備(用于銅柱的電化學(xué)沉積)、減薄與研磨設(shè)備等。

混合鍵合工藝對設(shè)備的精密性、穩(wěn)定性和集成度要求極高,尤其在對準(zhǔn)、鍵合、CMP和退火 環(huán)節(jié)存在顯著技術(shù)壁壘。目前,此類設(shè)備市場主要由日韓廠商,寶庫DISCO、東京電子和歐美廠商KLA、應(yīng)用材料等主導(dǎo);但國產(chǎn)設(shè)備已在CMP和檢測領(lǐng)域逐步突破,比如中電科45所、華海清科等。未來,隨著存儲、高性能計算和異構(gòu)集成需求的增長,混合鍵合設(shè)備的市場規(guī)模將持續(xù)擴大。

發(fā)布評論請先 登錄

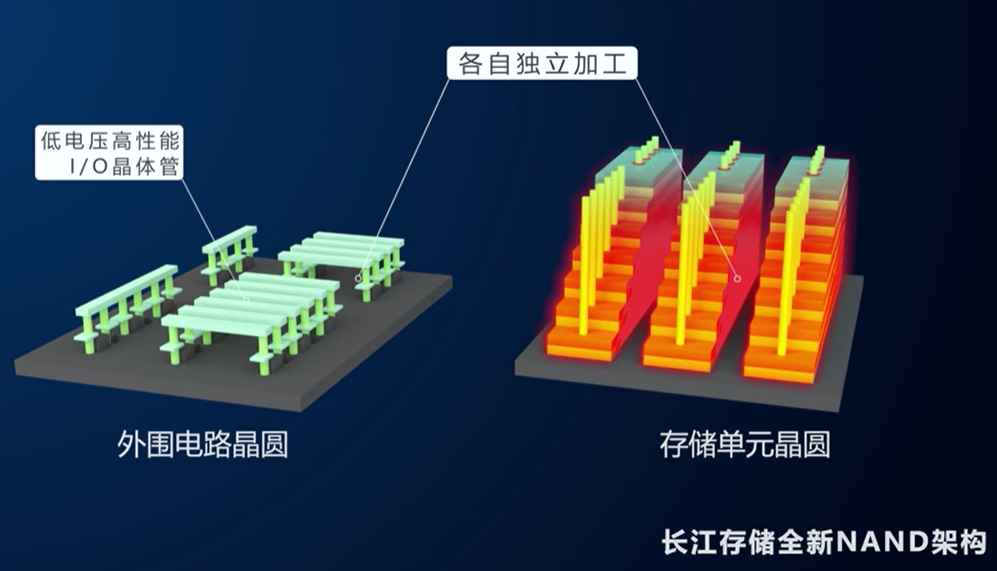

閃存沖擊400層+,混合鍵合技術(shù)傳來消息

引線鍵合的基礎(chǔ)知識

微流控芯片鍵合技術(shù)

混合鍵合:開創(chuàng)半導(dǎo)體互聯(lián)技術(shù)新紀(jì)元

混合鍵合的基本原理和優(yōu)勢

混合鍵合技術(shù):開啟3D芯片封裝新篇章

混合鍵合市場空間巨大,這些設(shè)備有機會迎來爆發(fā)

混合鍵合市場空間巨大,這些設(shè)備有機會迎來爆發(fā)

評論