引言

隨著半導體工藝不斷向深納米節點邁進,混合信號集成電路的重要性愈發顯著。從低功耗移動設備到高性能計算系統,眾多關鍵模塊如雙倍數據速率存儲器(DDR)、物理層接口(PHY)、通用串行總線(USB)、鎖相環(PLL)、低壓差穩壓器(LDO)、數模轉換器(ADC)等IP,已經被廣泛應用于各類系統中。這些IP的性能隨著工藝波動影響顯著,在先進工藝及多電壓、溫度(PVT)條件下更為明顯。如何實現高效且精準地IP特征化(IP Characterization),已成為確保芯片整體性能的關鍵挑戰。

然而,傳統蒙特卡洛(Monte Carlo)仿真方法因其依賴海量SPICE仿真樣本進行統計分析,面臨計算資源消耗巨大和收斂速度慢的瓶頸,已無法滿足這一需求。隨著工藝節點的演進,在人工智能芯片、高性能計算、無人駕駛等應用場景中,芯片設計對時序模型精度的要求日益嚴苛。如何實現“高精度”與“高效率”的平衡,并快速完成時序建模,成為亟待突破的核心問題。華大九天新一代混合信號電路IP模塊特征化提取工具——Empyrean Liberal IP,支持快速生成符合LVF(Liberty Variation Format)格式的標準庫文件,為混合信號IP模塊特征化提供高效、精準的解決方案。

Liberal IP的LVF K庫創新

LVF是集成電路單元庫特征化提取中的關鍵標準模型,用于描述制造工藝偏差對電路時序性能的影響。其核心包含兩部分:

OCV sigma模型:基于偏斜高斯分布,通過前后兩個正態分布的標準差(early/late)刻畫時序偏差。

Moment-based模型:支持非對稱、偏置或非高斯分布,精準捕獲超低電壓場景下時序變化的復雜形態。

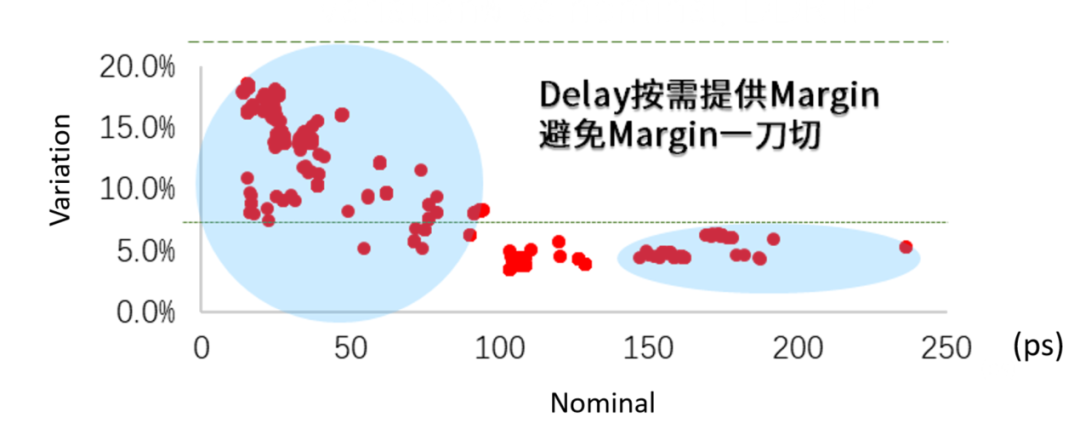

傳統的Margin 設置采用“一刀切”模式,難以兼顧不同場景的差異化需求。而 LVF方案能夠根據不同需求精準提供Margin,如下圖所示:正常Nominal延遲在50ps以內,控制誤差在正常變化(Nominal Variation)的10%~20%以內;當正常Nominal延遲超過100ps以后,誤差設置為Nominal Variation的5%以內。這種LVF模型方案能夠有效規避添加統一Margin而導致的時序約束過松(樂觀)或過緊(悲觀)的問題,實現精細化的時序管理,助力芯片設計在性能與可靠性之間達到平衡。

Liberal IP LVF K庫基于華大九天自主研發的Accurate LVF快速精準建庫技術,通過三大核心技術突破,重塑LVF建模流程:

靈敏度分析法:直接定位影響時序的關鍵參數,仿真次數降低 90% 以上。

智能參數過濾:基于相關性分析篩選器件的關鍵統計參數,避免冗余計算。

模塊劃分技術: 通過模塊劃分,把LVF的仿真縮小為一個個微型仿真,提高仿真效率,進一步壓縮建庫時間。

通過上述Liberal IP LVF K庫方法,K庫的構建效率得到了極大提升。以具體案例說明,如果目標是在3天內完成含有50個PVT的單元K庫構建,采用華大九天的創新技術,其效率相比采用傳統的蒙特卡洛方法可實現100倍效率提升!這意味原本可能需要數周甚至數月的復雜仿真任務,現在可以被壓縮到極短周期內高質量完成。同時,該技術顯著降低了資源消耗,大幅提高了工作效率。

Liberal IP的LVF K庫核心優勢

1高效建模

相較于傳統的蒙特卡洛法,需要數萬次的仿真次數,Liberal IP LVF K庫可以減少90%以上仿真量,性能提升高達100倍。這一突破性進展使在同等時間和資源條件下,可完成的特征化建庫任務量實現數量級提升,從而顯著加速設計周期,為設計企業帶來效率與成本的雙重優化。

2精準覆蓋

即使在復雜的非高斯分布場景和時序要求嚴苛的超低電壓環境下,Liberal IP仍能保持卓越性能。相較于依賴海量樣本的傳統蒙特卡洛方法,該工具能直接捕捉 ±3σ 邊界性能,并支持自定義 Sigma Level,其時序預測精度誤差率可控制在 1% 以內。這種高精度建模能力為芯片設計提供了強有力的支撐,確保其在各種極端條件下的穩定表現,顯著提升了芯片的可靠性與市場競爭力。

| 項目 | 傳統蒙特卡洛方法(MC) |

Liberal IPLVF K庫 |

| 仿真次數 | 數萬次/單元 | 減少90%以上 |

| 建模精度 |

依賴大量樣本 來保障建模精度 |

直接捕捉±3σ邊界性能,可自定義不同的sigma level |

| 樣本量 |

樣本量跟仿真次數成正比 非常難達成10萬次+仿真 |

支持10萬次+樣本量 |

3廣泛兼容

在實際應用中,Liberal IP LVF K庫顯示出極高的工具鏈兼容性,可輕松適配主流EDA環境。用戶僅需通過一條簡單命令,即可一鍵生成LVF庫文件,廣泛兼容現有設計流程,能夠被數字后端(包括時序分析,邏輯綜合,布局布線等)工具直接使用。這一特性顯著降低了技術整合成本,讓高效設計觸手可及。

客戶案例分享

某國際知名領先企業在其先進工藝節點的研發過程中遭遇嚴峻的時序收斂挑戰。在傳統模型下,芯片高頻運行時頻繁出現時序違規,過度的Margin設計會導致顯著的芯片性能折損。在引入 Liberal IP LVF K 庫之后,時序情況得到了顯著改善。

| Slackwith Margin |

Slack with LVF |

Slack Gain | |

|

建立時間 (Setup Time) |

-320ps | -261ps | 59ps |

|

保持時間 (Hold Time) |

-77ps | -61ps | 16ps |

建立時間(Setup Time):原始添加統一Margin方法,傳統模型方法的時序裕度Slack是 -320ps,而采用 LVF 后Slack提升至 -261ps,建立時間收益達到 59ps,這意味著時序建立過程更加穩定,為芯片高頻運行奠定了堅實基礎。

保持時間(Hold Time):傳統方法統一添加Margin,時序裕度為 -77ps,而采用 LVF 后Slack變為 -61ps,保持時間收益為 16ps,有效優化了時序保持特性,降低了數據保持階段的潛在風險。

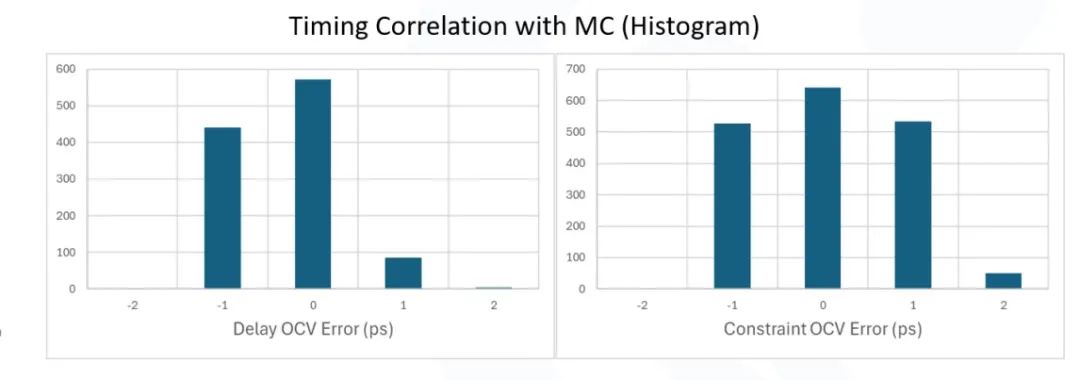

綜上兩個方面,其在保證芯片安全的前提下,LVF方法在建立時間和保持時間方面均獲得了時序收益,為芯片的整體競爭力奠定了堅實基礎。 進一步將Liberal IP LVF K庫結果與傳統蒙特卡洛方法所得結果的精度進行對比,LVF時序精度和蒙特卡洛結果高度契合。在延時片上偏差(Delay OCV)和約束片上偏差(Constraint OCV)方面,LVF和蒙卡的精度差異大部分集中分布在 ±1ps 區間內(對應柱狀圖峰值區域),整體時序精度偏差嚴格控制在2ps以內,充分驗證了LVF模型的高精準度。Liberal IP在大幅提升建庫效率的同時,仍能達到蒙特卡洛方法的精度水平,為芯片設計提供了高效精準的時序支撐。

基于Liberal IP在時序精度與性能方面的顯著提升,客戶已決定將其全面導入設計流程。這一決策不僅是對該工具技術實力的高度認可,更標志著客戶在芯片設計流程革新上邁出了關鍵一步。目前,客戶已成功推出高性能芯片產品,憑借該工具帶來的時序優勢,在市場競爭中搶占了性能與上市時間先機。

結語

作為中國EDA行業的領軍企業,華大九天致力于成為全流程、全領域、全球領先的EDA提供商。Empyrean Liberal IP特征化提取LVF K庫工具憑借“高效、精準”等核心特點,再次彰顯了華大九天在EDA領域的深厚技術積累和創新能力。未來,華大九天期待與更多集成電路設計企業攜手合作,共同應對混合信號電路特征化的挑戰,推動整個行業的持續進步與發展,攜手開創更加美好的未來。

北京華大九天科技股份有限公司(簡稱“華大九天”)成立于2009年,一直聚焦于EDA工具的開發、銷售及相關服務業務,致力于成為全流程、全領域、全球領先的EDA提供商。

華大九天主要產品包括全定制設計平臺EDA工具系統、數字電路設計EDA工具、晶圓制造EDA工具、先進封裝設計EDA工具和3DIC設計EDA工具等軟件及相關技術服務。其中,全定制設計平臺EDA工具系統包括模擬電路設計全流程EDA工具系統、存儲電路設計全流程EDA工具系統、射頻電路設計全流程EDA工具系統和平板顯示電路設計全流程EDA工具系統;技術服務主要包括基礎IP、晶圓制造工程服務及其他相關服務。產品和服務主要應用于集成電路設計、制造及封裝領域。

華大九天總部位于北京,在南京、成都、深圳、上海、香港、廣州、北京亦莊、西安和天津等地設有全資子公司,在武漢、廈門、蘇州等地設有分支機構。

-

鎖相環

+關注

關注

35文章

597瀏覽量

89534 -

混合信號

+關注

關注

0文章

507瀏覽量

65338 -

芯片設計

+關注

關注

15文章

1085瀏覽量

55609 -

eda

+關注

關注

71文章

2919瀏覽量

177720 -

華大九天

+關注

關注

5文章

93瀏覽量

13328

原文標題:混合信號芯片設計革命:Liberal IP通過LVF精準K庫實現性能全面躍升

文章出處:【微信號:華大九天,微信公眾號:華大九天】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

華大九天Empyrean Liberal工具助力數字集成電路設計

EDA2與華大九天達成戰略合作

華大九天發布停牌公告 重大事項擬收購芯和半導體

突發!華大九天啟動對芯和半導體控股權收購籌劃

華大九天ALPS模擬仿真器的Snapshot功能解析

?適配 17 款國產 AI 芯片,中國移動推出九天 AI 大模型?

華大九天Empyrean Polas工具解決功率設計難題

華大九天推出PowerMOS版圖自動化工具

中國電子成國產EDA龍頭華大九天實控人

中國電子集團入主國內EDA(電子設計自動化)產業龍頭企業華大九天

華大九天生態伙伴及用戶大會圓滿落幕

華大九天生態伙伴及用戶大會完美收官,多領域新技術飛躍創“芯”

華大九天Empyrean Liberal IP驅動混合信號芯片設計革命

華大九天Empyrean Liberal IP驅動混合信號芯片設計革命

評論