來源:OpenFPGA;作者:碎碎思

在創(chuàng)建 RTL 示例時,經(jīng)常使用 VHDL 2008 附帶的 VHDL 包。它提供了出色的功能,可以高效地處理定點數(shù),當(dāng)然,它們也是可綜合的。該包的一些優(yōu)點包括:

有符號和無符號(后綴和后綴)定點向量。

輕松將定點數(shù)表示并量化為定點向量。

小數(shù)點位于向量元素 0 和 -1 之間。這樣就無需在運算過程中跟蹤小數(shù)點以進行對齊(大量運算這點很難把握)。

運算的溢出、舍入和范圍管理有明確的定義。

算術(shù)和比較運算符。

因此,當(dāng)需要實現(xiàn)算法時,我會使用這個包。但是實際應(yīng)用時,還會有很多浮點運算。

自然而然地,一個問題出現(xiàn)了:用定點和浮點實現(xiàn)同一個方程時,資源有什么區(qū)別?

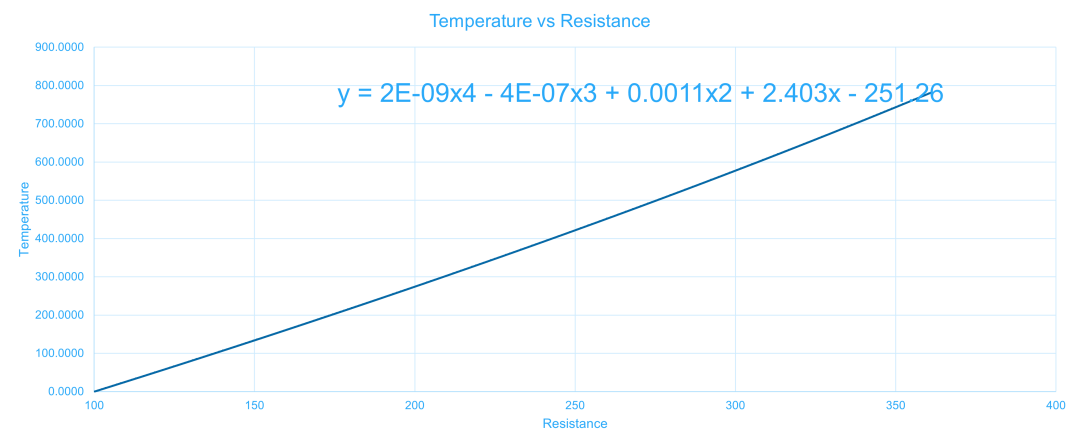

我們將要看的例子是如何利用多項式近似地將ADC讀數(shù)轉(zhuǎn)換為溫度值。這在工業(yè)應(yīng)用中很常見(使用鉑電阻溫度計時)。

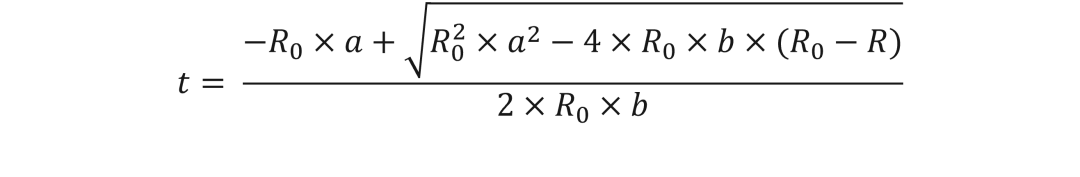

要實現(xiàn)的具體方程是 y = 2E-09x4 - 4E-07x3 + 0.011x2 + 2.403x - 251.26,該方程是從繪制方程式中提取出來的。雖然我們可以直接實現(xiàn)該方程,但這會非常浪費資源,還會增加開發(fā)的復(fù)雜性和風(fēng)險。

使用定點數(shù)系統(tǒng),我們需要做一些量化來保持精度和準(zhǔn)確度。

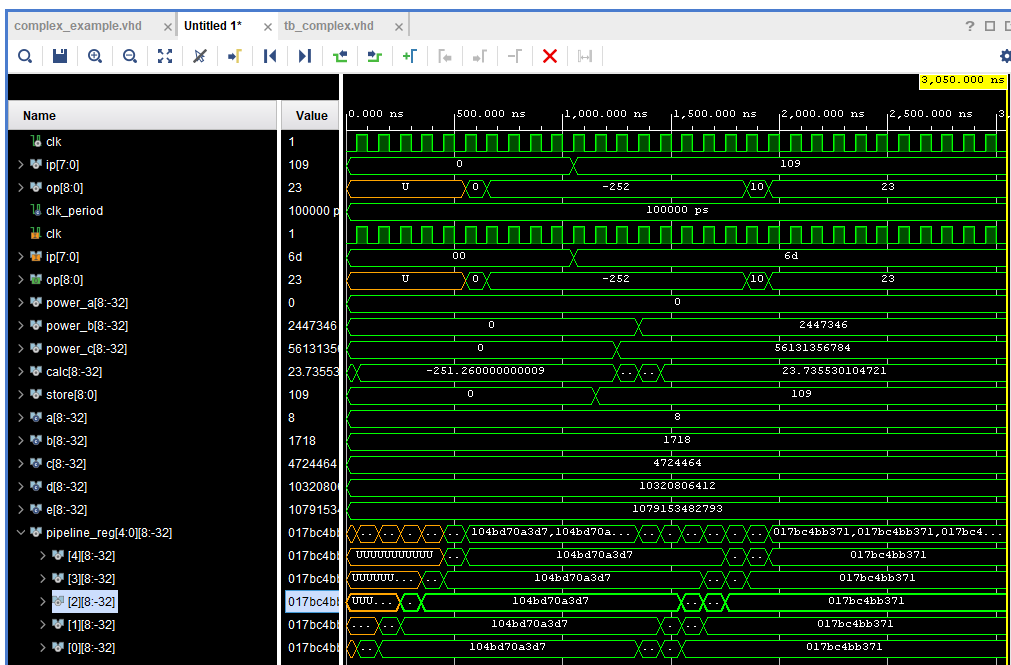

代碼和一個簡單的仿真如下。

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use ieee.fixed_pkg.all; entity complex_example is port( clk :instd_logic; ip :instd_logic_vector(7 downto 0); op : out std_logic_vector(8 downto 0)); end complex_example; architecture Behavioral of complex_example is signal power_a : sfixed(8 downto -32):=(others=>'0'); signal power_b : sfixed(8 downto -32):=(others=>'0'); signal power_c : sfixed(8 downto -32):=(others=>'0'); signal calc : sfixed(8 downto -32) :=(others=>'0'); signal store : sfixed(8 downto 0) := (others =>'0'); constant a : sfixed(8 downto -32):= to_sfixed( 2.00E-09, 8,-32 ); constant b : sfixed(8 downto -32):= to_sfixed( 4.00E-07, 8,-32 ); constant c : sfixed(8 downto -32):= to_sfixed( 0.0011, 8,-32 ); constant d : sfixed(8 downto -32):= to_sfixed( 2.403, 8,-32 ); constant e : sfixed(8 downto -32):= to_sfixed( 251.26, 8,-32 ); typereg_array is array (9 downto 0) of sfixed(8 downto -32); signal pipeline_reg : reg_array; begin cvd : process(clk) begin ifrising_edge(clk)then store <= to_sfixed('0'&ip,store); ? ? power_a <= resize (arg => power_b * store * a, size_res => power_a); power_b <= resize (arg => power_c * store * b, size_res => power_b); power_c <= resize (arg => store * store * c, size_res => power_c); calc <= resize (arg => power_a - power_b + power_c + (store * d) - e, size_res => calc); pipeline_reg <= pipeline_reg(pipeline_reg'high -1 downto 0 ) & calc; ? ? ?? ?op <= to_slv(pipeline_reg(pipeline_reg'high)(8 downto 0)); ? end?if; end process; end Behavioral;

對于 109 Ω的電阻輸入,溫度應(yīng)報告為 23.7°C。我們可以在下面的定點仿真中看到,結(jié)果符合預(yù)期,精度在可接受的范圍內(nèi)。

使用浮點包實現(xiàn)相同的功能,以類似的方式實現(xiàn)

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.FLOAT_pkg.ALL; -- Use the floating-point package

entity FloatingPointPolynomial is

Port (

clk :inSTD_LOGIC;

x :infloat32; -- Input x as a 32-bit floating-point number

y : out float32 -- Output y as a 32-bit floating-point number );

end FloatingPointPolynomial;

architecture Behavioral of FloatingPointPolynomial is

-- Define constantsforthe polynomial coefficients

constant a4 : float32 := TO_float(2.00E-09);

constant a3 : float32 := TO_float(-4.00E-07);

constant a2 : float32 := TO_float(0.011);

constant a1 : float32 := TO_float(2.403);

constant a0 : float32 := TO_float(-251.26);

signal x2, x3, x4 : float32; -- Intermediate powers of x

signal term4, term3, term2, term1 : float32; -- Polynomial terms

signal res : float32;

typereg_array is array (9 downto 0) of float32;

signal pipeline_reg : reg_array;

begin

process(clk)

begin

ifrising_edge(clk)then

-- Calculate powers of x

x2 <= x * x;

? ? ? ? ? ? x3 <= x2 * x;

? ? ? ? ? ? x4 <= x3 * x;

? ? ? ? ? ? -- Calculate each term?in?the polynomial

? ? ? ? ? ? term4 <= a4 * x4;

? ? ? ? ? ? term3 <= a3 * x3;

? ? ? ? ? ? term2 <= a2 * x2;

? ? ? ? ? ? term1 <= a1 * x;

? ? ? ? ? ? -- Calculate final result

? ? ? ? ? ? res <= term4 + term3 + term2 + term1 + a0;

? ? ? ? ? ? pipeline_reg <= pipeline_reg(pipeline_reg'high -1 downto 0 ) &?

? ? ? ?res;

? ? ? ? ? ? y <= (pipeline_reg(pipeline_reg'high));

? ? ? ? end?if;

? ? end process;

end Behavioral;

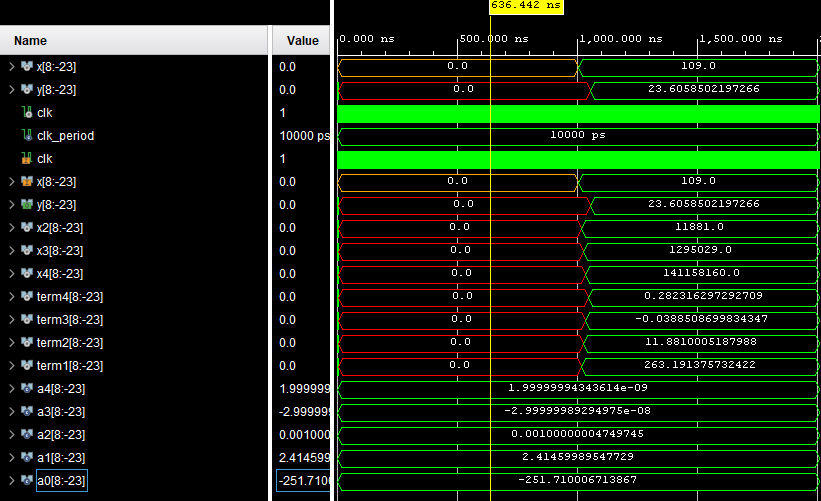

仿真再次顯示了預(yù)期的結(jié)果,作為浮點結(jié)果,我們得到的結(jié)果也包括分?jǐn)?shù)元素。

因此,定點和浮點都能夠?qū)崿F(xiàn)定義的算法。

為了了解利用所需的資源,決定將這兩種算數(shù)實現(xiàn)都以 K26 SoM 為目標(biāo)進行綜合。

運行綜合將識別每個模塊所需的資源。

正如預(yù)期的那樣,定點實現(xiàn)所需的邏輯占用空間比浮點實現(xiàn)所需的小得多。

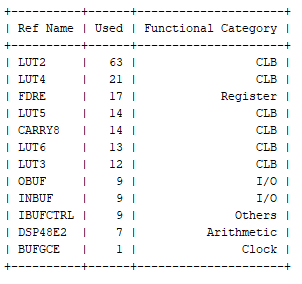

定點實現(xiàn)

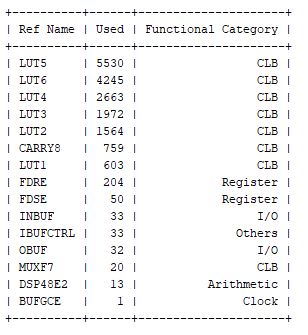

浮點實現(xiàn)

我們不僅需要考慮邏輯占用空間,還需要考慮時序性能。考慮到這一點,將兩個設(shè)計都設(shè)置為 200 MHz 運行,并從一開始就實現(xiàn)了基準(zhǔn)時序收斂。

實現(xiàn)時序收斂比定點收斂更重要,這在浮點實現(xiàn)中是可以預(yù)料到的。不得不重新審視設(shè)計,并在幾個關(guān)鍵階段實現(xiàn)流水線,因為最初的代碼只是為了確定占用空間的差異。

值得注意的是,Versal 系列中的 DSP58 支持浮點運算,但它不能直接從 float32 映射到 DSP。為了利用此功能,我們需要實例化配置為 FP32 操作的 DSP58,或者利用 Vivado IP 集成器提供的浮點 IP。

總結(jié)這篇博客,正如預(yù)期的那樣,在使用 VHDL 中的浮點庫時,邏輯占用空間存在很大差異。

建議在必要時利用定點,并在絕對必要時限制浮點。

-

仿真

+關(guān)注

關(guān)注

52文章

4257瀏覽量

135643 -

RTL

+關(guān)注

關(guān)注

1文章

389瀏覽量

60985 -

運算符

+關(guān)注

關(guān)注

0文章

173瀏覽量

11438

原文標(biāo)題:FPGA定點和浮點數(shù)學(xué)運算-實例對比

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

浮點數(shù)與定點數(shù)

【安富萊——DSP教程】第7章 DSP定點數(shù)和浮點數(shù)(重要)

第7章 DSP定點數(shù)和浮點數(shù)

CPU執(zhí)行一個需要浮點數(shù)運算的程序時有三種方式

定點數(shù)和浮點數(shù)的區(qū)別是什么

如何在GCC中為具有FPU的Cortex M4啟用硬件浮點數(shù)學(xué)運算呢?

擴充浮點運算集是否需要自己在FPGA板子上設(shè)置一個定點數(shù)轉(zhuǎn)為浮點數(shù)的部分?

在FPGA里浮點數(shù)與定點數(shù)表示法原理展示

單片機浮點數(shù)運算的源碼設(shè)計

FPGA中浮點運算定標(biāo)實現(xiàn)方法

定點數(shù)和浮點數(shù)在STM32單片機中使用傅里葉(FFT)變換的理解

如何在FPGA中正確處理浮點數(shù)運算

FPGA浮點數(shù)轉(zhuǎn)化為定點數(shù)方法

FPGA浮點數(shù)表示及計算機數(shù)值表示規(guī)則

定點數(shù)和浮點數(shù)的概念 浮點數(shù)二進制序列與指數(shù)表達式之間的轉(zhuǎn)化

FPGA定點和浮點數(shù)學(xué)運算實例對比

FPGA定點和浮點數(shù)學(xué)運算實例對比

評論