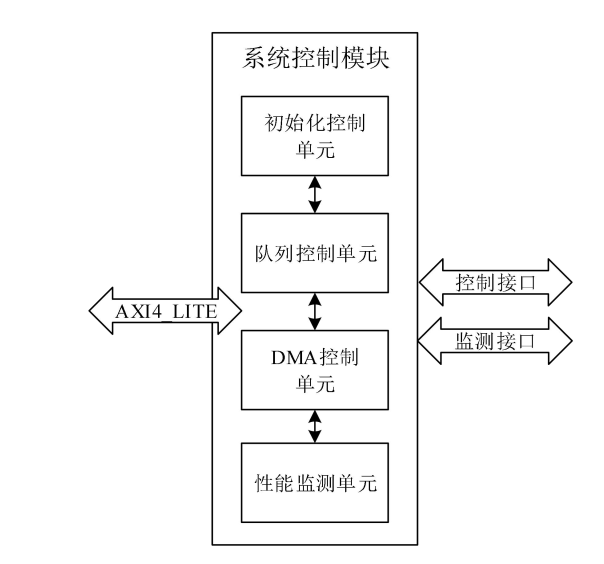

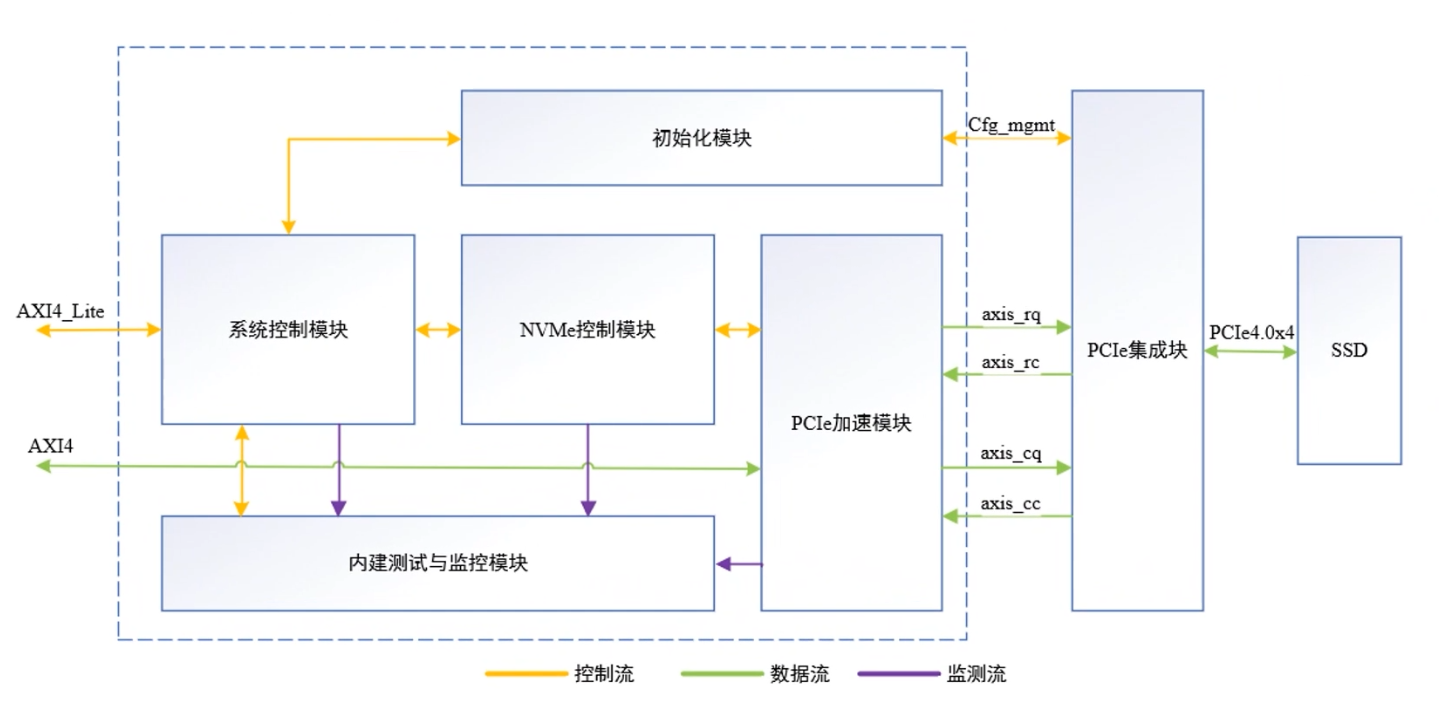

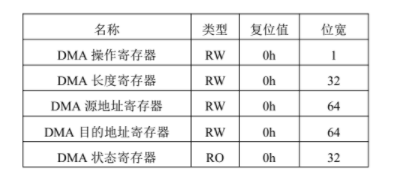

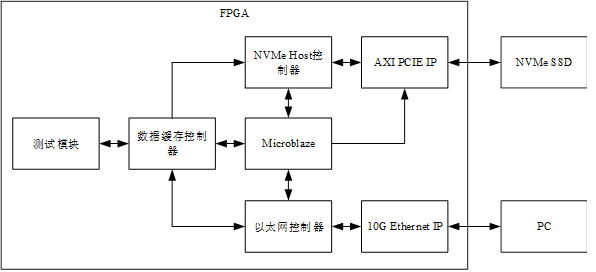

系統控制模塊負責實現 NVMe over PCI 邏輯加速引擎的控制功能, 其結構如圖 1 所示。 用戶通過系統控制模塊實現對初始化功能、 隊列管理功能、 DMA 功能等主要功能的控制, 同時邏輯加速引擎的工作狀態也通過此模塊反饋給用戶。 系統控制模塊包含了初始化控制單元、 隊列控制單元、 DMA 控制單元和性能監測單元。 在各控制單元和監測單元中包含了多個寄存器組, 用戶可通過訪問寄存器組的方式實現功能的控制和狀態的監測。 為方便用戶訪問這些寄存器組, 系統控制模塊采用 AXI4-Lite 總線作為接口, AXI4-Lite 接口具有低帶寬、 低延時、 低復雜度的特點, 采用該接口可以簡化設計邏輯和功耗, 同時作為標準協議接口可以更方便的集成到用戶環境。

圖1 NVMe over PCI 控制模塊結構圖

更多博文鏈接:https://blog.csdn.net/tiantianuser/article/details/148995285

審核編輯 黃宇

-

PCI

+關注

關注

5文章

679瀏覽量

131725 -

控制模塊

+關注

關注

2文章

138瀏覽量

19271 -

nvme

+關注

關注

0文章

249瀏覽量

23187

發布評論請先 登錄

NVMe IP高速傳輸卻不依賴XDMA設計之六:性能監測單元設計

NVMe IP高速傳輸擺脫XDMA設計之四:系統控制模塊設計

NVMe IP高速傳輸卻不依賴XDMA設計之三:系統架構

NVMe IP高速傳輸卻不依賴便利的XDMA設計之三:系統架構

NVMe IP高速傳輸卻不依賴XDMA設計之二:PCIe讀寫邏輯

NVMe IP之AXI4總線分析

NVMe控制器IP設計之接口轉換

NVMe IP over PCIe 4.0:擺脫XDMA,實現超高速!

NVMe IP高速傳輸卻不依賴XDMA設計之四:系統控制模塊

NVMe IP高速傳輸卻不依賴XDMA設計之四:系統控制模塊

評論