該視頻將向開發(fā)人員介紹Xilinx和Avnet的新平臺(tái),Spartan-6 FPGA 嵌入式套件基于 Spartan?-6 LX45T FPGA 之上,包含可擴(kuò)展式開發(fā)板、關(guān)鍵設(shè)計(jì)工具以及實(shí)現(xiàn)高效嵌入式應(yīng)用開發(fā)所需的 IP 核。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1645文章

22012瀏覽量

616688 -

嵌入式

+關(guān)注

關(guān)注

5146文章

19599瀏覽量

316326 -

賽靈思

+關(guān)注

關(guān)注

33文章

1797瀏覽量

132226

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

AMD Spartan UltraScale+ FPGA 開始量產(chǎn)出貨

高 I/O、低功耗及先進(jìn)的安全功能,適用于成本敏感型邊緣應(yīng)用 AMD 很高興宣布,Spartan UltraScale+ 成本優(yōu)化型系列的首批器件現(xiàn)已投入量產(chǎn)! 三款最小型的器件——SU10P

Analog Devices Inc. DC3080A-KIT演示套件數(shù)據(jù)手冊(cè)

、DC3078A無線接收器和兩個(gè)6mm DC3079A應(yīng)用尺寸接收器。DC3080A-KIT演示套件采用DC3078A無線充電器接收器,具有外部涓流充電電路。當(dāng)插入電壓低于2.8V深度放電電池時(shí),該涓流

XILINX XCZU67DR FPGA完整原理圖

電子發(fā)燒友網(wǎng)站提供《XILINX XCZU67DR FPGA完整原理圖.pdf》資料免費(fèi)下載

發(fā)表于 05-30 15:29

?0次下載

請(qǐng)問NICE協(xié)處理器與傳統(tǒng)ocb外設(shè)相比的優(yōu)勢(shì)有什么?

使用擴(kuò)展指令調(diào)用NICE協(xié)處理器完成預(yù)定操作,給出的優(yōu)勢(shì)通常為代替CPU處理數(shù)據(jù),但其實(shí)使用片上總線掛一個(gè)外設(shè),然后驅(qū)動(dòng)外設(shè)完成操作也可以實(shí)現(xiàn)相同的功能,所以想問一下協(xié)

發(fā)表于 05-29 08:21

NICE協(xié)處理器與傳統(tǒng)ocb外設(shè)相比的優(yōu)勢(shì)有什么?

使用擴(kuò)展指令調(diào)用NICE協(xié)處理器完成預(yù)定操作,給出的優(yōu)勢(shì)通常為代替CPU處理數(shù)據(jù),但其實(shí)使用片上總線掛一個(gè)外設(shè),然后驅(qū)動(dòng)外設(shè)完成操作也可以實(shí)現(xiàn)相同的功能,所以想問一下協(xié)

發(fā)表于 05-28 08:31

spartan 6 14位LVDS 反序列化

spartan 6系列的FPGA 與14位ADC 輸出LVDS信號(hào) 怎么實(shí)現(xiàn)1:14的串轉(zhuǎn)并呢?iserdes2 在ise里面最高只能實(shí)現(xiàn)8位啊

發(fā)表于 04-25 15:20

ADS54J64EVM開發(fā)板可以配套使用哪些Xilinx FPGA開發(fā)板呢?

個(gè) FMC 連接器,該連接器也可與領(lǐng)先的FPGA制造商提供的許多開發(fā)套件兼容。

那么問題來了,TI的這兩個(gè)AD開發(fā)板到底能不能直接用在Xilinx FPGA的其他通用開發(fā)板上,例如 K

發(fā)表于 12-20 10:18

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評(píng)估套件

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評(píng)估套件可快速啟動(dòng)汽車、工業(yè)、視頻和通信應(yīng)用設(shè)計(jì)。AMD/Xilinx MPSoC ZCU102 評(píng)估套

采用Xilinx FPGA的AFE79xx SPI啟動(dòng)指南

電子發(fā)燒友網(wǎng)站提供《采用Xilinx FPGA的AFE79xx SPI啟動(dòng)指南.pdf》資料免費(fèi)下載

發(fā)表于 11-15 15:28

?0次下載

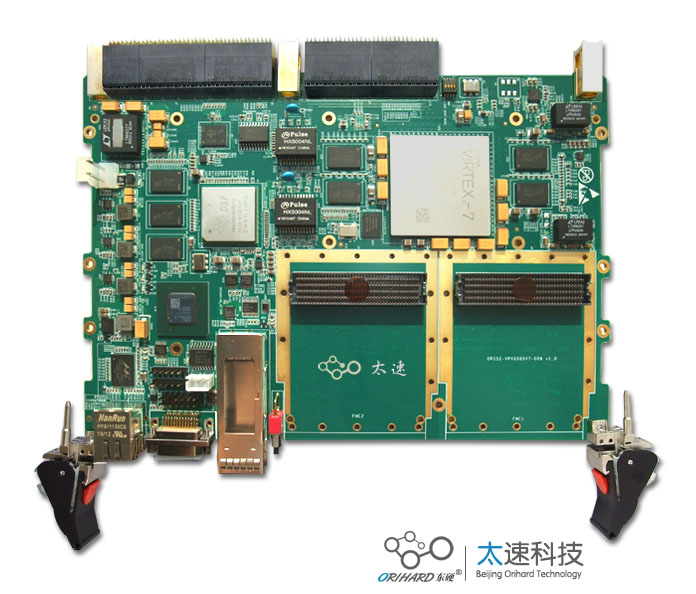

基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信號(hào)處理卡

本板卡基于標(biāo)準(zhǔn)6U VPX 架構(gòu),為通用高性能信號(hào)處理平臺(tái),系我公司自主研發(fā)。板卡采用一片TI DSP TMS320C6678和一片Xilinx公司Virtex 7系列的FPGA

Xilinx 7系列FPGA PCIe Gen3的應(yīng)用接口及特性

Xilinx7系列FPGA集成了新一代PCI Express集成塊,支持8.0Gb/s數(shù)據(jù)速率的PCI Express 3.0。本文介紹了7系列FPGA PCIe Gen3的應(yīng)用接口及一些特性。

使用TMS320C6416協(xié)處理器:Turbo協(xié)處理器(TCP)

電子發(fā)燒友網(wǎng)站提供《使用TMS320C6416協(xié)處理器:Turbo協(xié)處理器(TCP).pdf》資料免費(fèi)下載

發(fā)表于 10-23 10:16

?0次下載

使用TMS320C6416協(xié)處理器:Viterbi協(xié)處理器(VCP)

電子發(fā)燒友網(wǎng)站提供《使用TMS320C6416協(xié)處理器:Viterbi協(xié)處理器(VCP).pdf》資料免費(fèi)下載

發(fā)表于 10-21 09:36

?0次下載

如何在FPGA中實(shí)現(xiàn)隨機(jī)數(shù)發(fā)生器

分享如何在Xilinx Breadboardable Spartan-7 FPGA, CMOD S7中實(shí)現(xiàn)4位偽隨機(jī)數(shù)發(fā)生器(PRNGs)。

一文了解FPGA比特流的內(nèi)部結(jié)構(gòu)

比特流是一個(gè)常用詞匯,用于描述包含FPGA完整內(nèi)部配置狀態(tài)的文件,包括布線、邏輯資源和IO設(shè)置。大多數(shù)現(xiàn)代FPGA都是基于SRAM的,包括Xilinx Spartan和Virtex系列

Xilinx Spartan-6 FPGA協(xié)處理套件演示

Xilinx Spartan-6 FPGA協(xié)處理套件演示

評(píng)論