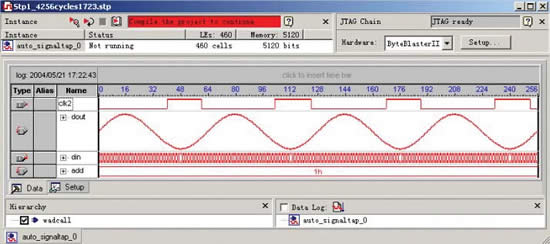

SignalTap II內(nèi)置邏輯分析儀是quartus ii開發(fā)過程中必要的工具,用于抓取工程運行中實際產(chǎn)生的信號。這與modelsim不同,modelsim屬于功能驗證,是“理論上”的波形,而signaltap ii抓取的真實的波形(當(dāng)然也不能保證全對!),是隨著碼流燒錄進(jìn)FPGA然后綜合處一塊區(qū)域為邏輯分析儀。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關(guān)注

關(guān)注

1645文章

22021瀏覽量

617258 -

軟件

+關(guān)注

關(guān)注

69文章

5144瀏覽量

89125 -

工具

+關(guān)注

關(guān)注

4文章

315瀏覽量

28248

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

【鋯石A4 FPGA試用體驗】SignalTap II使用

SignalTapII全稱SignalTap II Logic Analyzer是第二代系統(tǒng)級調(diào)試工具,可以捕獲和顯示實時信號,觀察在系統(tǒng)設(shè)計中的硬件和軟件之間的互相作用。Quartu

發(fā)表于 09-11 23:59

【鋯石A4 FPGA試用體驗】IP核之FIFO(三)SignalTap II仿真

本帖最后由 jinyi7016 于 2016-10-15 15:08 編輯

SignalTap II全稱SignalTap II Logic Analyzer是第二代系統(tǒng)級調(diào)試

發(fā)表于 10-11 22:24

勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載75:基于SignalTap II的超聲波測距調(diào)試之SignalTap II源文件創(chuàng)建

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載75:基于SignalTap II的超聲波測距調(diào)試之SignalTap

發(fā)表于 06-09 21:30

勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載77:基于SignalTap II的超聲波測距調(diào)試之SignalTap II調(diào)試

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載77:基于SignalTap II的超聲波測距調(diào)試之SignalTap

發(fā)表于 06-14 20:10

使用SignalTap II邏輯分析儀調(diào)試FPGA

本文介紹了可編程邏輯器件開發(fā)工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個具體的設(shè)計實例,詳細(xì)介紹使用SignalTap

發(fā)表于 11-01 14:49

?45次下載

使用SignalTap II邏輯分析儀調(diào)試FPGA

摘 要 :本文介紹了可編程邏輯器件開發(fā)工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個具體的設(shè)計實例,詳細(xì)介紹使用SignalTap

發(fā)表于 06-20 10:42

?1783次閱讀

【從零開始走進(jìn)FPGA】 SignalTap II Logic Analyzer

關(guān)鍵詞:FPGA , SignalTap 一、為啥別忘了我 嵌入式邏輯分析儀—SigbalTap II,是Altera Quartus II 自帶的嵌入式邏輯分析儀,與Modelsim

發(fā)表于 10-01 15:30

?1019次閱讀

鋯石FPGA A4_Nano開發(fā)板視頻:SignalTap II軟件使用講解

SignalTap II全稱SignalTap II Logic Analyzer是第二代系統(tǒng)級調(diào)試工具,可以捕獲和顯示實時信號,觀察在系統(tǒng)

正點原子開拓者FPGA視頻:SignalTap II軟件的使用

SignalTap II全稱SignalTap II Logic Analyzer是第二代系統(tǒng)級調(diào)試工具,可以捕獲和顯示實時信號,觀察在系統(tǒng)

如何輕松掌握SignalTAP II工具的使用方法

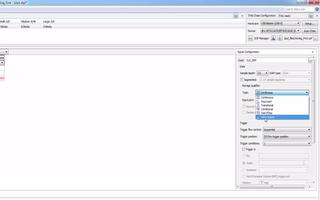

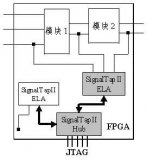

SignalTap II獲取實時數(shù)據(jù)的原理是在工程中引入Megafunction中的ELA(Embedded Logic Analyzer),以預(yù)先設(shè)定的時鐘采樣實時數(shù)據(jù),并存儲于FPGA片上ram

SignalTap II的特點、設(shè)置流程及邏輯分析儀的設(shè)計

伴隨著EDA工具的快速發(fā)展,一種新的調(diào)試工具Quartus II 中的SignalTap II 滿足了F

FPGA之軟件工具篇:SignalTap II軟件使用講解

FPGA之軟件工具篇:SignalTap II軟件使用講解

評論