基于DE1-SOC開發(fā)板的oneAPI實驗教程(1)

在算力需求爆炸式增長的時代,異構(gòu)計算已成為突破性能瓶頸的首選路徑。然而,多架構(gòu)編程困境、傳統(tǒng)硬件開發(fā)....

在友晶LabCloud平臺上使用PipeCNN實現(xiàn)ImageNet圖像分類

利用深度卷積神經(jīng)網(wǎng)絡(luò)(CNN)進行圖像分類是通過使用多個卷積層來從輸入數(shù)據(jù)中提取特征,最后通過分類層....

友晶科技攜手中國地質(zhì)大學(xué)舉辦FPGA硬件在線實驗云平臺公開課

近日,友晶科技攜手中國地質(zhì)大學(xué),成功舉辦了一場FPGA硬件在線實驗云平臺公開課。

SDRAM控制器的設(shè)計——Sdram_Control.v代碼解析(異步FIFO讀寫模塊、讀寫SDRAM過程)

前言 SDRAM控制器里面包含5個主要的模塊,分別是PLL模塊,異步FIFO 寫模塊,異步FIFO讀....

SDRAM控制器設(shè)計之異步FIFO的調(diào)用

為了加深讀者對 FPGA 端控制架構(gòu)的印象,在數(shù)據(jù)讀取的控制部分,首先我們可以將SDRAM 想作是一....

SDRAM控制器設(shè)計之command.v代碼解析

command.v文件對應(yīng)圖中SDRAM指令執(zhí)行模塊,它會從SDRAM接口控制模塊接收指令,然后產(chǎn)生....

SDRAM控制器設(shè)計之control_interface.v代碼解析

control_interface.v文件里已經(jīng)寫了非常詳盡的代碼備注。本文繼續(xù)對該文件代碼進行講解....

基于互聯(lián)網(wǎng)的攝像測量系統(tǒng)(三)

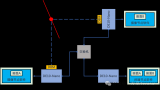

使用HDMI線將三個HDMI顯示器分別連接到攝像節(jié)點A、B和終端節(jié)點DE10-Nano開發(fā)板上的HD....

基于互聯(lián)網(wǎng)的攝像測量系統(tǒng)(二)

攝像節(jié)點由一個DE10-Nano開發(fā)板和一個D8M攝像頭實現(xiàn),DE10-Nano開發(fā)板的HDMI接口....

街機彈球機的模擬設(shè)計實現(xiàn)

該項目是實現(xiàn)經(jīng)典的街機游戲——彈球機。使用DE1-SOC開發(fā)板上的滑動開關(guān),玩家可以設(shè)置球的初始速度....

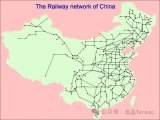

中國鐵路網(wǎng)的Dijkstra算法實現(xiàn)案例

該項目分別在DE1-SOC開發(fā)板的FPGA和HPS上實現(xiàn)了Dijkstra算法,能在中國鐵路網(wǎng)中找到....

基于DE1-SOC的String Art實現(xiàn)

String Art起源于19世紀(jì)的數(shù)學(xué)家Mary Everest Boole的設(shè)計,隨后發(fā)展成一種....