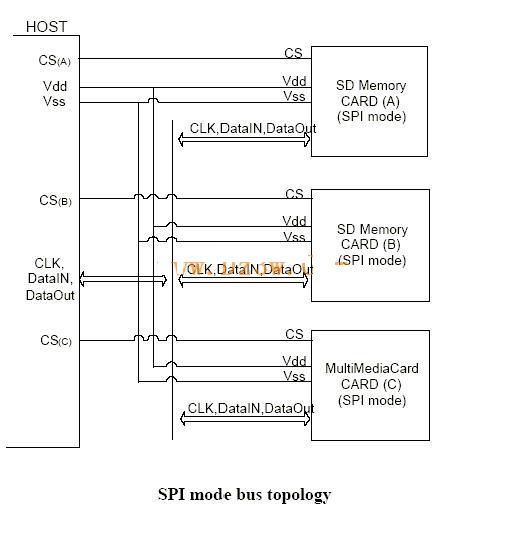

摘要:在一個主機和多個從器件的典型SPI系統(tǒng)中,通常采用專門的片選信號來尋址從器件。隨著從器件數(shù)量不斷增加,片選線也隨之增多。這種情況將給電路板布板帶來很大的挑戰(zhàn)。

一個布板方法就是采用菊鏈結構。本文詳細講述了SPI系統(tǒng)的菊鏈配置,并展示如何使用軟件向串聯(lián)從器件發(fā)送命令。

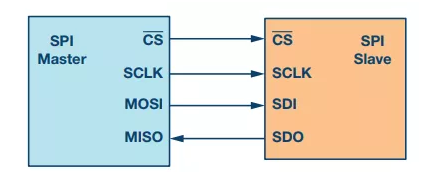

標準SPI?/QSPI?/MICROWIRE?兼容微控制器通過3線/4線串口與從器件通信。典型接口包括片選信號(/CS)、串行時鐘(SCLK)和數(shù)據(jù)輸入信號(DIN),有時還會有數(shù)據(jù)輸出信號(DOUT)。如同I2C系統(tǒng)中一樣,單獨尋址的器件能輕易的和總線上的其它器件通信。

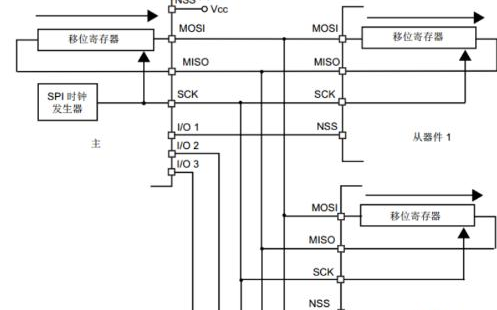

圖1. 帶有多個從器件獨立片選信號的微控制器。

在上述系統(tǒng)中,微控制器通過一個串行時鐘輸出(SCLK)和一個主機輸出/從機輸入(MOSI)信號線向各從器件發(fā)送命令。主機為每個器件分配了一個獨立的片選信號(/SS_),從而實現(xiàn)各個從器件的獨立尋址。由于所有從器件共享同一個時鐘和數(shù)據(jù)線,只有/CS輸入變低的從器件才會應答串行時鐘和數(shù)據(jù)線。當從器件數(shù)目較少時,該系統(tǒng)較易實現(xiàn)。如果系統(tǒng)中從器件數(shù)較多,微控制器需要提供和從器件一樣多的/SS_輸出,這種結構就增加了硬件和布板的復雜程度。

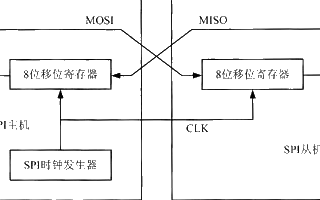

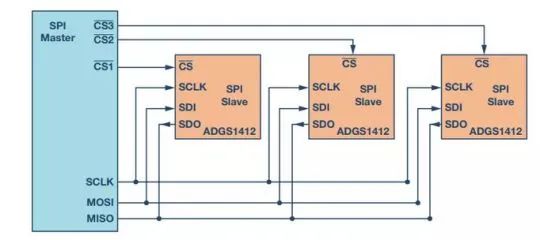

圖2. 微控制器連接多個從器件

采用一個/SS (或者/CS)信號控制所有從器件的/CS輸入;所有從器件接收同一個時鐘信號。只有鏈上的第一個從器件(SLAVE 1)從微控制器直接接收命令。其他所有從器件都從鏈上前一個器件的DOUT輸出獲得其DIN數(shù)據(jù)。

要保證菊鏈正常工作,每一個從器件就必須能在給定的命令周期內(定義為每一個命令所需的時鐘數(shù))從DIN引腳讀入命令,而在下一個命令周期從DOUT引腳輸出同樣的命令。顯然,從DIN到DOUT會有一個命令周期的延遲。另外,各個從器件只能在/CS的上升沿執(zhí)行寫入的命令。這意味著只要/CS保持低電平,從器件將不會執(zhí)行命令,并且會在下一個命令周期將命令通過DOUT引腳輸出。如果在給定命令周期之后/CS變高,所有從器件將立即執(zhí)行寫入DIN引腳的命令。如果/CS變高,數(shù)據(jù)將不會從DOUT輸出,這就使得鏈上每個從器件可以執(zhí)行不同的命令。只要菊鏈的這些要求能夠滿足,微控制器只需三個信號(/SS、SCK和MOSI)就能控制網(wǎng)絡上的所有從器件。

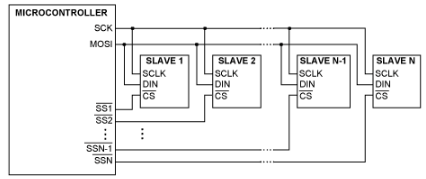

圖3. 菊鏈電路#1

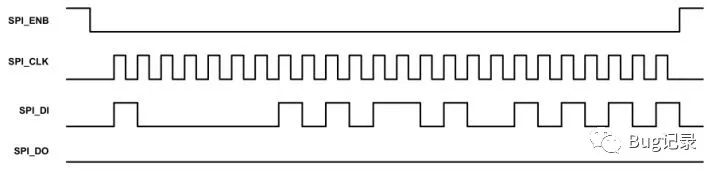

圖4給出了將IC1 (A1和B1)、IC2 (A2和B2)和IC3 (A3和B3)的輸出分別設為零點、中點和滿刻度的命令序列圖。在這個例子中,使用了以下的命令:

圖4. 電路#1—命令時序A

在第一個命令周期(16個SCLK脈沖序列),將0x7FF8載入IC1的移位寄存器。當/CS保持低電平,這一數(shù)據(jù)將在IC1內傳遞,并且在下一個命令周期內通過DOUT1輸出。在第二個命令周期內,IC1輸出端DOUT1上的數(shù)據(jù)輸入到DIN2,將0x7FF8載入IC2的移位寄存器中。同時,新的命令0x7000將載入IC1移位寄存器,覆蓋了前一個命令。

第三個命令周期內,第一個命令0x7FF8將載入IC3的移位寄存器,而第二個命令0x7000將載入IC2的移位寄存器,同時IC1將接收到新的命令0x6000。此時,三個IC都從菊鏈上接收到命令并存儲在他們的移位寄存器中。一旦/CS變高,將執(zhí)行已存儲的命令;A1和B1被設為零點、A2和B2被設為中點、A3和B3被設為滿刻度。

圖5給出了更為復雜的命令序列。在這個例子中,使用以下的命令(更多詳細信息,請參考MAX5233數(shù)據(jù)資料):

圖5. 電路#1—命令序列B

在第一個三命令周期內,菊鏈上三個IC中的各個器件的移位寄存器軍接收到一條命令。IC1、IC2、IC3接收到的命令分別為0xB000、0xBFF8和0xBFF8。 器件將在/CS的上升沿執(zhí)行這些命令(第一次執(zhí)行)。執(zhí)行完之后,IC1、IC2、IC3的輸入寄存器B中分別加載了中點、滿刻度和滿刻度的數(shù)據(jù)。此時,由于各IC的DAC寄存器B保持不變,因此B1、B2、B3均未改變。

在接下來的三命令周期內,每個IC的移位寄存器中均寫入了僅向輸入寄存器A加載數(shù)據(jù)的命令。DAC寄存器A和輸出保持不變。在/CS的上升沿,IC1、IC2、IC3的輸入寄存器A分別加載了滿刻度、零點和中點數(shù)據(jù)。此時,由于只更新了輸入寄存器A而不是DAC寄存器A,因此A1、A2、A3均保持不變。

在第二次執(zhí)行命令之后,硬件/LDAC命令(驅動/LDAC為低)將輸入寄存器中的數(shù)據(jù)加載到相應的DAC寄存器中。這樣,DAC的輸出就被刷新為相應的DAC寄存器中的數(shù)據(jù)。A1、B2和B3變?yōu)闈M刻度。A2變?yōu)榱泓c而A3仍為中點狀態(tài)。

在第三個命令周期,IC2和IC3接收了空操作命令(0x0000),而IC1接收0xA000命令,將零點數(shù)據(jù)加載到IC1的輸入寄存器B。第三次執(zhí)行命令之后,所有的輸出仍舊沒有改變。

在第四個命令周期內,IC1和IC2接收空操作命令,而IC3接收到0x3FF8命令。第四次執(zhí)行命令之后,IC3的輸入寄存器A加載滿刻度數(shù)據(jù)。另一個硬件/LDAC命令將輸入寄存器的數(shù)據(jù)加載到相應DAC寄存器。這將使B1從中點變?yōu)榱泓c,A3從中點變?yōu)闈M刻度。其他的輸出仍舊不變。

表1. 命令序列B中,上電后以及執(zhí)行硬件/LDAC命令后,IC1、IC2和IC3的輸出狀態(tài)

圖6. 菊鏈電路#2

圖7給出了命令序列示例,使用了以下的命令(更多詳細信息請見MAX5290數(shù)據(jù)資料)。

圖7. 電路#2命令時序示例

器件在/CS上升沿時執(zhí)行已經加載到每個器件移位寄存器中的命令。第一次執(zhí)行命令后,所有DAC輸出均刷新。IC1的DAC輸出為零點,IC2的DAC輸出為中點,而IC3的DAC輸出為滿刻度。

第二個命令周期時,執(zhí)行命令0xE400,IC2的DAC的A和B輸出都進入關斷模式。IC1和IC3由于執(zhí)行空操作命令而不受影響。第三個命令周期后,IC1的輸出變?yōu)闈M刻度,IC3的輸出變?yōu)榱泓c。而IC2的輸出仍處于關斷模式,其內部輸入寄存器和DAC寄存器數(shù)據(jù)已被刷新。在最后的命令周期,IC2恢復正常工作模式,所有輸出變?yōu)闈M刻度。

表2. 命令序列示例中,上電后和執(zhí)行命令后,IC1、IC2、IC3的輸出狀態(tài)

一個布板方法就是采用菊鏈結構。本文詳細講述了SPI系統(tǒng)的菊鏈配置,并展示如何使用軟件向串聯(lián)從器件發(fā)送命令。

標準SPI?/QSPI?/MICROWIRE?兼容微控制器通過3線/4線串口與從器件通信。典型接口包括片選信號(/CS)、串行時鐘(SCLK)和數(shù)據(jù)輸入信號(DIN),有時還會有數(shù)據(jù)輸出信號(DOUT)。如同I2C系統(tǒng)中一樣,單獨尋址的器件能輕易的和總線上的其它器件通信。

基本串行通信接口

很多SPI器件并不是單獨尋址的。因此,這些器件和總線上其它單個器件通信時,就需要進行額外的硬件或者軟件處理。圖1所示是一個微控制器和多個從器件通信的系統(tǒng)。

圖1. 帶有多個從器件獨立片選信號的微控制器。

在上述系統(tǒng)中,微控制器通過一個串行時鐘輸出(SCLK)和一個主機輸出/從機輸入(MOSI)信號線向各從器件發(fā)送命令。主機為每個器件分配了一個獨立的片選信號(/SS_),從而實現(xiàn)各個從器件的獨立尋址。由于所有從器件共享同一個時鐘和數(shù)據(jù)線,只有/CS輸入變低的從器件才會應答串行時鐘和數(shù)據(jù)線。當從器件數(shù)目較少時,該系統(tǒng)較易實現(xiàn)。如果系統(tǒng)中從器件數(shù)較多,微控制器需要提供和從器件一樣多的/SS_輸出,這種結構就增加了硬件和布板的復雜程度。

菊鏈方法

硬件空間方面的限制往往會使圖1所示的電路無法實現(xiàn)或難以實現(xiàn)。可采用菊鏈法替代實現(xiàn)串行接口。圖2是一個有N個從器件的菊鏈系統(tǒng)結構。

圖2. 微控制器連接多個從器件

采用一個/SS (或者/CS)信號控制所有從器件的/CS輸入;所有從器件接收同一個時鐘信號。只有鏈上的第一個從器件(SLAVE 1)從微控制器直接接收命令。其他所有從器件都從鏈上前一個器件的DOUT輸出獲得其DIN數(shù)據(jù)。

要保證菊鏈正常工作,每一個從器件就必須能在給定的命令周期內(定義為每一個命令所需的時鐘數(shù))從DIN引腳讀入命令,而在下一個命令周期從DOUT引腳輸出同樣的命令。顯然,從DIN到DOUT會有一個命令周期的延遲。另外,各個從器件只能在/CS的上升沿執(zhí)行寫入的命令。這意味著只要/CS保持低電平,從器件將不會執(zhí)行命令,并且會在下一個命令周期將命令通過DOUT引腳輸出。如果在給定命令周期之后/CS變高,所有從器件將立即執(zhí)行寫入DIN引腳的命令。如果/CS變高,數(shù)據(jù)將不會從DOUT輸出,這就使得鏈上每個從器件可以執(zhí)行不同的命令。只要菊鏈的這些要求能夠滿足,微控制器只需三個信號(/SS、SCK和MOSI)就能控制網(wǎng)絡上的所有從器件。

如何實現(xiàn)菊鏈

在菊鏈系統(tǒng)中(圖2),SLAVE 1從微控制器直接接收數(shù)據(jù)。該數(shù)據(jù)在時鐘驅動下進入SLAVE 1的內部移位寄存器。只要/CS (或/SS)仍然保持低電平,該數(shù)據(jù)將通過SLAVE 1的DOUT引腳輸出。SLAVE 1的DOUT引腳接至SLAVE 2的DI引腳,因此當數(shù)據(jù)通過SLAVE 1的DOUT引腳端輸出時,同時也被同步移入SLAVE 2的內部移位寄存器。同理,當SLAVE 2接收來自SLAVE 1的數(shù)據(jù)的時候,微控制器可同時向SLAVE 1發(fā)送另一個命令。該新命令將覆蓋SLAVE 1移位寄存器中原來的數(shù)據(jù)。只要/CS保持為低,數(shù)據(jù)會在整條菊鏈上傳遞,直到每一個從器件都接收了相應的命令。存儲在每一個從器件移位寄存器中的命令將在/CS的上升沿執(zhí)行。下面例子使用MAX5233和MAX5290構成菊鏈。電路圖范例#1

圖3給出的菊鏈結構中連接了3個MAX5233。MAX5233為雙路、10位DAC (包含兩個DAC通道,通道A和B)。將RSTV接至VDD,模擬輸出的上電狀態(tài)被設置到中點。

圖3. 菊鏈電路#1

圖4給出了將IC1 (A1和B1)、IC2 (A2和B2)和IC3 (A3和B3)的輸出分別設為零點、中點和滿刻度的命令序列圖。在這個例子中,使用了以下的命令:

- 0x7FF8—將滿刻度數(shù)據(jù)加載到IC3 DAC寄存器,并將兩路輸出(A3、B3)設置到滿刻度

- 0x7000—將滿刻度數(shù)據(jù)加載到IC2 DAC寄存器,并將兩路輸出(A2、B2)設置到中點

- 0x6000—將滿刻度數(shù)據(jù)加載到IC1 DAC寄存器,并將兩路輸出(A1、B1)設置到零點

圖4. 電路#1—命令時序A

在第一個命令周期(16個SCLK脈沖序列),將0x7FF8載入IC1的移位寄存器。當/CS保持低電平,這一數(shù)據(jù)將在IC1內傳遞,并且在下一個命令周期內通過DOUT1輸出。在第二個命令周期內,IC1輸出端DOUT1上的數(shù)據(jù)輸入到DIN2,將0x7FF8載入IC2的移位寄存器中。同時,新的命令0x7000將載入IC1移位寄存器,覆蓋了前一個命令。

第三個命令周期內,第一個命令0x7FF8將載入IC3的移位寄存器,而第二個命令0x7000將載入IC2的移位寄存器,同時IC1將接收到新的命令0x6000。此時,三個IC都從菊鏈上接收到命令并存儲在他們的移位寄存器中。一旦/CS變高,將執(zhí)行已存儲的命令;A1和B1被設為零點、A2和B2被設為中點、A3和B3被設為滿刻度。

圖5給出了更為復雜的命令序列。在這個例子中,使用以下的命令(更多詳細信息,請參考MAX5233數(shù)據(jù)資料):

- 0x3FF8—將滿刻度數(shù)據(jù)加載到輸入寄存器A,不改變DAC寄存器和輸出

- 0x3000—將中點數(shù)據(jù)加載到輸入寄存器A,不改變DAC寄存器和輸出

- 0x2000—將零點數(shù)據(jù)加載到輸入寄存器A,不改變DAC寄存器和輸出

- 0xBFF8—將滿刻度數(shù)據(jù)加載到輸入寄存器B,不改變DAC寄存器和輸出

- 0xB000—將中點數(shù)據(jù)加載到輸入寄存器B,不改變DAC寄存器和輸出

- 0xA000—將零點數(shù)據(jù)加載到輸入寄存器B,不改變DAC寄存器和輸出

- 0x0000—空操作

圖5. 電路#1—命令序列B

在第一個三命令周期內,菊鏈上三個IC中的各個器件的移位寄存器軍接收到一條命令。IC1、IC2、IC3接收到的命令分別為0xB000、0xBFF8和0xBFF8。 器件將在/CS的上升沿執(zhí)行這些命令(第一次執(zhí)行)。執(zhí)行完之后,IC1、IC2、IC3的輸入寄存器B中分別加載了中點、滿刻度和滿刻度的數(shù)據(jù)。此時,由于各IC的DAC寄存器B保持不變,因此B1、B2、B3均未改變。

在接下來的三命令周期內,每個IC的移位寄存器中均寫入了僅向輸入寄存器A加載數(shù)據(jù)的命令。DAC寄存器A和輸出保持不變。在/CS的上升沿,IC1、IC2、IC3的輸入寄存器A分別加載了滿刻度、零點和中點數(shù)據(jù)。此時,由于只更新了輸入寄存器A而不是DAC寄存器A,因此A1、A2、A3均保持不變。

在第二次執(zhí)行命令之后,硬件/LDAC命令(驅動/LDAC為低)將輸入寄存器中的數(shù)據(jù)加載到相應的DAC寄存器中。這樣,DAC的輸出就被刷新為相應的DAC寄存器中的數(shù)據(jù)。A1、B2和B3變?yōu)闈M刻度。A2變?yōu)榱泓c而A3仍為中點狀態(tài)。

在第三個命令周期,IC2和IC3接收了空操作命令(0x0000),而IC1接收0xA000命令,將零點數(shù)據(jù)加載到IC1的輸入寄存器B。第三次執(zhí)行命令之后,所有的輸出仍舊沒有改變。

在第四個命令周期內,IC1和IC2接收空操作命令,而IC3接收到0x3FF8命令。第四次執(zhí)行命令之后,IC3的輸入寄存器A加載滿刻度數(shù)據(jù)。另一個硬件/LDAC命令將輸入寄存器的數(shù)據(jù)加載到相應DAC寄存器。這將使B1從中點變?yōu)榱泓c,A3從中點變?yōu)闈M刻度。其他的輸出仍舊不變。

表1. 命令序列B中,上電后以及執(zhí)行硬件/LDAC命令后,IC1、IC2和IC3的輸出狀態(tài)

| ? | Analog Output Name |

| ||

| After Power-Up (RSTV = VDD) | First Hardware Active-Low LDAC | Second Hardware Active-Low LDAC | ||

| IC1 | A1 | Midscale | Full scale | Full scale |

| B1 | Midscale | Midscale | Zero scale | |

| IC2 | A2 | Midscale | Zero scale | Zero scale |

| B2 | Midscale | Full scale | Full scale | |

| IC3 | A3 | Midscale | Midscale | Full scale |

| B3 | Midscale | Full scale | Full scale | |

電路范例#2

圖6給出的菊鏈結構中有三個MAX5290 (雙路12位DAC)。將PU接至DVDD,則上電時模擬輸出設置為滿刻度。MAX5290沒有專用于菊鏈的數(shù)字輸出。因此,需通過串口將兩個UPIO (用戶可編程輸入/輸出)引腳中的任意一個編程設置為DOUTDC_模式。更多詳細信息請見MAX5290數(shù)據(jù)資料。

圖6. 菊鏈電路#2

圖7給出了命令序列示例,使用了以下的命令(更多詳細信息請見MAX5290數(shù)據(jù)資料)。

- 0xDFFF—將滿刻度數(shù)據(jù)加載到所有輸入寄存器和DAC寄存器,刷新DAC的A和B輸出

- 0xD800—將中點數(shù)據(jù)加載到所有輸入寄存器和DAC寄存器,刷新DAC的A和B輸出

- 0xD000—將零點數(shù)據(jù)加載到所有輸入寄存器和DAC寄存器,刷新DAC的A和B輸出

- 0xE400—將DAC的A和B輸出置于關斷模式

- 0xE40F—使DAC的A和B輸出跳出關斷模式

- 0xFFFF—空操作

圖7. 電路#2命令時序示例

器件在/CS上升沿時執(zhí)行已經加載到每個器件移位寄存器中的命令。第一次執(zhí)行命令后,所有DAC輸出均刷新。IC1的DAC輸出為零點,IC2的DAC輸出為中點,而IC3的DAC輸出為滿刻度。

第二個命令周期時,執(zhí)行命令0xE400,IC2的DAC的A和B輸出都進入關斷模式。IC1和IC3由于執(zhí)行空操作命令而不受影響。第三個命令周期后,IC1的輸出變?yōu)闈M刻度,IC3的輸出變?yōu)榱泓c。而IC2的輸出仍處于關斷模式,其內部輸入寄存器和DAC寄存器數(shù)據(jù)已被刷新。在最后的命令周期,IC2恢復正常工作模式,所有輸出變?yōu)闈M刻度。

表2. 命令序列示例中,上電后和執(zhí)行命令后,IC1、IC2、IC3的輸出狀態(tài)

| ? | Analog Output Name |

| ||||

| After Power-Up (PU = VDD) | After First Excution | After Second Execution | After Third Execution | After Fourth Execution | ||

| IC1 | A1 | Full scale | Zero scale | Zero scale | Full scale | Full scale |

| B1 | Full scale | Zero scale | Zero scale | Full scale | Full scale | |

| IC2 | A2 | Full scale | Midscale | Shutdown | Shutdown | Full scale |

| B2 | Full scale | Midscale | Shutdown | Shutdown | Full scale | |

| IC3 | A3 | Full scale | Full scale | Full scale | Zero scale | Zero scale |

| B3 | Full scale | Full scale | Full scale | Zero scale | Zero scale | |

電子發(fā)燒友App

電子發(fā)燒友App

評論