AD9510 1.2 GHz時鐘分配IC,PLL內(nèi)核,分頻器,延遲調(diào)整,8路輸出

數(shù)據(jù):

AD9510產(chǎn)品技術(shù)英文資料手冊

優(yōu)勢和特點

- 鎖相環(huán)(PLL)內(nèi)核

參考輸入頻率達250 MHz

可編程雙模預分頻器

可編程電荷泵(CP)電流

獨立的CP電源(VCP)可擴展調(diào)整范圍 - 兩路1.6 GHz差分時鐘輸入

- 8 個可編程分頻器,1至32整數(shù)分頻比

- 用于輸出到輸出延遲粗調(diào)的相位選擇

- 4路獨立的1.2 GHz LVPECL輸出

加性輸出抖動:225 fs RMS - 4路獨立的800 MHz/250 MHz LVDS/CMOS輸出

加性輸出抖動:275 fs RMS

2路輸出提供延遲精調(diào),5位延遲字 - 串行控制端口

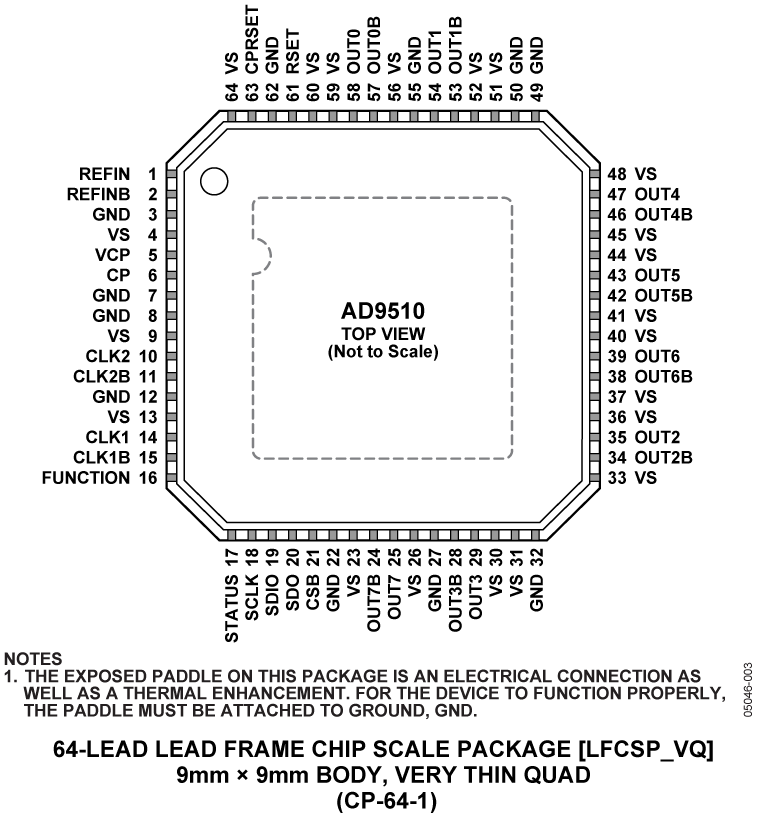

- 節(jié)省空間的64引腳LFCSP封裝

產(chǎn)品詳情

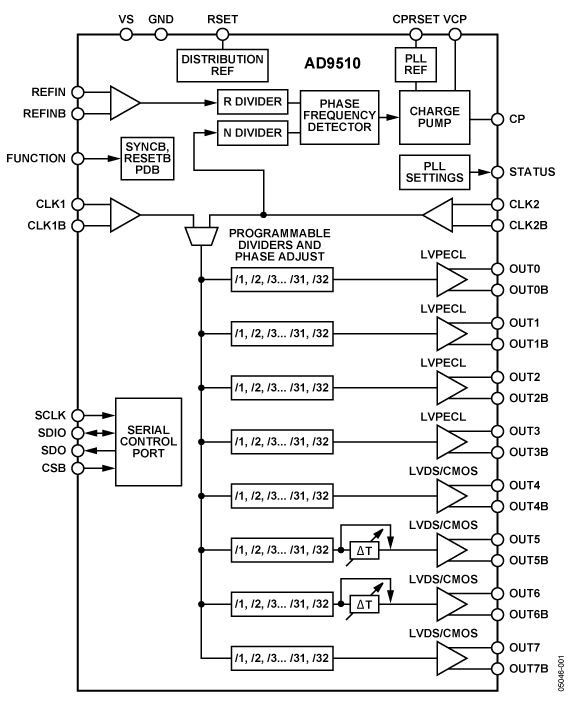

AD9510提供多路輸出時鐘分配功能,并集成一個片內(nèi)鎖相環(huán)(PLL)內(nèi)核。它具有低抖動和低相位噪聲特性,能夠極大地提升數(shù)據(jù)轉(zhuǎn)換器的時鐘性能。4路獨立的LVPECL時鐘輸出和4路LVDS時鐘輸出工作頻率分別為1.2 GHz和800 MHz。可選的CMOS時鐘輸出工作頻率為250 MHz。

PLL部分由可編程參考分頻器(R)、低噪聲鑒頻鑒相器(PFD)、精密電荷泵(CP)和可編程反饋分頻器(N)組成。將外部VCXO或VCO連接到CLK2和CLK2B引腳時,最高達1.6 GHz的PLL輸出頻率可以與輸入?yún)⒖糝EFIN同步。

時鐘分配部分提供LVPECL輸出和可編程為LVDS或CMOS的輸出。每路輸出都有一個可編程分頻器,可以旁路該分頻器或者設置最高32的整數(shù)分頻比。

用戶可以通過各分頻器改變一路時鐘輸出相對于其它時鐘輸出的相位,這種相位選擇功能可用于時序粗調(diào)。某些輸出還提供可編程延遲特性,具有最長10 ns的用戶可選滿量程延遲值。該精調(diào)延遲模塊通過一個5位字進行編程,提供32個可用的延遲時間供用戶選擇。

AD9510非常適合數(shù)據(jù)轉(zhuǎn)換器時鐘應用,利用亞皮秒抖動編碼信號,可實現(xiàn)最佳的轉(zhuǎn)換器性能。

AD9510提供64引腳LFCSP封裝,額定溫度范圍為-40°C至+85°C,可以采用3.3 V單電源供電。如果用戶希望擴展外部VCO的電壓范圍,可以利用最高達5.5V的電荷泵電源VCP。

應用

- 低抖動、低相位噪聲時鐘分配

- 為高速ADC、DAC、DDS、DDC、DUC、MxFE?轉(zhuǎn)換器提供時鐘

- 無線基礎設施收發(fā)器

- 高性能儀器儀表

- 寬帶基礎設施

方框圖