完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > 賽靈思

提供賽靈思公司最新的技術(shù)和產(chǎn)品信息,工程師最喜歡的賽靈思技術(shù)社區(qū)

文章:1699個(gè) 瀏覽:132179次 帖子:56個(gè)

適用于Zynq-7000 All Programmable SoC的模擬混合信號工具

了解適用于Zynq-7000 All Programmable SoC的模擬混合信號工具。 此培訓(xùn)將幫助您了解核心AMS功能,集成模擬的優(yōu)勢以及可用A...

Zynq-7000 SoC ZC702 評估套件產(chǎn)品描述

Zynq-7000 SoC ZC702 評估套件包含硬件、設(shè)計(jì)工具、IP 核 以及預(yù)驗(yàn)證參考設(shè)計(jì)的所有基本元件,包括可實(shí)現(xiàn)完整嵌入式處理平臺的目標(biāo)設(shè)計(jì)。...

2019-07-31 標(biāo)簽:賽靈思硬件設(shè)計(jì)工具 2901 0

本視頻介紹了Xilinx的28nm,20nm和16nm FPGA和MPSoC在2016年和2017年初發(fā)生的2D標(biāo)記變化。 本概述提供了有用的信息,包...

賽靈思FPGA卷積神經(jīng)網(wǎng)絡(luò),云中的機(jī)器學(xué)習(xí)

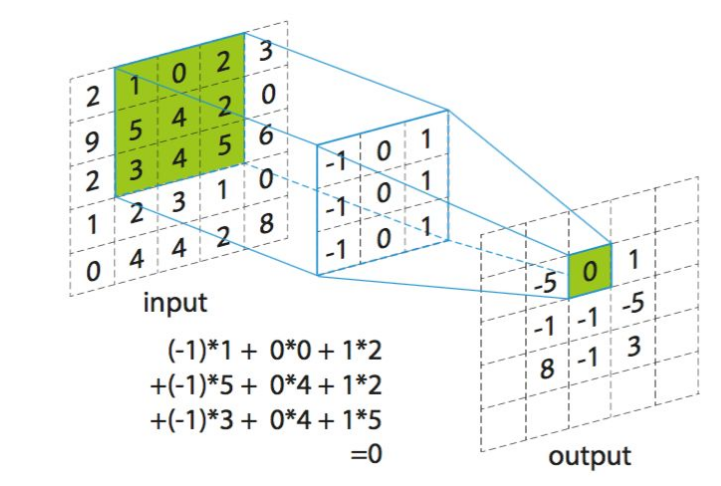

人工智能正在經(jīng)歷一場變革,這要得益于機(jī)器學(xué)習(xí)的快速進(jìn)步。在機(jī)器學(xué)習(xí)領(lǐng)域,人們正對一類名為“深度學(xué)習(xí)”算法產(chǎn)生濃厚的興趣,因?yàn)檫@類算法具有出色的大數(shù)據(jù)集...

2018-07-11 標(biāo)簽:FPGA賽靈思機(jī)器學(xué)習(xí) 2891 0

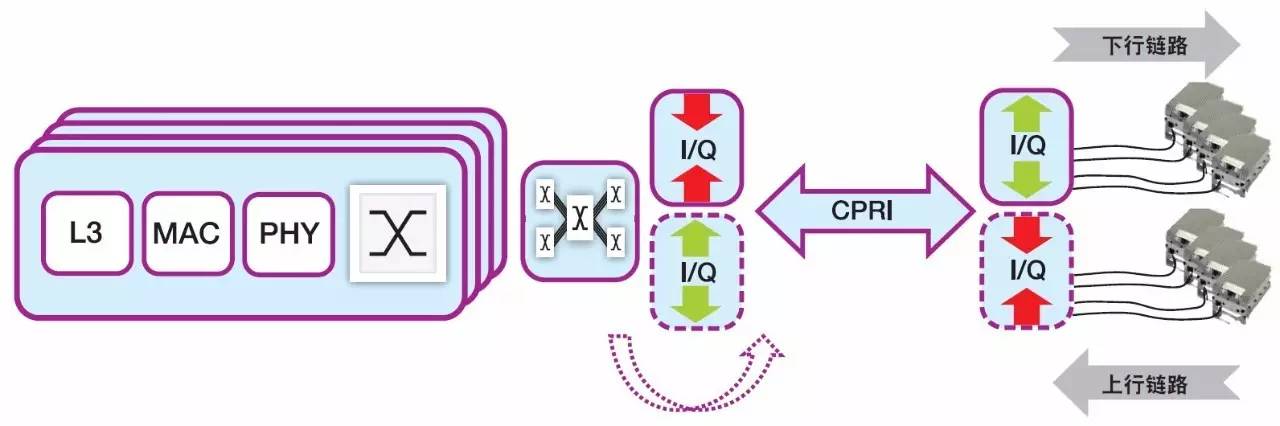

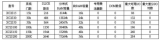

賽靈思的Vivado HLS工具有助于降低無線去程網(wǎng)絡(luò)基礎(chǔ)設(shè)施的成本

非線性量化 (NLQ) 過程將正態(tài)分布的 15 位基帶 IQ 樣本轉(zhuǎn)化為 10 位量化值。NLQ 使用具有指定標(biāo)準(zhǔn)偏差的累積分布函數(shù) (CDF) 來描述...

用于Zynq微處理器和可編程邏輯的新型操作系統(tǒng)Dyplo介紹

Xilinx的Dave Tokic與Topic Embedded Systems的創(chuàng)始人兼首席執(zhí)行官Rieny Rijnen進(jìn)行了交談,他描述了Dypl...

2018-11-30 標(biāo)簽:賽靈思操作系統(tǒng)微處理器 2887 0

了解有關(guān)設(shè)備樹的背景信息,各種類型的u-boot映像及其功能以及有關(guān)使用的內(nèi)容。 除了dumpimage工具從圖像中提取組件。

訪問集成Xilinx模數(shù)轉(zhuǎn)換器的三種方法介紹

了解訪問集成Xilinx模數(shù)轉(zhuǎn)換器(XADC)的三種方法; 通過直接連接到PS,作為PS或Microblaze的AXI外設(shè),或作為邏輯的IP核。

2018-11-20 標(biāo)簽:賽靈思ip模數(shù)轉(zhuǎn)換器 2872 0

強(qiáng)化DPD演算效能 SoC FPGA提升蜂巢網(wǎng)絡(luò)設(shè)備整合度

蜂巢式網(wǎng)絡(luò)業(yè)者設(shè)法透過全新傳輸界面、傳輸頻率、更高頻寬以及增加天線的數(shù)量和更多無線基地臺提升網(wǎng)絡(luò)密度,因此須要大幅降低設(shè)備的成本。另外,這些業(yè)者為降低營...

2013-09-16 標(biāo)簽:FPGA賽靈思無線網(wǎng)絡(luò) 2872 0

了解Xilinx的VC730 OTN測試開發(fā)平臺,適用于從1到400G的所有OTN應(yīng)用的快速開發(fā)。

如何使用Carnegie Robotics 3D傳感器降低計(jì)算量

Carnegie Robotics的產(chǎn)品使無人機(jī)器人能夠感知和理解3D信息,從而使系統(tǒng)在工業(yè)和農(nóng)??業(yè)等領(lǐng)域的未知環(huán)境中安全有效地運(yùn)行.Xilinx F...

在Artix A35T Arty評估套件評估Xilinx的AMS技術(shù)

了解如何使用內(nèi)置IPI且無任何HDL的簡單但功能強(qiáng)大的設(shè)計(jì),快速輕松地在Artix A35T Arty評估套件上快速輕松地評估Xilinx的模擬混合信號...

如何快速地創(chuàng)建圖像處理流水線,實(shí)時(shí)檢測運(yùn)動物體

這段視頻中,我們將向您演示如何快速地創(chuàng)建一個(gè)簡單的圖像處理流水線,實(shí)時(shí)檢測運(yùn)動物體。把運(yùn)動物體邊緣勾勒并實(shí)時(shí)地插入到視頻流中,視頻幀速是1080p每秒6...

reVISION堆棧為視覺導(dǎo)向應(yīng)用鋪路

全新的reVISION?堆棧能夠支持更廣泛的沒有或者很少硬件設(shè)計(jì)專業(yè)知識的嵌入式軟件和系統(tǒng)工程師,使其也可以使用賽靈思技術(shù)更輕松,更快速地開發(fā)視覺導(dǎo)向的...

2018-11-22 標(biāo)簽:賽靈思無人機(jī)增強(qiáng)現(xiàn)實(shí) 2851 0

借助FPGA開發(fā)SoC原型制作平臺(Xilinx的Zynq為例)

對于使用安謀國際(ARM)處理器的系統(tǒng)單芯片(SoC)設(shè)計(jì)者而言,在原型制作的階段經(jīng)常會面臨如何整合處理器的問題。本文以賽靈思(Xilinx)的Zynq...

1984年,賽靈思發(fā)明了現(xiàn)場可編程門陣列(FPGA),同時(shí)它成為全球首家無晶圓半導(dǎo)體公司的鼻祖,賽靈思通過不斷應(yīng)用尖端技術(shù)來長久保持它的行業(yè)領(lǐng)袖地位:賽...

Zynq-7000 AP SoC提供業(yè)經(jīng)驗(yàn)證的IP及參考設(shè)計(jì)

Xilinx為Zynq-7000 SoC提供了一個(gè)穩(wěn)健而廣泛的支持基礎(chǔ),讓用戶基于Zynq的開發(fā)設(shè)計(jì)更加高效,同時(shí)也幫助客戶更快地把設(shè)計(jì)推向市場.Zyn...

PCI Express IP設(shè)計(jì)的過程與仿真介紹

了解在啟用PIPE模式的情況下創(chuàng)建PCI Express IP設(shè)計(jì)的過程,以便可以使用Mentor Graphics Questa Verificati...

實(shí)時(shí)視頻引擎OZ 745開發(fā)平臺演示

Omnitek總裁Michael Hodson演示了基于Zynq 7045 AP SoC的可擴(kuò)展視頻流水線和實(shí)時(shí)視頻引擎OZ 745開發(fā)平臺。

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |