完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > 阻抗

阻抗是表示元件性能或一段電路電性能的物理量。交流電路中一段無源電路兩端電壓峰值(或有效值)Um與通過該電路電流峰值(或有效值)Im之比稱為阻抗

文章:759個(gè) 瀏覽:47115次 帖子:768個(gè)

眾所周知,阻抗控制是我們做高速設(shè)計(jì)最基本的原則,各大板廠在PCB加工也會(huì)保證10%左右的阻抗誤差。看似那么輕松的一個(gè)板廠的承諾,要是出現(xiàn)了阻抗在誤差范圍...

PCB設(shè)計(jì):網(wǎng)絡(luò)分析儀測(cè)試DUT出現(xiàn)2個(gè)差不多的阻抗?

用網(wǎng)絡(luò)分析儀測(cè)試DUT的兩個(gè)通道,發(fā)現(xiàn)駐波比差很多,第一反應(yīng)是兩個(gè)通道的阻抗一致性是不是沒做好,打開阻抗測(cè)試界面,結(jié)果顯示兩個(gè)通道的阻抗差不多,而且滿足...

2021-03-24 標(biāo)簽:pcb阻抗網(wǎng)絡(luò)分析儀 3330 0

PCB線路板生產(chǎn)會(huì)造成哪些偏差?層偏對(duì)阻抗的影響

trace在板上常常需要穿過密集的過孔區(qū)域,比如BGA區(qū)域、連接器區(qū)域,此時(shí)trace離過孔的距離就受到限制,不是你想遠(yuǎn)離就能遠(yuǎn)離的,我們常說此處的布線...

線寬要按50或者100歐姆設(shè)計(jì),差分線要做等長(zhǎng),電源走線要粗一點(diǎn),電源地平面最好緊耦合等等這些PCB設(shè)計(jì)的常規(guī)操作相信沒人質(zhì)疑。那么對(duì)于走線包地要打孔,...

2021-03-29 標(biāo)簽:阻抗 9494 0

我們?nèi)CB板廠轉(zhuǎn)一圈,問他們:走線可以幫我們控10%的阻抗公差嗎?他們會(huì)自信滿滿的答應(yīng)你:沒問題!如果你想再摳一下,控8%,他們會(huì)稍微考慮下,也拍板說...

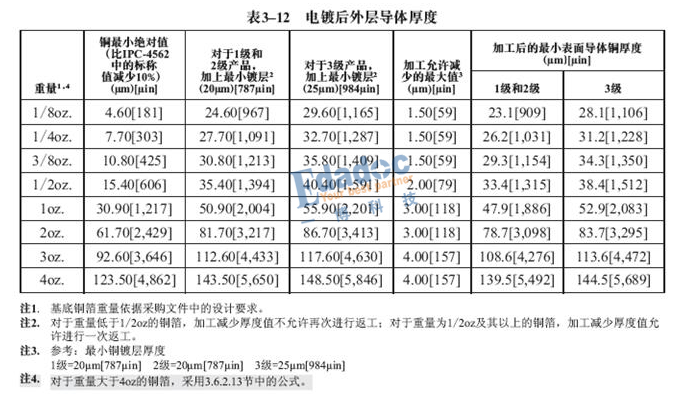

我引用了IPC對(duì)銅箔厚度偏差的定義,我們來回顧一下: 提取內(nèi)層0.5oz的數(shù)據(jù)來簡(jiǎn)單做個(gè)描述:這也是多層板層疊中的常見內(nèi)層厚度 內(nèi)層0.5oz的銅箔正常...

2021-03-31 標(biāo)簽:阻抗多層板PCB設(shè)計(jì) 1.2萬(wàn) 0

首先看一個(gè)真實(shí)的故事:H公司的某網(wǎng)絡(luò)產(chǎn)品,PCB一直在A板廠生產(chǎn),產(chǎn)品測(cè)試一直沒有什么問題。量產(chǎn)的時(shí)候,由于供應(yīng)鏈需要雙供應(yīng)商備份,就嘗試找了B板廠進(jìn)行...

2021-03-31 標(biāo)簽:阻抗數(shù)字信號(hào)DDR4 3997 0

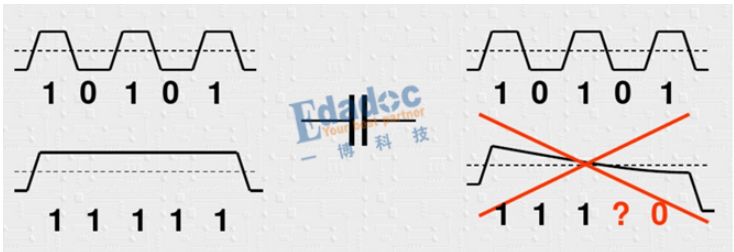

對(duì)高速信號(hào)8B/10B編碼的初步認(rèn)識(shí)

在高速鏈路中導(dǎo)致接收端眼圖閉合的原因,很大部分并不是由于高頻的損耗太大了,而是由于高低頻的損耗差異過大,導(dǎo)致碼間干擾嚴(yán)重,因此不能張開眼睛。針對(duì)這種情況...

FLY-BY拓?fù)浣Y(jié)構(gòu):阻抗不連續(xù)到了什么程度呢

信號(hào)通道中只要有分叉就會(huì)存在阻抗的不連續(xù),fly-by結(jié)構(gòu)處處是分叉,阻抗不連續(xù)問題就很突出,到底這種阻抗不連續(xù)到了什么程度呢?

2021-04-11 標(biāo)簽:DDR3阻抗拓?fù)浣Y(jié)構(gòu) 7319 0

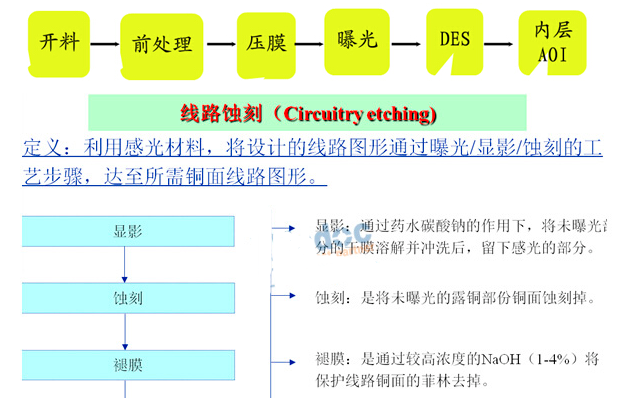

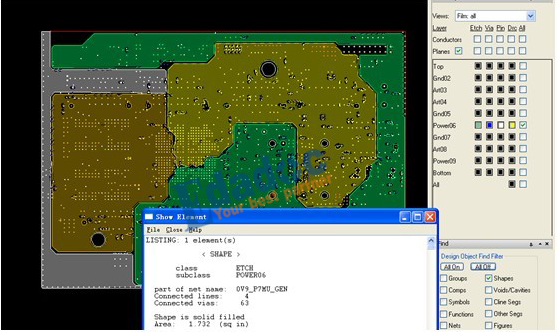

1、 PCB蝕刻介紹 蝕刻是使用化學(xué)反應(yīng)而移除多余材料的技術(shù)。PCB線路板生產(chǎn)加工對(duì)蝕刻質(zhì)量的基本要求就是能夠?qū)⒊刮g層下面以外的所有銅層完全去除干凈,...

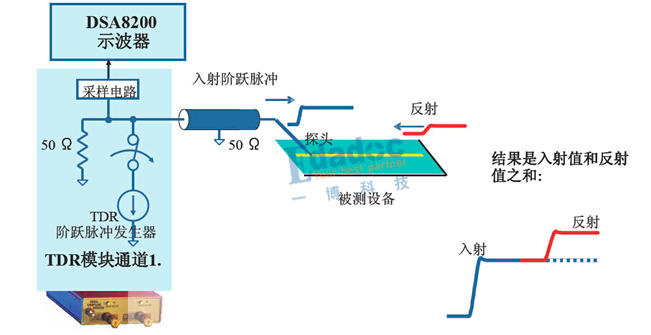

TDR產(chǎn)生一個(gè)階躍信號(hào)到待測(cè)器件中,會(huì)產(chǎn)生入射波,入射波經(jīng)過時(shí)延TD之后在待測(cè)器件中遇到阻抗不連續(xù)的地方,又會(huì)產(chǎn)生發(fā)射波,反射波將會(huì)疊加在入射波上,再經(jīng)...

圍繞拓?fù)浣Y(jié)構(gòu)與端接展開,淺談對(duì)fly-by結(jié)構(gòu)

DDR的歷史,就是一個(gè)SI技術(shù)變革的過程,說白了就是拓?fù)渑c端接之爭(zhēng)。DDR2使用的是T拓?fù)洌l(fā)展到DDR3,引入了全新的菊花鏈—fly-by結(jié)構(gòu)。使用f...

2021-04-11 標(biāo)簽:阻抗DDR拓?fù)浣Y(jié)構(gòu) 6801 0

TDR分辨率不足會(huì)給測(cè)試結(jié)果有什么影響?

在日常的生活工作中,有很多測(cè)試測(cè)量的工具,比如測(cè)量長(zhǎng)度的尺子,計(jì)量時(shí)間的鐘表等等,談到測(cè)試測(cè)量工具的時(shí)候,分辨率是關(guān)鍵指標(biāo)之一,比如尺子的分辨率是1mm...

2021-04-12 標(biāo)簽:測(cè)試測(cè)量阻抗TDR 3870 0

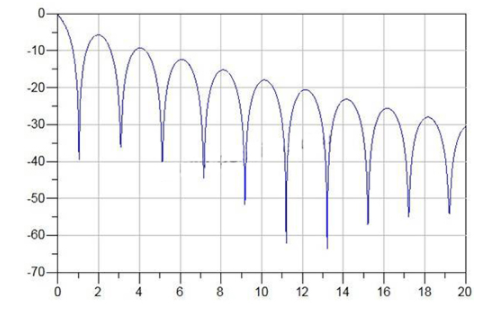

某網(wǎng)友S提問: 使用仿真軟件模擬背板上的微帶線,兩邊分別加上背板連接器和過孔的S參數(shù)模型,仿真出來的結(jié)果發(fā)現(xiàn)插損曲線整個(gè)頻段都會(huì)有波浪狀的震蕩,實(shí)測(cè)時(shí)完...

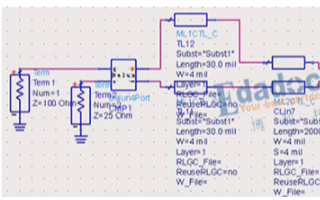

在PCB設(shè)計(jì)初期,確定差分信號(hào)線寬間距時(shí),我們會(huì)面對(duì)這么個(gè)選擇:相同的阻抗管控,對(duì)應(yīng)著不同的線寬間距,4mil/4mil,5mil/8mil或6mil/...

2021-04-16 標(biāo)簽:耦合阻抗PCB設(shè)計(jì) 5060 0

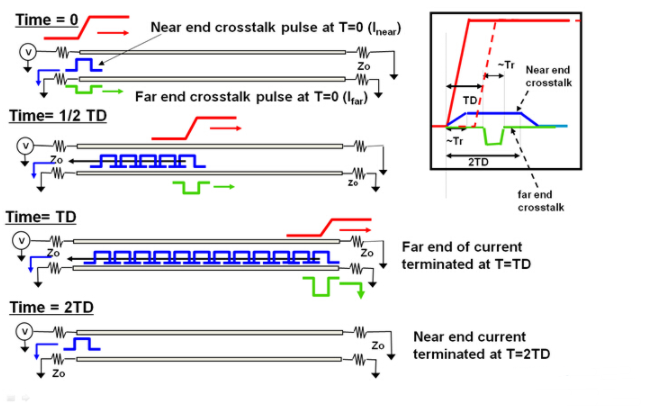

近端串?dāng)_與遠(yuǎn)端串?dāng)_的區(qū)別對(duì)比

容性耦合產(chǎn)生的電流分成兩半,一半往近端一半往遠(yuǎn)端,而感性耦合產(chǎn)生一個(gè)往近端的電流。

從仿真結(jié)果可以看到,隨著電源地之間的間距減小,加入埋容材料,平面諧振點(diǎn)向低頻偏移,同時(shí)低頻的阻抗也大幅降低,這個(gè)頻段埋容材料的作用也非常明顯。

2021-04-20 標(biāo)簽:阻抗PCB設(shè)計(jì)PDN 5019 0

電感阻抗頻率曲線_Matlab繪制電感曲線實(shí)驗(yàn)

橫軸為頻率,縱軸為阻抗的模。藍(lán)色的曲線為理想電感,理想電感的阻抗為Z=jwL,阻抗和頻率成正比,所以看起來像是一條直線。而黃色曲線是實(shí)際電感的阻抗曲線,...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |