完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > rtl

RTL在電子科學(xué)中指的是寄存器轉(zhuǎn)換級(jí)電路(Register Transfer Level)的縮寫,也叫暫存器轉(zhuǎn)移層次。

文章:352個(gè) 瀏覽:60806次 帖子:96個(gè)

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺(tái)之PL LED實(shí)驗(yàn)(3)

對(duì)于Versal來說PL(FPGA)開發(fā)是至關(guān)重要的,這也是Versal比其他ARM的有優(yōu)勢(shì)的地方,可以定制化很多ARM端的外設(shè)

verilog-2005和systemverilog-2017標(biāo)準(zhǔn)規(guī)范

作為邏輯工程師,在FPGA和數(shù)字IC開發(fā)和設(shè)計(jì)中,一般采用verilog,VHDL或SystemVerilog等作為硬件描述語言進(jìn)行工程設(shè)計(jì),將一張白板...

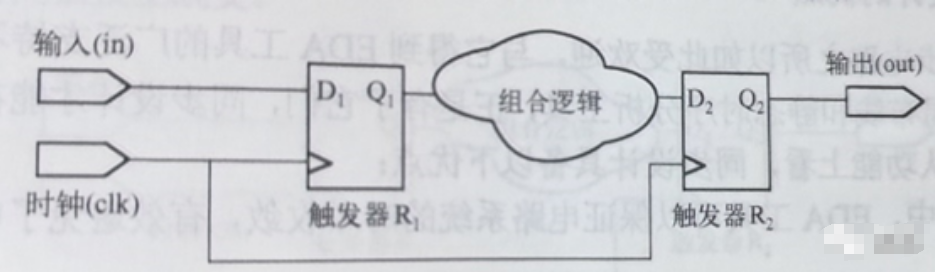

同步電路設(shè)計(jì)和異步電路設(shè)計(jì)的特點(diǎn)

同步邏輯是時(shí)鐘之間有固定的因果關(guān)系。異步邏輯是各時(shí)鐘之間沒有固定的因果關(guān)系。

2023-01-17 標(biāo)簽:電路設(shè)計(jì)RTL組合邏輯 3722 0

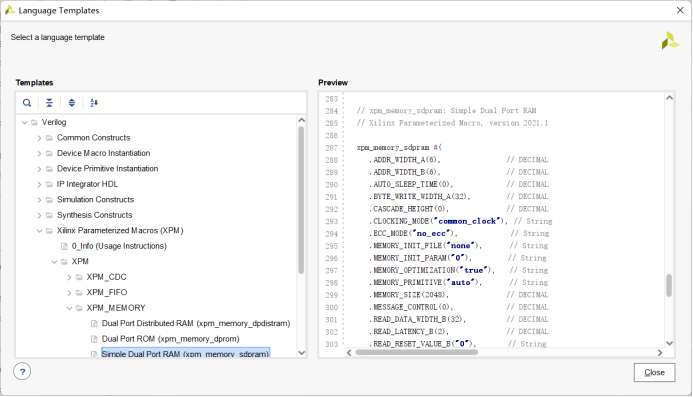

如何讓級(jí)聯(lián)URAM獲得最佳時(shí)序性能

在上一篇文章里《如何使用UltraScale+芯片中UltraRam資源》,我們向大家介紹了在RTL設(shè)計(jì)中使用URAM的方法。其中,我們推薦大家使用Xi...

14.2節(jié)提到的問題①,即設(shè)計(jì)中有很大的扇出,對(duì)于如何獲知該扇出信號(hào)有多種途徑。常見的途徑是通過FPGAEditor(Xilinx)或者Fitter里R...

使用Vivado Block Design設(shè)計(jì)解決項(xiàng)目繼承性問題

使用Vivado Block Design設(shè)計(jì)解決了項(xiàng)目繼承性問題,但是還有個(gè)問題,不知道大家有沒有遇到,就是新設(shè)計(jì)的自定義 RTL 文件無法快速的添加...

基于Verilog的經(jīng)典數(shù)字電路設(shè)計(jì)(1)加法器

加法器是非常重要的,它不僅是其它復(fù)雜算術(shù)運(yùn)算的基礎(chǔ),也是 CPU 中 ALU 的核心部件(全加器)。

【PlanAhead教程】-4 RTL and IP Design

教您如使用PlanAhead 13.1進(jìn)行設(shè)計(jì)應(yīng)用,通過一個(gè)設(shè)計(jì)程序,來體驗(yàn)PlanAhead的功能強(qiáng)大

數(shù)字硬件建模SystemVerilog之Interface方法概述

SystemVerilog Interface是modport的一種,但比簡(jiǎn)單的輸入、輸出或輸入輸出端口的功能更多。

2023-04-28 標(biāo)簽:時(shí)鐘發(fā)生器RTLUVM 3414 0

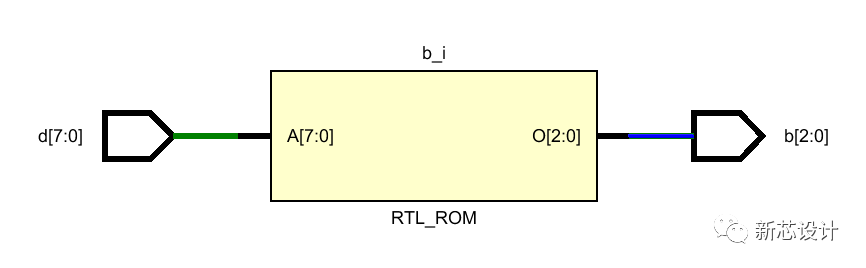

基于Verilog的經(jīng)典數(shù)字電路設(shè)計(jì)(4)編碼器

在近代戰(zhàn)爭(zhēng)中,軍事信息傳遞,例如通過發(fā)電報(bào)的方式,電報(bào)信息難免被敵方截獲,而我們又不得不通過發(fā)電報(bào)傳輸信息(喲,都近代了,就別飛鴿傳書了),所以發(fā)送方需...

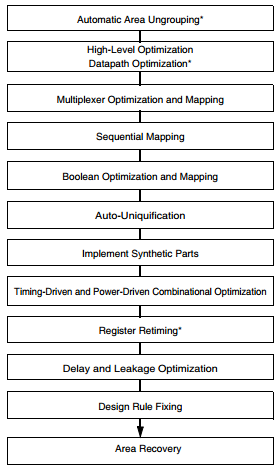

利用工具將RTL代碼轉(zhuǎn)化為門級(jí)網(wǎng)表的過程稱為邏輯綜合。綜合一個(gè)設(shè)計(jì)的過程,從讀取RTL代碼開始,通過時(shí)序約束關(guān)系,映射產(chǎn)生一個(gè)門級(jí)網(wǎng)表。

在電路設(shè)計(jì)自動(dòng)化的時(shí)代,綜合工具的作用不言而喻,通過綜合,設(shè)計(jì)人員能夠獲得自己所設(shè)計(jì)模塊的規(guī)模、時(shí)序性能和關(guān)鍵路徑等有用信息,進(jìn)而指導(dǎo)自己優(yōu)化設(shè)計(jì)結(jié)構(gòu)。...

2023-06-19 標(biāo)簽:電路設(shè)計(jì)HDLDC 3150 0

RISC-V處理器驗(yàn)證:瑞士奶酪模型驗(yàn)證應(yīng)用

而今,除了少數(shù)應(yīng)用外,最先進(jìn)的處理節(jié)點(diǎn)對(duì)所有應(yīng)用而言都太過昂貴。在大多數(shù)情況下,架構(gòu)創(chuàng)新是提供更高性能的唯一途徑。對(duì)于計(jì)算要求較高的應(yīng)用而言,理想情況下...

本文介紹一種新的方法,這種方法可以從RTL設(shè)計(jì)環(huán)境中,自動(dòng)生成一個(gè)芯片設(shè)計(jì)的門級(jí)波形,而不需要事先建立門級(jí)的環(huán)境。

2012-11-29 標(biāo)簽:SpringsoftCSRRTL 3100 0

USB無線網(wǎng)卡非常小巧,以至于會(huì)好奇,電路板是怎么塞進(jìn)去的

2022-10-19 標(biāo)簽:usbRTL無線網(wǎng)卡 3065 0

SystemVerilog調(diào)試過程中常用的方法和技巧

使用ctags掃描工作目錄,建立基于語法元素的索引,配合Vim可以實(shí)現(xiàn)語法元素的快速跳轉(zhuǎn)。

詳細(xì)介紹數(shù)字IC設(shè)計(jì)的全流程內(nèi)容

一顆芯片是如何造出來的,相信對(duì)行業(yè)稍有涉獵的同學(xué),都能簡(jiǎn)單作答:即先通過fabless進(jìn)行設(shè)計(jì),再交由Foundry進(jìn)行制造,最后由封測(cè)廠交出。

2023-10-09 標(biāo)簽:寄存器IC設(shè)計(jì)RTL 2995 0

介紹一種通過SystemC做RTL/C/C++聯(lián)合仿真的方法

當(dāng)FPGA開發(fā)者需要做RTL和C/C++聯(lián)合仿真的時(shí)候,一些常用的方法包括使用MicroBlaze軟核,或者使用QEMU仿真ZYNQ的PS部分。

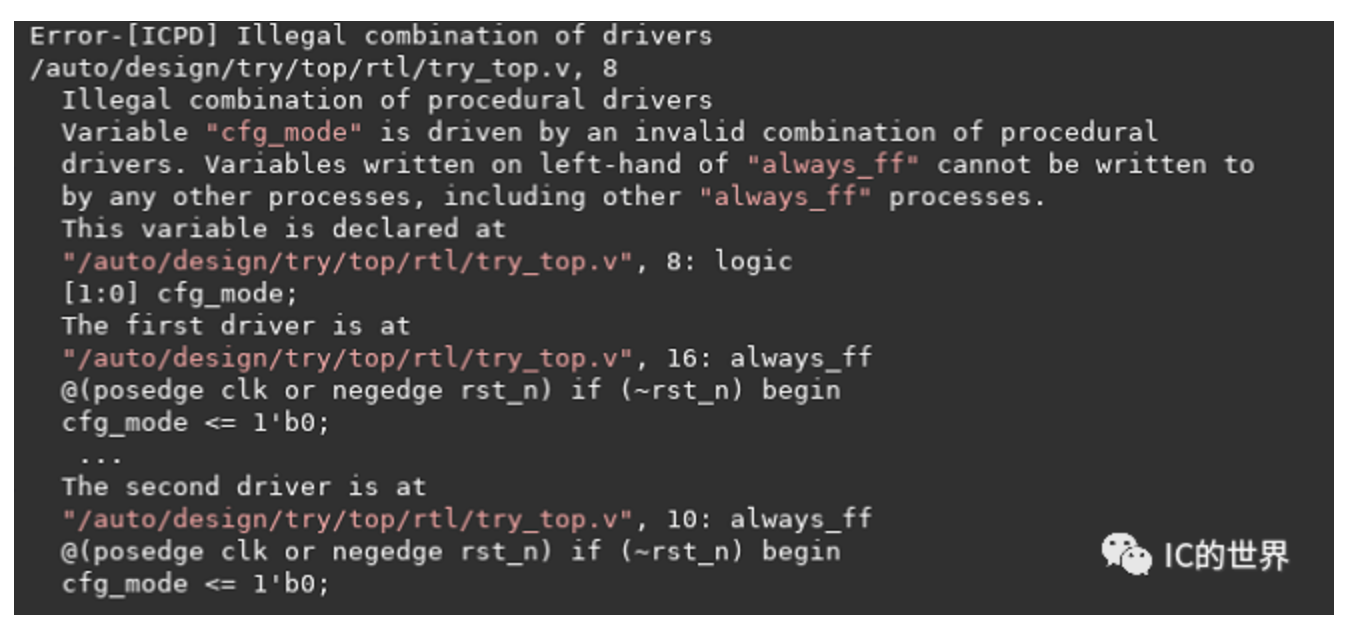

systemverilog:logic比reg更有優(yōu)勢(shì)?

在systemverilog協(xié)議中,logic定義四態(tài)值,即向量(vector)的每個(gè)位(bit)可以是邏輯0, 1, Z或X,與verilog協(xié)議中的...

2023-09-28 標(biāo)簽:驅(qū)動(dòng)器仿真器RTL 2917 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |