完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > system

system是一個(gè)C語言和C++下的函數(shù)。windows操作系統(tǒng)下system () 函數(shù)詳解主要是在C語言中的應(yīng)用,system函數(shù)需加頭文件《stdlib.h》后方可調(diào)用。

文章:117個(gè) 瀏覽:37637次 帖子:105個(gè)

SystemVerilog還為工程師定義新的數(shù)據(jù)類型提供了一種機(jī)制。用戶定義的數(shù)據(jù)類型允許從現(xiàn)有數(shù)據(jù)類型創(chuàng)建新的類型定義。

2023-02-09 標(biāo)簽:VerilogSystem數(shù)據(jù)類型 1334 0

packed union相比unpacked union最大的一個(gè)區(qū)別就是,在packed union中,所有成員的大小必須相同,這就保證了不管unio...

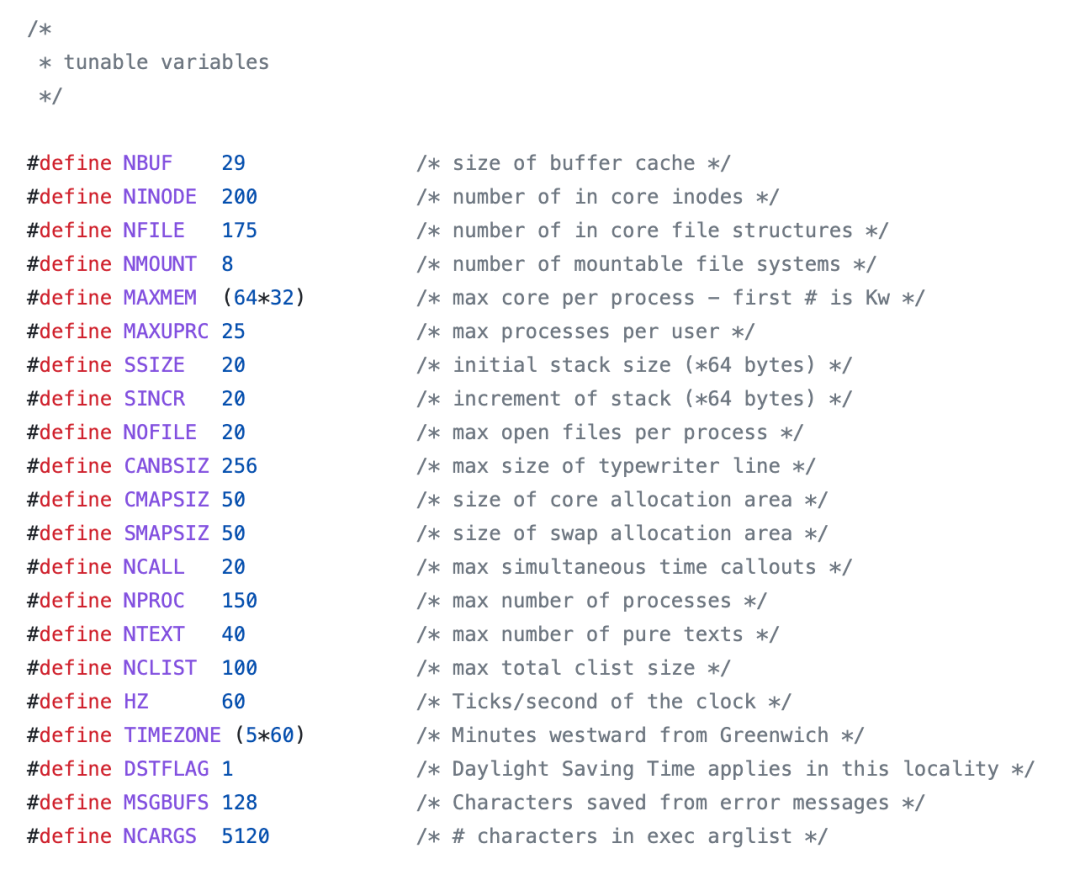

有時(shí),進(jìn)步難以察覺,特別是當(dāng)你正身處其中時(shí)。而對(duì)比新舊資料之間的差異,尋找那些推動(dòng)變革的信息源,我們就可以清晰地看到進(jìn)步的發(fā)生。在Linux(以及大部分...

2023-07-20 標(biāo)簽:Linux操作系統(tǒng)System 1323 0

關(guān)于有符號(hào)數(shù)據(jù)類型的示例

我們學(xué)習(xí)一下Systemverilog中的有符號(hào)數(shù)據(jù)類型的賦值。

2022-10-17 標(biāo)簽:VerilogSystem數(shù)據(jù)類型 1280 0

EDA數(shù)字仿真器:SystemVerilog全面覆蓋編程案例

數(shù)字芯片的驗(yàn)證技術(shù)是隨著Verilog語法的演變而演變的。最早,Verilog是完全用來描述(Model)硬件的,因此又叫HDL(Hardware De...

上面我們通過隊(duì)列dq1展示了push和pop的行為。然后我們聲明了有界隊(duì)列q3,最大的index限制是5,所以這個(gè)隊(duì)列最大的size是6.

一些有趣的數(shù)組相關(guān)的SystemVerilog約束

我們在工作中常常會(huì)針對(duì)數(shù)組施加各式的約束,下面列舉一下有趣的Systemverilog數(shù)組約束示例。

在 C# 中 Object 是所有類的基類,所有的結(jié)構(gòu)和類都直接或間接的派生自它。

繼承是基于類的面向?qū)ο缶幊?object-oriented pro - gramming)的最重要特性之一。

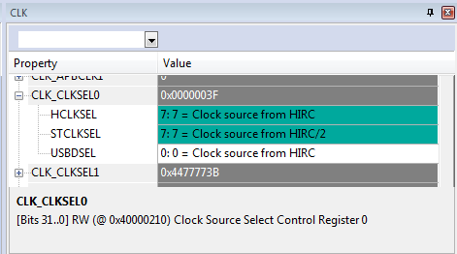

新唐開發(fā)平臺(tái):進(jìn)階使用者的七大訣竅(3)使用System Viewer檢查寄存器狀態(tài)

新唐開發(fā)平臺(tái):進(jìn)階使用者的七大訣竅(3)使用System Viewer檢查寄存器狀態(tài)

protected類屬性或方法具有l(wèi)ocal成員的所有特征,除此之外的是,protected類屬性或方法對(duì)擴(kuò)展類是可見的。

當(dāng)我們聲明一個(gè)類時(shí)還沒有分配內(nèi)存,只有在實(shí)例化(new())時(shí)才會(huì)分配內(nèi)存。這個(gè)時(shí)候?qū)ο缶浔赶虮环峙涞膬?nèi)存,下面是對(duì)象句柄賦值的示例。

SystemVerilog中的句柄賦值和對(duì)象復(fù)制的概念是有區(qū)別的。

SystemVerilog union允許單個(gè)存儲(chǔ)空間以不同的數(shù)據(jù)類型存在,所以u(píng)nion雖然看起來和struct一樣包含了很多個(gè)成員,實(shí)際上物理上共享...

2022-11-09 標(biāo)簽:VerilogSystem結(jié)構(gòu)體 1095 0

UltraScale開發(fā)板與套件-使用System Controller手動(dòng)調(diào)整VADJ

VADJ 引腳是 VITA 57.1 FMC 標(biāo)準(zhǔn)的一部分,承載著從載卡到 I/O 夾層模塊的可調(diào)節(jié)電壓等級(jí)的電源

System Verilog提供兩組通用的數(shù)據(jù)類型:網(wǎng)絡(luò)和變量(nets 和 variables)。網(wǎng)絡(luò)和變量同時(shí)具有類型和數(shù)據(jù)類型特性。類型表示信號(hào)為...

2023-02-09 標(biāo)簽:網(wǎng)絡(luò)VerilogSystem 968 0

SystemVerilog coding過程中你在哪里聲明臨時(shí)變量

眾所周知,語句塊中需要用到的變量只能在語句塊最開始定義。

SystemVerilog有兩種類型的數(shù)組:壓縮數(shù)組和非壓縮數(shù)組。壓縮數(shù)組是連續(xù)存儲(chǔ)的位的集合,通常稱為向量。非壓縮數(shù)組是網(wǎng)絡(luò)或變量的集合。

2023-02-09 標(biāo)簽:網(wǎng)絡(luò)VerilogSystem 900 0

SystemVerilog中的Unpacked Unions

unpacked union中各個(gè)成員的大小可以是不同的。

SystemVerilog中的Virtual Methods

SystemVerilog中多態(tài)能夠工作的前提是父類中的方法被聲明為virtual的。

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |