本文介時鐘頻率概念及其對系統(tǒng)性能的影響,并在電路板級、芯片級和單元模塊級分別提供了減小相位噪聲和抖動的有效方法。

2012-03-10 09:55:23 4544

4544

本文介紹了如何準(zhǔn)確地估算采樣時鐘抖動,以及如何計算正確的上下整合邊界。

2012-04-01 10:19:38 1665

1665

為了正確理解時鐘相關(guān)器件的抖動指標(biāo)規(guī)格,同時選擇抖動性能適合系統(tǒng)應(yīng)用的時鐘解決方案,本文詳細(xì)介紹了如何理解兩種類型時鐘驅(qū)動器的抖動參數(shù),以及從鎖相環(huán)輸出噪聲特性理解時鐘器件作為合成器、抖動濾除功能時的噪聲特性。

2013-06-21 15:40:41 14342

14342

時鐘抖動是相對于理想時鐘沿實(shí)際時鐘存在不隨時間積累的、時而超前、時而滯后的偏移稱為時鐘抖動,簡稱抖動

2023-11-08 15:08:01 892

892

當(dāng)DAQ信號鏈被隔離之后,控制采樣保持開關(guān)的信號一般來自進(jìn)行多通道同步采樣的背板。系統(tǒng)設(shè)計人員選擇低抖動數(shù)字隔離器至關(guān)重要,以使進(jìn)入ADC的采樣保持開關(guān)的控制信號具有低抖動。

2022-03-16 11:53:34 2696

2696

時鐘頻率的不斷提高使相位噪聲和抖動在系統(tǒng)時序上占據(jù)日益重要的位置。本文介其概念及其對系統(tǒng)性能的影響,并在電路板級、芯片級和單元模塊級分別提供了減小相位噪聲和抖動的有效方法。

2019-06-05 07:13:30

。 圖1:時間抖動引入與信號邊緣速率 圖1強(qiáng)調(diào)了噪聲源而不是固有抖動會引起定時抖動錯誤。更快的邊沿速率減少了時鐘信號上的電壓噪聲對時鐘抖動性能的影響。這種現(xiàn)象并非是僅屬于時鐘信號的特點(diǎn)。在接收時鐘信號或

2018-09-19 11:47:50

對高速信號進(jìn)行高分辨率的數(shù)字化處理需審慎選擇時鐘,才不至于使其影響模數(shù)轉(zhuǎn)換器(ADC)的性能。那么時鐘抖動會對高速ADC的性能有什么影響呢?

2021-04-08 06:00:04

圖1強(qiáng)調(diào)了噪聲源而不是固有抖動會引起定時抖動錯誤。更快的邊沿速率減少了時鐘信號上的電壓噪聲對時鐘抖動性能的影響。這種現(xiàn)象并非是僅屬于時鐘信號的特點(diǎn)。在接收時鐘信號或測量抖動性能的設(shè)備內(nèi),這種機(jī)理也表現(xiàn)得很明顯。…

2022-11-23 07:59:49

作者:John Johnson,德州儀器 本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點(diǎn)介紹抖動預(yù)算基礎(chǔ)。 用于在更遠(yuǎn)距離對日益增長的海量數(shù)據(jù)進(jìn)行傳輸?shù)囊恍?biāo)準(zhǔn)不斷出現(xiàn)。來自各行業(yè)的工程師們組成

2018-09-19 14:23:47

本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點(diǎn)介紹抖動預(yù)算基礎(chǔ)。 用于在更遠(yuǎn)距離對日益增長的海量數(shù)據(jù)進(jìn)行傳輸?shù)囊恍?biāo)準(zhǔn)不斷出現(xiàn)。來自各行業(yè)的工程師們組成了各種委員會和標(biāo)準(zhǔn)機(jī)構(gòu),根據(jù)其開發(fā)標(biāo)準(zhǔn)的目標(biāo)

2022-11-23 06:59:24

很多人都知道,抖動(這是時鐘邊沿不確定性)是不好的現(xiàn)象,其不僅可導(dǎo)致噪聲增加,而且還會降低數(shù)據(jù)轉(zhuǎn)換器的有效位數(shù) (ENOB)。例如,如果系統(tǒng)需要 100MHz 14(最小值)位的 ENOB,我們

2022-11-21 07:26:27

上升沿。圖1 —LMK03806(具有時鐘發(fā)生器、時鐘分頻器和驅(qū)動器)的方框圖因此,您下次設(shè)計采樣系統(tǒng)時,別忘了考慮時鐘抖動性能,因?yàn)檫@會影響整體動態(tài)范圍。其它資源:閱讀我們的最新博客系列《定時決定一切

2018-09-13 14:18:06

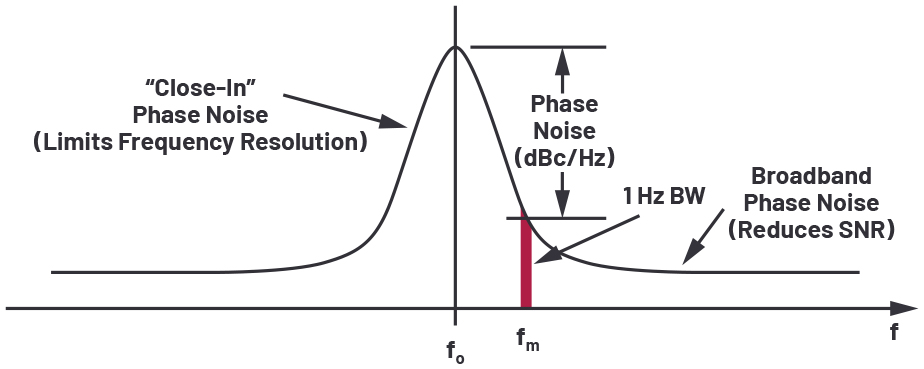

的SFDR(無雜散動態(tài)范圍)。結(jié)果,低性能時鐘源最終會降低系統(tǒng)容量和吞吐量。時鐘發(fā)生器技術(shù)規(guī)格盡管關(guān)于時鐘抖動的定義多種多樣,但在數(shù)據(jù)轉(zhuǎn)換器應(yīng)用中,最合適的定義是相位抖動,其單位為時域ps rms或fs

2018-10-18 11:29:03

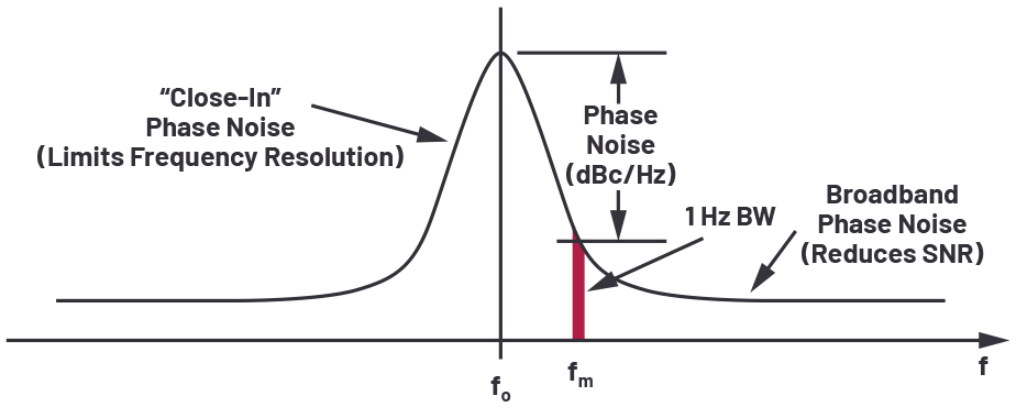

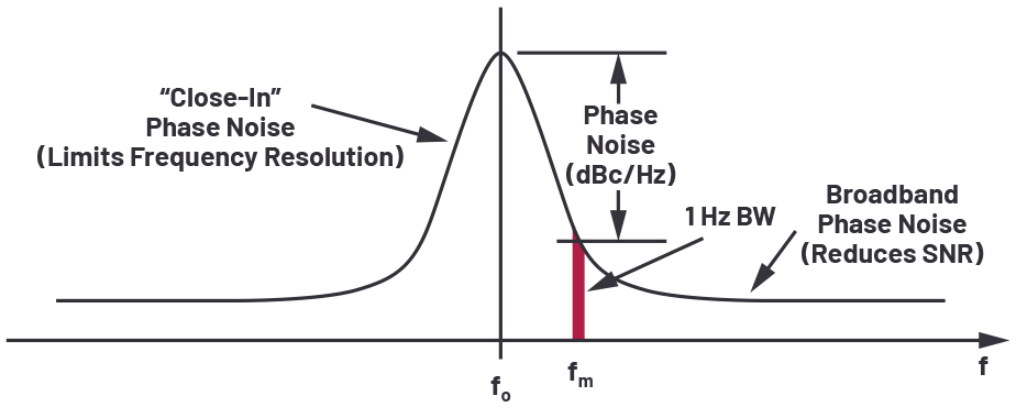

采樣時鐘考量在高性能采樣數(shù)據(jù)系統(tǒng)中,應(yīng)使用低相位噪聲晶體振蕩器產(chǎn)生ADC(或DAC)采樣時鐘,因?yàn)?b class="flag-6" style="color: red">采樣時鐘抖動會調(diào)制模擬輸入/輸出信號,并提高噪聲和失真底。采樣時鐘發(fā)生器應(yīng)與高噪聲數(shù)字電路隔離

2014-11-20 10:58:30

基于FPGA多通道采樣系統(tǒng)設(shè)計資料

2012-08-20 11:43:23

時域采樣理論與頻域采樣理論是數(shù)字信號處理中的重要理論,本文首先簡單介紹信號處理過程中時域采樣和頻域采樣的原理,接著基于NI LabVIEW2015平臺,設(shè)計開發(fā)了采樣定理驗(yàn)證系統(tǒng),在時域采樣系統(tǒng)中

2019-06-26 09:13:53

基于STC89C52,adc0832,7279的多路數(shù)據(jù)采樣系統(tǒng)設(shè)計匯編程序

2016-06-20 12:31:14

奈奎斯特準(zhǔn)則對數(shù)據(jù)采樣系統(tǒng)設(shè)計

2016-01-05 13:05:35

3GHz以上的系統(tǒng)中,時間抖動(jitter)會導(dǎo)致碼間干擾(ISI),造成傳輸誤碼率上升。在此趨勢下,高速數(shù)字設(shè)備的設(shè)計師們也開始更多地關(guān)注時序因素。在數(shù)字音頻信號中,隨著系統(tǒng)時鐘頻率的不斷提高,時間抖動

2016-09-28 16:08:05

采樣時鐘抖動對ADC信噪比的性能有什么影響?如何實(shí)現(xiàn)低抖動采樣時鐘電路的設(shè)計?

2021-04-14 06:49:20

如何設(shè)計并實(shí)現(xiàn)一種高性能中頻采樣系統(tǒng)?中頻采樣系統(tǒng)系統(tǒng)總體設(shè)計由哪些組成?它們分別有什么作用?

2021-04-07 07:09:32

需要使用濾波器,根據(jù)系統(tǒng)的特性選擇什么濾波器,這樣的濾波器如何使用代碼實(shí)現(xiàn),以及實(shí)現(xiàn)后可能會有什么樣的性能提升?”這樣“一條龍”的ADC濾波設(shè)計方法。2.高精度、中低速采樣系統(tǒng)的實(shí)際設(shè)計過程中,討論

2016-10-14 23:08:55

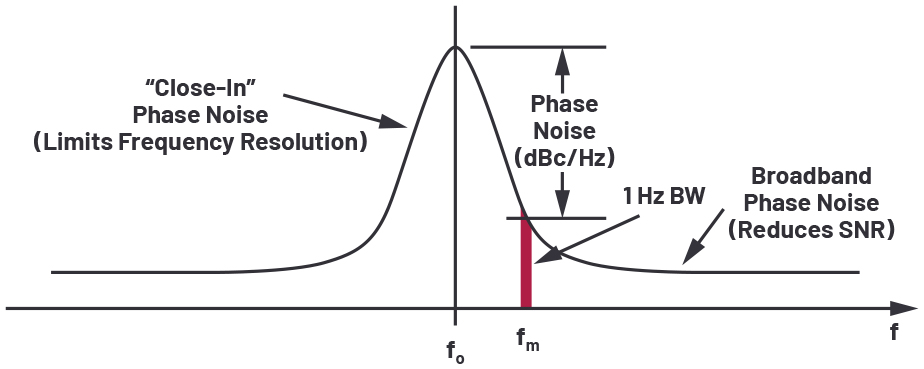

高信噪比=低ADC孔徑抖動嗎?在設(shè)計中,為了避免降低ADC的性能,工程師一般會采用抖動極低的采樣時鐘。然而,用于產(chǎn)生采樣時鐘的振蕩器常常用相位噪聲而非時間抖動來描述特性。那么,有木有方法將振蕩器相位噪聲轉(zhuǎn)換為時間抖動呢?

2019-08-13 06:27:54

摘要:在數(shù)據(jù)采樣系統(tǒng)中,高于二分之一采樣率的頻率成分“混疊”(搬移)到有用頻帶。大多數(shù)時間,混疊是有害的副作用,所以在模/數(shù)(AD)轉(zhuǎn)換級之前,將“欠采樣”的較高頻率簡單濾除。但有時候,特意設(shè)計利

2019-07-30 06:11:02

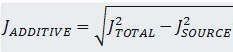

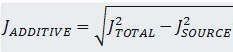

需求。作為該最新博客系列的開篇文章,我將幫助您了解如何正確測量時鐘緩沖器的附加抖動。為什么抖動很重要?在當(dāng)今數(shù)據(jù)通信、有線及無線基礎(chǔ)設(shè)施以及其它高速應(yīng)用等高級系統(tǒng)中,時鐘抖動是整體系統(tǒng)性能的關(guān)鍵因素。要

2018-09-13 14:38:43

在我的應(yīng)用程序中,HSPDM 觸發(fā) EVADC 同時對兩個通道進(jìn)行采樣。

我應(yīng)該如何配置 EVADC 以最大限度地減少采樣抖動并最大限度地提高采樣率?

在用戶手冊中,它提到 SSE=0,USC=0

2024-01-18 07:59:23

設(shè)計一個基于單片機(jī)的水質(zhì)采樣系統(tǒng),可以定時對不同深度的水層進(jìn)行采樣。單片機(jī)的選型和使用;水泵的選型和使用;相關(guān)傳感器的選型和使用;相關(guān)系統(tǒng)的集成;還需考慮制作安裝成本問題。推薦課程:張飛軟硬開源

2019-03-20 12:37:42

設(shè)計采樣系統(tǒng)時,關(guān)于時鐘抖動性能如何考慮?抖動對時鐘采樣系統(tǒng)有何影響?

2021-04-06 06:07:38

AD9444的功能和特性是什么?基于AD9444的時間交叉采樣系統(tǒng)怎樣去設(shè)計?設(shè)計時間交叉采樣系統(tǒng)有哪些注意事項?

2021-04-23 07:07:29

,你可以實(shí)現(xiàn)更高的性能—最多比傳統(tǒng)SAW示波器高9倍。 圖1:SAW示波器和TI LMK03328的10G鏈路性能一個低相位噪聲基準(zhǔn)時鐘轉(zhuǎn)化為串行鏈路中其它關(guān)鍵塊的更高抖動允許量分配。隨著數(shù)據(jù)速率快速

2018-09-05 16:07:30

3GHz以上的系統(tǒng)中,時間抖動(jitter)會導(dǎo)致碼間干擾(ISI),造成傳輸誤碼率上升。在此趨勢下,高速數(shù)字設(shè)備的設(shè)計師們也開始更多地關(guān)注時序因素。在數(shù)字音頻信號中,隨著系統(tǒng)時鐘頻率的不斷提高,時間抖動

2016-09-28 16:28:28

本文利用TMS320C5402 的高速計算功能,設(shè)計了一種新的交流采樣系統(tǒng),該系統(tǒng)利用小波變換的優(yōu)越特性對采集到的電壓和電流信號進(jìn)行處理,克服了原來在計算無功功率過程中由于

2009-09-08 14:45:50 22

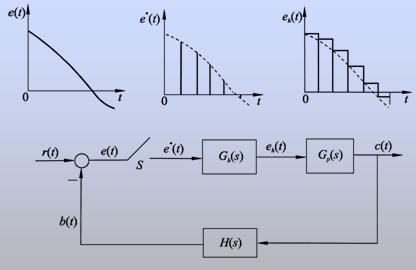

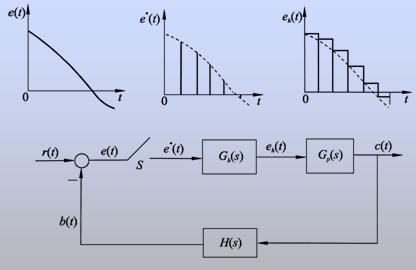

22 采樣控制系統(tǒng)與連續(xù)控制系統(tǒng)的根本區(qū)別在于采樣系統(tǒng)中既包含有連續(xù)信號,又包含有離散信號,是一個混和信號系統(tǒng)。分析和設(shè)計采樣系統(tǒng)的數(shù)學(xué)工具是Z變換,采用

2009-11-24 09:35:31 0

0 本文主要討論采樣時鐘抖動對ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設(shè)計。

2009-11-27 11:24:07 15

15 本文分析了晶振的漂移對GPS 接收機(jī)的影響,從鎖相環(huán)理論的角度,重點(diǎn)分析了采樣時鐘抖動對基帶載波跟蹤和偽碼跟蹤性能的影響,并給出一種環(huán)路分級降帶寬的方法來消除這種

2009-12-19 13:49:58 19

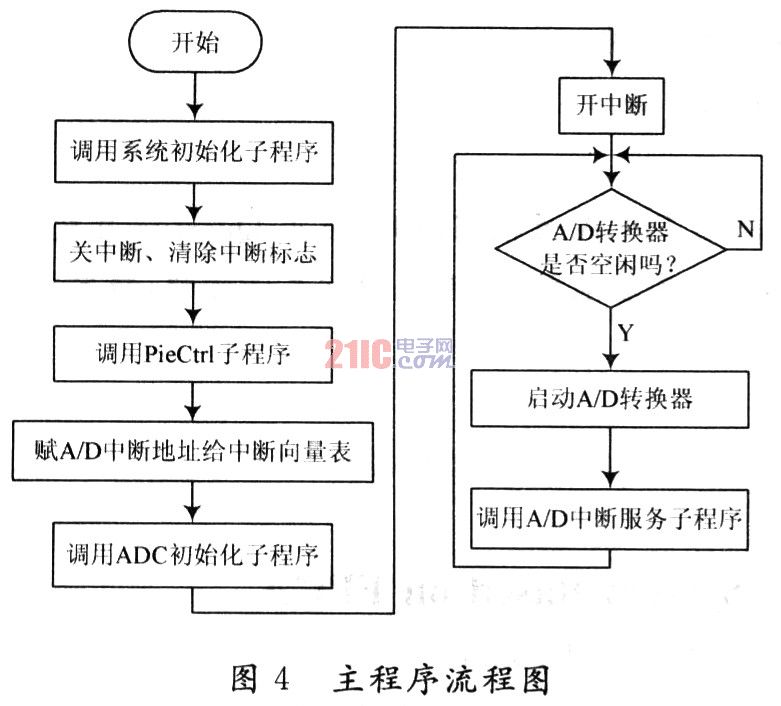

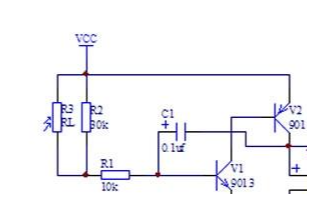

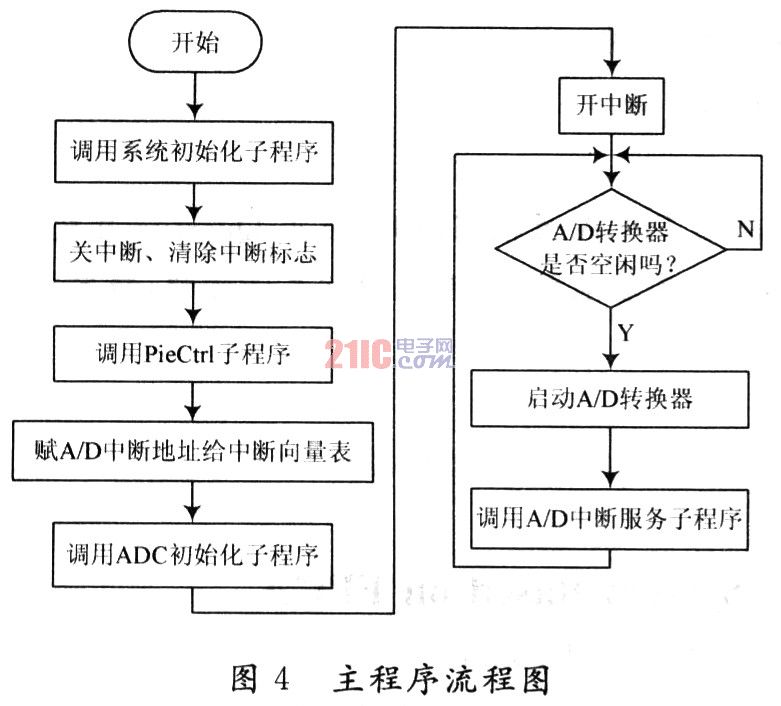

19 本文詳細(xì)介紹了基于TMS320F2812的電流采樣系統(tǒng)的設(shè)計方法。根據(jù)直流電流信號產(chǎn)生特點(diǎn)和采集技術(shù)的基本要求,選用合適的電流傳感器LTS25-NP,設(shè)計電壓變換電路,采用TMS320F2812型DSP

2010-07-27 16:50:08 65

65 隨著支持直接IF采樣的更高分辨率數(shù)據(jù)轉(zhuǎn)換器的上市,系統(tǒng)設(shè)計師在選擇低抖動時鐘電路時,需要在性能/成本之間做出權(quán)衡取舍。許多用于標(biāo)定時鐘抖動的傳統(tǒng)方法都不適用于數(shù)

2010-11-27 17:12:46 32

32

為提高中頻采樣系統(tǒng)性能,降低板級噪聲,加大采樣頻率的靈活性,設(shè)計并實(shí)現(xiàn)一種高性能中頻采樣系統(tǒng)。該系統(tǒng)利用AD9518-4實(shí)現(xiàn)可配置的采樣時鐘,根據(jù)不同的采樣要

2010-12-07 13:40:23 22

22 采樣系統(tǒng)典型結(jié)構(gòu)圖

2009-01-08 14:19:46 1407

1407

USB接口技術(shù)在外置式采樣系統(tǒng)中的應(yīng)用

一、前言:

---- 中高速、高精度連續(xù)采樣系統(tǒng)由

2009-02-08 10:47:06 632

632

理解不同類型的時鐘抖動

抖動定義為信號距離其理想位置的偏離。本文將重點(diǎn)研究時鐘抖動,并探討下面幾種類型的時鐘抖動:相鄰周期抖動、周期抖動、時間間隔誤

2010-01-06 11:48:11 1608

1608

利用TMS320F2812變頻電源的交流采樣系統(tǒng)設(shè)計方案

概述:本文介紹利用HCNR200及TMS320F2812內(nèi)置ADC采集交流電壓和負(fù)載電流信號的系統(tǒng)設(shè)計。HCNR200是一款

2010-03-22 14:36:44 1925

1925

基于DDS的時鐘抖動性能與DAC重構(gòu)濾波器性能的關(guān)系

2011-11-25 00:01:00 36

36 時鐘抖動時域分析(下):

2012-05-08 15:26:25 29

29 如果明智地選擇時鐘,一份簡單的抖動規(guī)范幾乎是不夠的。而重要的是,你要知道時鐘噪聲的帶寬和頻譜形狀,才能在采樣過程中適當(dāng)?shù)貙⑺鼈兛紤]進(jìn)去。很多系統(tǒng)設(shè)計師對數(shù)據(jù)轉(zhuǎn)換器

2012-05-08 15:29:00 47

47 200MHz實(shí)時采樣系統(tǒng)的設(shè)計與實(shí)現(xiàn),下來看看。

2016-02-19 16:39:58 0

0 基于FPGA多通道采樣系統(tǒng)設(shè)計資料,有興趣的同學(xué)可以下載學(xué)習(xí)

2016-04-28 14:29:56 48

48 寬帶雷達(dá)信號的低雜散采樣系統(tǒng)研究_王龍

2017-01-08 10:47:21 0

0 基于FPGA的高速多通道AD采樣系統(tǒng)的設(shè)計與實(shí)現(xiàn)_徐加彥

2017-01-18 20:23:58 12

12 基于TMS320F2812變頻電源的交流采樣系統(tǒng)設(shè)計_王榮海

2017-03-19 11:46:35 5

5 的系統(tǒng)設(shè)計,如在某些情況下系統(tǒng)性能極限由系統(tǒng)決定時序裕量。所以對時序抖動有很好的了解在系統(tǒng)設(shè)計中變得非常重要。總抖動可以隨機(jī)抖動和確定性抖動分離組件。我們將不討論抖動的組件本申請說明。我們將專注于不同類型的時鐘

2017-04-01 16:13:18 6

6 了解高速ADC時鐘抖動的影響將高速信號數(shù)字化到高分辨率要求仔細(xì)選擇一個時鐘,不會妥協(xié)模數(shù)轉(zhuǎn)換器的采樣性能(ADC)。 在這篇文章中,我們希望給讀者一個更好的了解時鐘抖動及其影響高速模數(shù)轉(zhuǎn)換器的性能

2017-05-15 15:20:59 13

13 級,從而降低成本和功耗。在欠采樣接收機(jī)設(shè)計中必須要特別注意采樣時鐘,因?yàn)樵谝恍└咻斎腩l率下時鐘抖動會成為限制信噪比(SNR) 的主要原因。 本系列文章共有三部分,第1 部分重點(diǎn)介紹如何準(zhǔn)確地估算某個時鐘源的抖動,以及如何將其與AD

2017-05-18 09:47:38 1

1 采樣時鐘抖動可對高性能ADCs信噪比性能的災(zāi)難。雖然信噪比和抖動之間的關(guān)系是眾所周知的,但是大多數(shù)振蕩器都是根據(jù)相位噪聲來指定的。

2017-08-03 10:57:33 13

13 時鐘產(chǎn)生抖動(jitter)會使發(fā)生抖動的時鐘信號與未發(fā)生抖動的時鐘信號在時域上存在偏差,從而使模數(shù)轉(zhuǎn)換器的采樣頻率發(fā)生紊亂,最終導(dǎo)致模數(shù)轉(zhuǎn)換器采樣的不穩(wěn)定性,使輸出信號存在頻譜毛刺,導(dǎo)致誤碼率上升

2017-11-11 18:22:26 9

9 本文分析了晶振的漂移對 GPS 接收機(jī)的影響,從鎖相環(huán)理論的角度,重點(diǎn)分析了采樣時鐘抖動對基帶載波跟蹤和偽碼跟蹤性能的影響,并給出一種環(huán)路分級降帶寬的方法來消除這種影響。該方法在保證最終偽碼跟蹤精度

2017-11-27 14:45:05 8

8 本文主要討論采樣時鐘抖動對 ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設(shè)計。 ADC 是現(xiàn)代數(shù)字解調(diào)器和軟件無線電接收機(jī)中連接模擬信號處理部分和數(shù)字信號處理部分的橋梁,其性能在很大程度上決定

2017-11-27 14:59:20 17

17 仔細(xì)觀察某個采樣點(diǎn),可以看到計時不準(zhǔn)(時鐘抖動或時鐘相位噪聲)是如何形成振幅變化的。由于高 Nyquist 區(qū)域(例如,f1 = 10 MHz 到 f2 = 110 MHz)欠采樣帶來輸入頻率的增加,固定數(shù)量的時鐘抖動自理想采樣點(diǎn)產(chǎn)生更大數(shù)量的振幅偏差(噪聲)。

2018-05-14 08:51:40 3

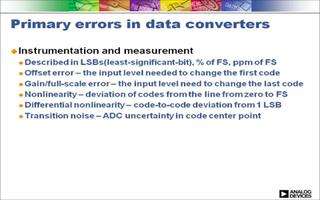

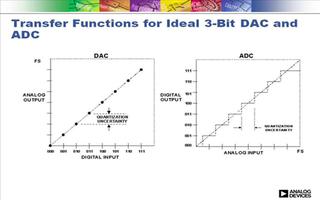

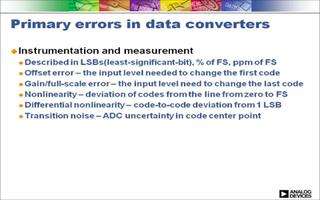

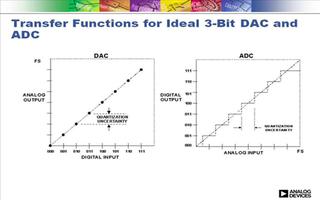

3 ADI公司推出三集系列在線研討會來關(guān)注模擬電氣信號到數(shù)字信號的轉(zhuǎn)換,以便通過DSP、微控制器或其它嵌入式處理器來分析和處理,本研討會是第一集。但在使用數(shù)據(jù)轉(zhuǎn)換器之前,我們需要先了解數(shù)據(jù)采樣系統(tǒng)的基礎(chǔ)知識:單極性和雙極性代碼、傳遞函數(shù)、奈奎斯特原理、濾波器等等。

2018-05-24 14:50:00 4352

4352

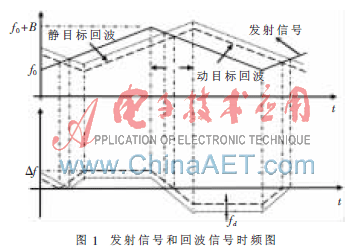

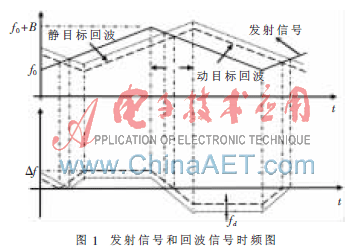

針對線性調(diào)頻連續(xù)波汽車防撞雷達(dá)回波信號的特點(diǎn),選用串行差分ADC,設(shè)計了一種基于DSP的SPORT口的I、Q雙通道采樣系統(tǒng),并通過實(shí)驗(yàn)驗(yàn)證了系統(tǒng)的正確性。

2018-12-19 11:49:49 1088

1088

ADI研討會:高性能時鐘: 解密抖動

2019-08-20 06:05:00 1656

1656 ADI公司推出三集系列在線研討會來關(guān)注模擬電氣信號到數(shù)字信號的轉(zhuǎn)換,以便通過DSP、微控制器或其它嵌入式處理器來分析和處理,本研討會是第一集。但在使用數(shù)據(jù)轉(zhuǎn)換器之前,我們需要先了解數(shù)據(jù)采樣系統(tǒng)的基礎(chǔ)知識:單極性和雙極性代碼、傳遞函數(shù)、奈奎斯特原理、濾波器等等。

2019-06-10 06:01:00 2986

2986

時鐘抖動性能主題似乎是時鐘,ADC和電源的當(dāng)前焦點(diǎn)供應(yīng)廠家。理由很清楚;時鐘抖動會干擾包括高速ADC在內(nèi)的數(shù)字電路的性能。高速時鐘可以對它們所接收的功率的“清潔度”非常敏感,盡管量化關(guān)系需要一些努力。

2019-09-14 11:24:00 7712

7712

ADC是現(xiàn)代數(shù)字解調(diào)器和軟件無線電接收機(jī)中連接模擬信號處理部分和數(shù)字信號處理部分的橋梁,其性能在很大程度上決定了接收機(jī)的整體性能。在A/D轉(zhuǎn)換過程中引入的噪聲來源較多,主要包括熱噪聲、ADC電源的紋波、參考電平的紋波、采樣時鐘抖動引起的相位噪聲以及量化錯誤引起的噪聲等。

2020-07-24 11:02:57 804

804

和高性能的優(yōu)勢,高性能設(shè)計中使用了高速串行總線。使用串行數(shù)據(jù)連接將數(shù)據(jù)從系統(tǒng)中的一個點(diǎn)傳輸?shù)搅硪稽c(diǎn)。時鐘和數(shù)據(jù)恢復(fù)電路用于將系統(tǒng)中的數(shù)據(jù)從發(fā)送方準(zhǔn)確地發(fā)送到接收方。 ? 在接收側(cè)對數(shù)據(jù)的準(zhǔn)確解釋主要取決于具有

2021-02-20 14:20:50 6228

6228

AN-1221: 使用ADF4002 PLL產(chǎn)生高速模數(shù)轉(zhuǎn)換器所需的極低抖動編碼(采樣)時鐘

2021-03-19 08:59:00 13

13 MT-002: 奈奎斯特準(zhǔn)則對數(shù)據(jù)采樣系統(tǒng)設(shè)計有何意義

2021-03-20 10:16:34 4

4 前言 :本文我們介紹下ADC采樣時鐘的抖動(Jitter)參數(shù)對ADC采樣的影響,主要介紹以下內(nèi)容: 時鐘抖動的構(gòu)成 時鐘抖動對ADC SNR的影響 如何計算時鐘抖動 如何優(yōu)化時鐘抖動 1.采樣理論

2021-04-07 16:43:45 7378

7378

AN-1576:采用AD9958 500 MSPS DDS或AD9858 1 GSPS DDS和AD9515時鐘分配IC的高性能ADC的低抖動采樣時鐘發(fā)生器

2021-04-30 09:48:42 13

13 作者: Richard Zarr

如果您在通信行業(yè)工作,那么您可能很熟悉抖動對系統(tǒng)性能的影響。抖動不僅會降低數(shù)據(jù)轉(zhuǎn)換器的性能,而且還可在高速數(shù)字系統(tǒng)中產(chǎn)生誤碼。憑直覺判斷,給時鐘增加噪聲會增大系統(tǒng)

2021-11-23 17:45:07 1769

1769

PCIe 和網(wǎng)絡(luò)時鐘抖動測量之間的另一個顯著差異在圖 2 中并不明顯。數(shù)字采樣示波器 (DSO) 用于獲取時鐘周期或波形文件以計算 PCIe 時鐘抖動,而不是 PNA。造成這種情況的主要原因是 PCIe 時鐘支持?jǐn)U頻,而網(wǎng)絡(luò)時鐘不支持,而且從歷史上看,PNA 一直無法使用正在擴(kuò)頻的時鐘。

2022-05-05 15:50:44 4513

4513

高 AC 和 DC 精度,而無需犧牲 DC 精度以獲得更高的采樣率。然而,為了實(shí)現(xiàn)高 AC 性能,例如信噪比 (SNR),系統(tǒng)設(shè)計人員需要考慮采樣時鐘信號或控制采樣和轉(zhuǎn)換的轉(zhuǎn)換啟動信號上的抖動引入的誤差

2022-07-19 16:37:37 1518

1518

超低抖動時鐘發(fā)生器如何優(yōu)化串行鏈路系統(tǒng)性能

2022-11-04 09:50:15 0

0 時鐘采樣系統(tǒng)最大限度減少抖動

2022-11-04 09:52:12 0

0 時鐘抖動使隨機(jī)抖動和相位噪聲不再神秘

2022-11-07 08:07:29 4

4 時鐘抖動解秘—高速鏈路時鐘抖動規(guī)范基礎(chǔ)知識

2022-11-07 08:07:30 1

1 精度,無需犧牲直流精度來換取更高的采樣速率。然而,為實(shí)現(xiàn)高交流性能,如信噪比(SNR),系統(tǒng)設(shè)計人員必須考慮采樣時鐘信號或控制ADC中采樣保持(SH)開關(guān)的轉(zhuǎn)換啟動信號上的抖動所帶來的誤差。隨著目標(biāo)信號和采樣速率的增加,控制采樣保持開

2022-11-13 11:25:11 473

473 抖動和相位噪聲是晶振的非常重要指標(biāo),本文主要從抖動和相位噪聲定義及原理出發(fā),闡述其在不同場景下對數(shù)字系統(tǒng)、高速串行接口、數(shù)據(jù)轉(zhuǎn)換器和射頻系統(tǒng)的影響。 1.?抖動和相位噪聲 1.1.?抖動

2023-03-10 14:54:32 657

657

系統(tǒng)時序設(shè)計中對時鐘信號的要求是非常嚴(yán)格的,因?yàn)槲覀兯械臅r序計算都是以恒定的時鐘信號為基準(zhǔn)。但實(shí)際中時鐘信號往往不可能總是那么完美,會出現(xiàn)抖動(Jitter)和偏移(Skew)問題。

2023-04-04 09:20:56 1637

1637 先來聊一聊什么是時鐘抖動。時鐘抖動實(shí)際上是相比于理想時鐘的時鐘邊沿位置,實(shí)際時鐘的時鐘邊沿的偏差,偏差越大,抖動越大。實(shí)際上,時鐘源例如PLL是無法產(chǎn)生一個絕對干凈的時鐘。這就意味著時鐘邊沿出現(xiàn)在

2023-06-09 09:40:50 1128

1128

精度,無需犧牲直流精度來換取更高的采樣速率。然而,為實(shí)現(xiàn)高交流性能,如信噪比(SNR),系統(tǒng)設(shè)計人員必須考慮采樣時鐘信號或控制ADC中采樣保持(S&H)開關(guān)的轉(zhuǎn)換啟動信號上的抖動所帶來的誤差。隨著目標(biāo)信號和采樣速率的增加,控制采樣保持開關(guān)的信號抖動會成為主要誤差源。

2023-06-15 16:30:12 381

381

本文主要介紹了時鐘偏差和時鐘抖動。

2023-07-04 14:38:28 960

960

電子發(fā)燒友網(wǎng)站提供《高性能中頻采樣系統(tǒng)的設(shè)計與實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-10-18 09:57:34 0

0 電子發(fā)燒友網(wǎng)站提供《時鐘抖動對ADC性能有什么影響.pdf》資料免費(fèi)下載

2023-11-28 10:24:10 1

1 ,通常低于 100 飛秒 (fs),以保持系統(tǒng)性能。這些時鐘還必須長期保持低抖動規(guī)格,且不受溫度和電壓的影響。 某些抖動是由信號路徑噪聲和失真引起的,使用重復(fù)時鐘和重定時技術(shù)可以在一定程度上減少抖動。不過,抖動也是由時鐘源產(chǎn)生的,時鐘源通常是振蕩器。這是由于各

2024-02-13 17:47:00 621

621

電子發(fā)燒友App

電子發(fā)燒友App

評論