GaAs基VCSEL已廣泛應用于三維成像、無人駕駛、物聯(lián)網(wǎng)、數(shù)據(jù)通訊等領(lǐng)域,同時在光電對抗、激光雷達、航空航天等高精尖領(lǐng)域也發(fā)揮著巨大的作用和潛能。GaAs基VCSEL的刻蝕技術(shù)是制備過程中最關(guān)鍵的環(huán)節(jié)。刻蝕時掩膜的質(zhì)量、刻蝕GaAs后的表面質(zhì)量、VCSEL的臺面和側(cè)壁形貌都會直接影響器件性能。在刻蝕過程中,掩膜的好壞直接影響刻蝕的效果。

VCSEL側(cè)壁如果過于粗糙,就會影響載流子的復合效率,也會使光發(fā)生散射效應。VCSEL表面和側(cè)壁不光滑、有殘留時會增大其電阻值或擊穿電流。如果GaAs/AIGaAs的刻蝕速率未能達到1:1,那么臺面的側(cè)壁會出現(xiàn)橫向鉆蝕的鏤空現(xiàn)象,不利于實現(xiàn)均勻電場和高效的器件隔離。

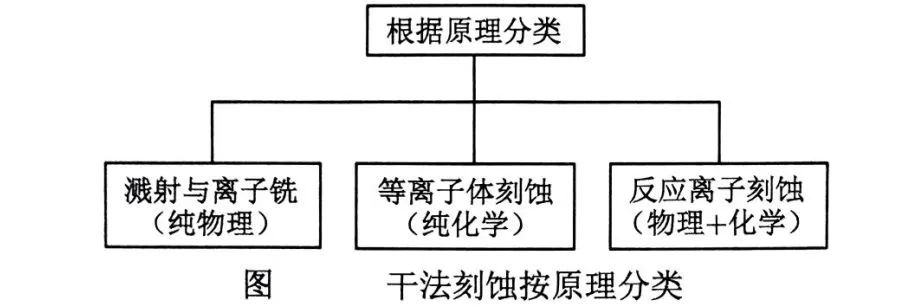

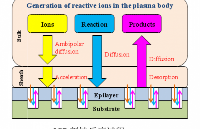

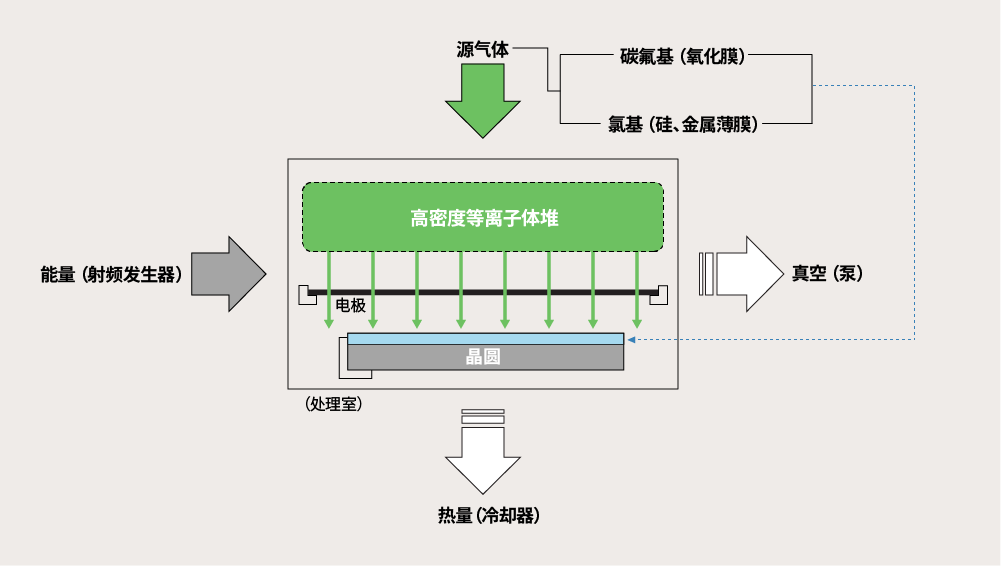

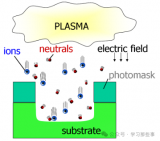

目前VCSEL刻蝕分為濕法刻蝕和干法刻蝕兩種。為實現(xiàn)良好的形貌控制,GaAs基VCSEL的刻蝕通常采用干法刻蝕技術(shù)。干法刻燭具有精度高、可控性好、易于批量生產(chǎn)以及工藝清潔度高等優(yōu)勢。因此,深入研究高精度的刻蝕技術(shù),尤其是高精度的干法刻蝕技術(shù),對制備高性能VCSEL具有重要意義。

據(jù)麥姆斯咨詢報道,近期,長春理工大學高功率半導體激光國家重點實驗室的科研團隊在《紅外》期刊上發(fā)表了以“GaAs基VCSEL干法刻蝕技術(shù)研究綜述”為主題的文章。該文章第一作者為范昊軒,主要從事半導體激光器件的研究工作;通訊作者為郝永芹研究員,主要從事半導體光電子材料與器件方面的研究工作。本文綜述了GaAs基VCSEL干法刻蝕技術(shù)的發(fā)展與研究現(xiàn)狀。

刻蝕中改善掩膜質(zhì)量的研究現(xiàn)狀

目前,VCSEL刻蝕過程中的關(guān)鍵環(huán)節(jié)主要有以下幾個方面:控制臺面的尺寸、刻蝕時掩膜的質(zhì)量、刻蝕GaAs后的表面質(zhì)量、VCSEL臺面和側(cè)壁形貌。

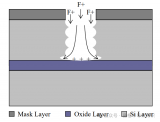

刻蝕VCSEL之前要進行光刻。常用的掩膜有光刻膠軟掩膜,二氧化硅、氮化硅和金屬硬掩膜。光刻膠掩膜通過前烘和堅膜之后形狀會改變。由于在刻蝕氣體氛圍中光刻膠的抗蝕性不能保證穩(wěn)定的狀態(tài),在刻蝕過程中高濃度的離子會使光刻膠掩膜變性或者碳化。另外,光刻膠掩膜的形狀在刻蝕過程中會轉(zhuǎn)移給下方的晶圓片,所以控制好掩膜的質(zhì)量對刻蝕過程很重要。

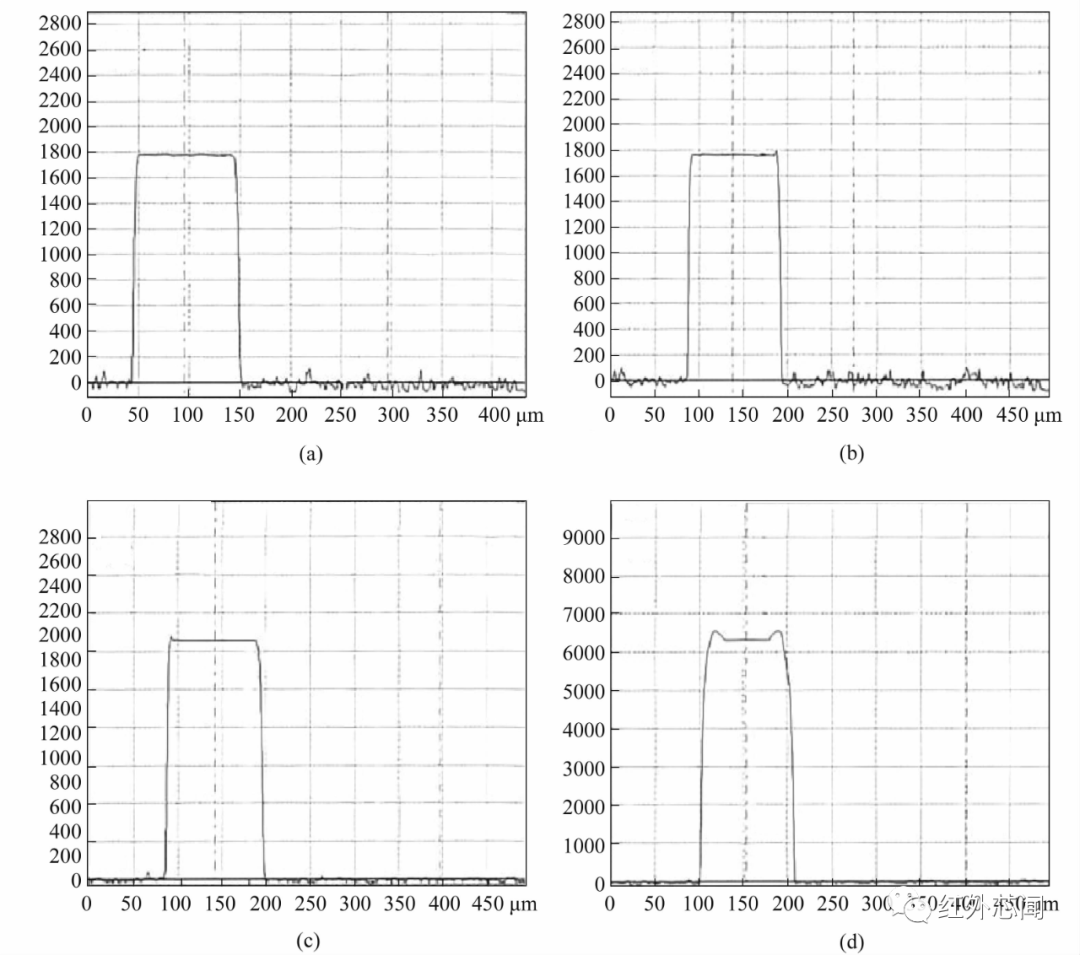

為了使光刻膠掩膜具有更好的形貌,研究人員通過對光刻膠厚度的分析,研究了不同厚度下光刻膠掩膜在烘烤后的變化規(guī)律。2012年,孫麗媛等人針對光刻膠掩膜對刻蝕GaAs材料側(cè)壁的問題,采用控制變量法研究了厚度不同的光刻膠財GaAs材料側(cè)壁傾角產(chǎn)生的影響。他們用臺階儀測量旋涂不同厚度光刻膠烘烤之后的結(jié)果,發(fā)現(xiàn)光刻膠的厚度越大,高溫烘烤后光刻膠變性越嚴重,如圖1所示。

圖1

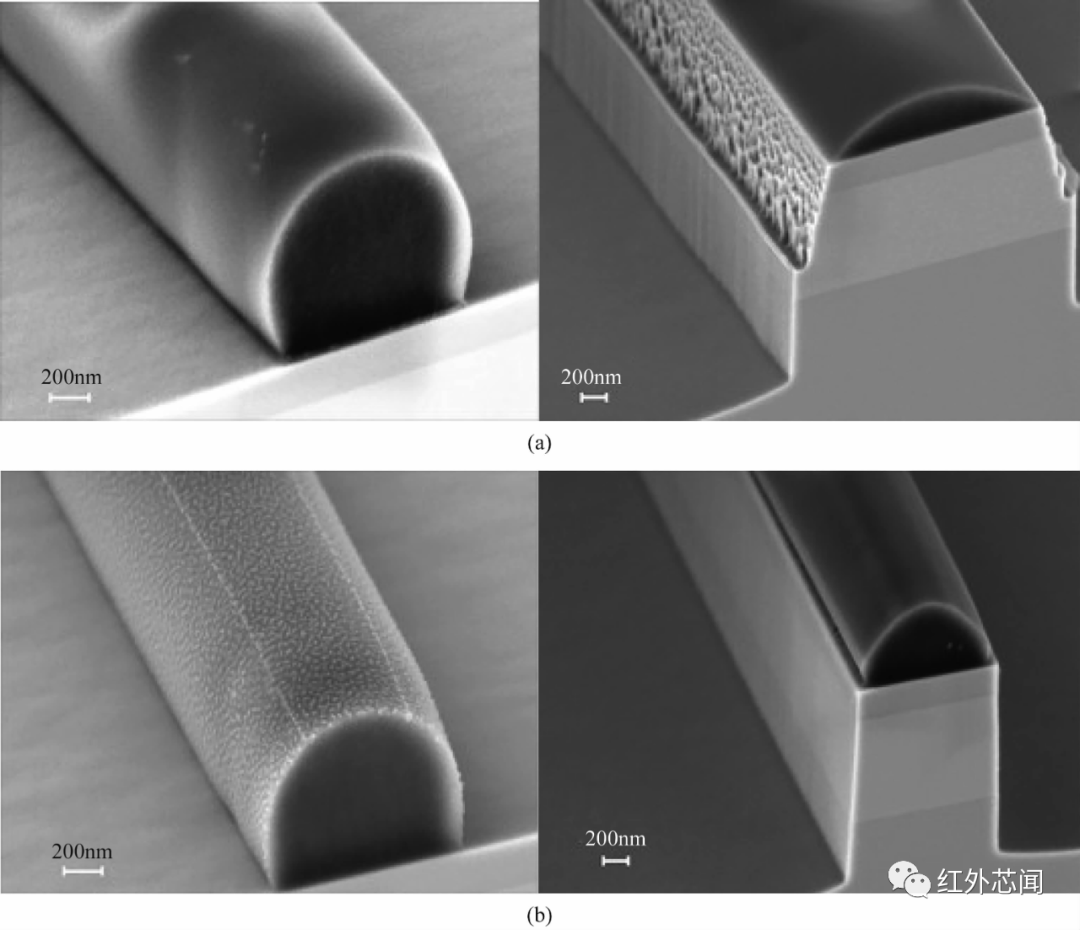

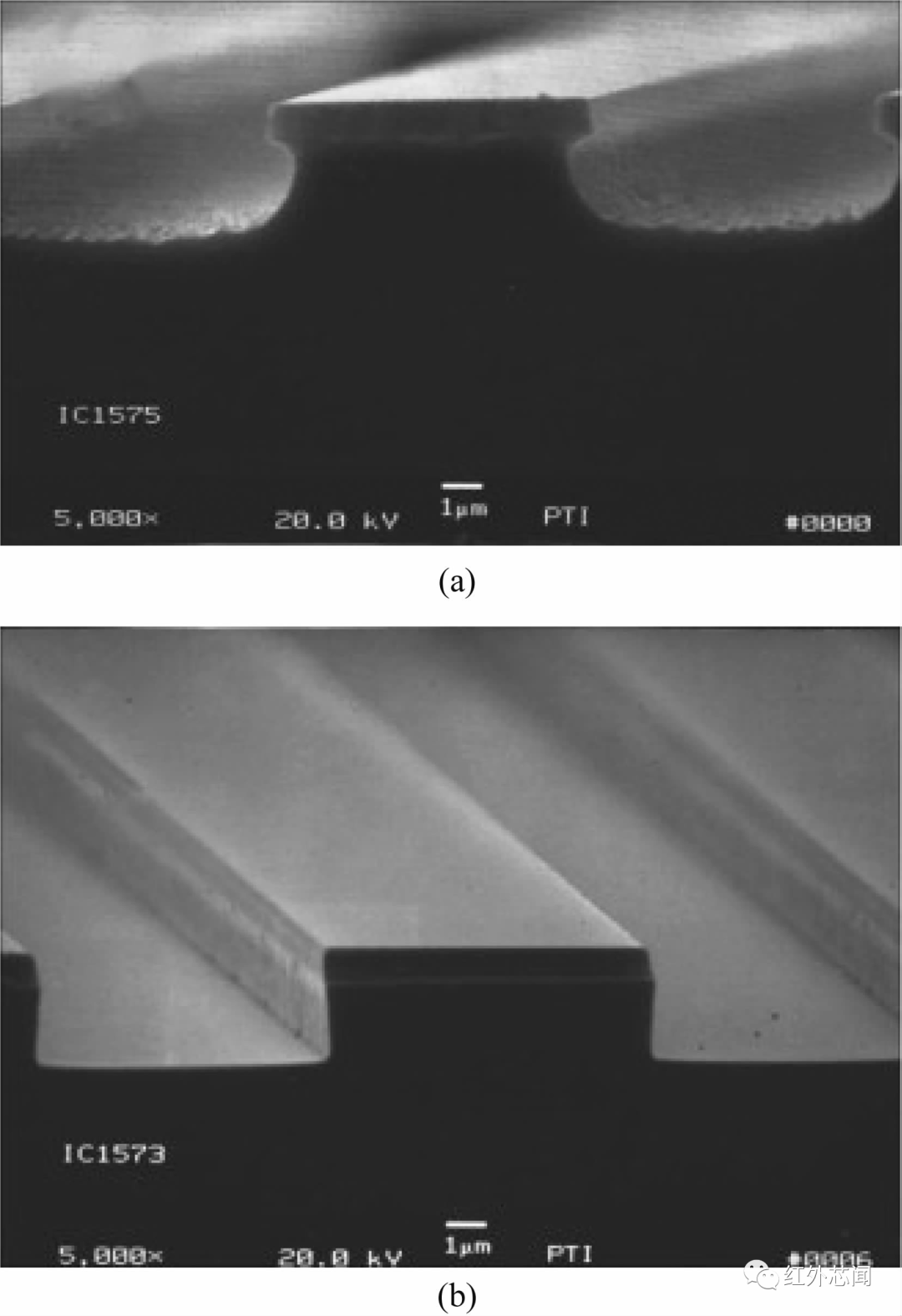

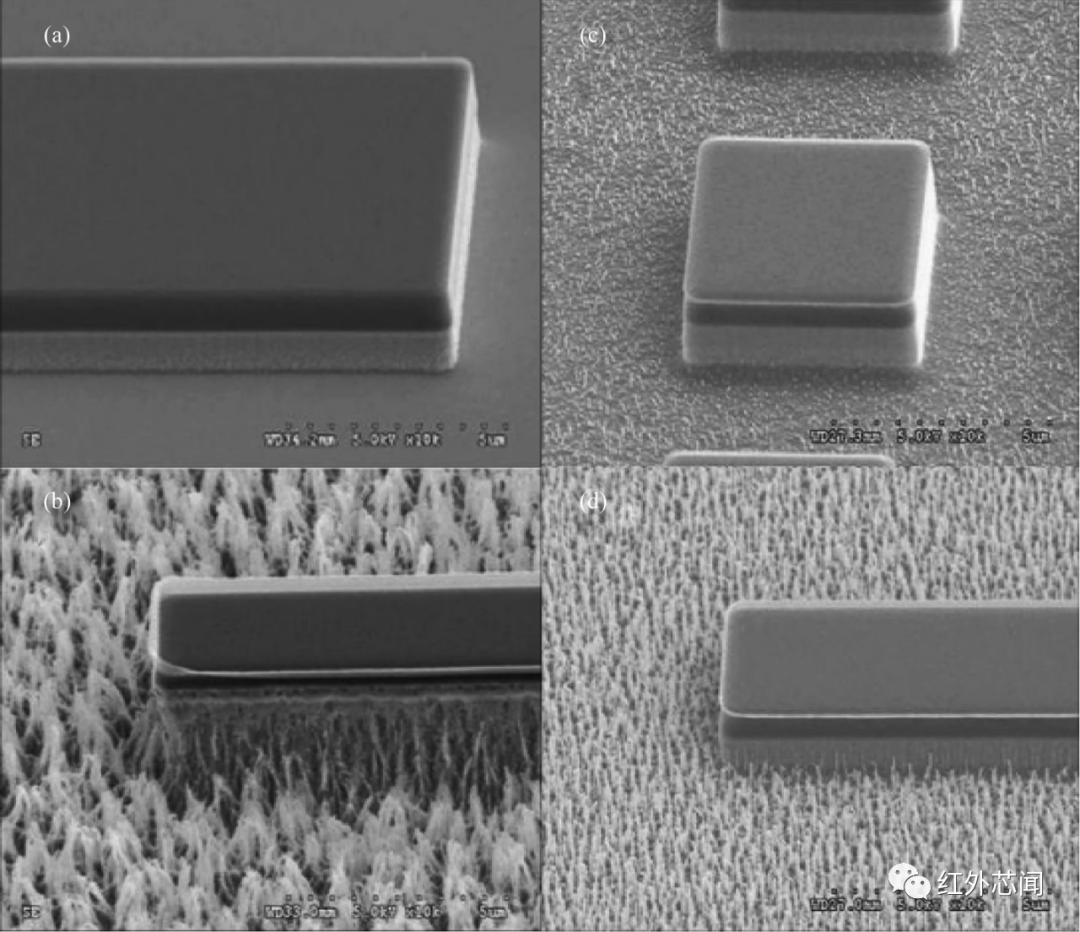

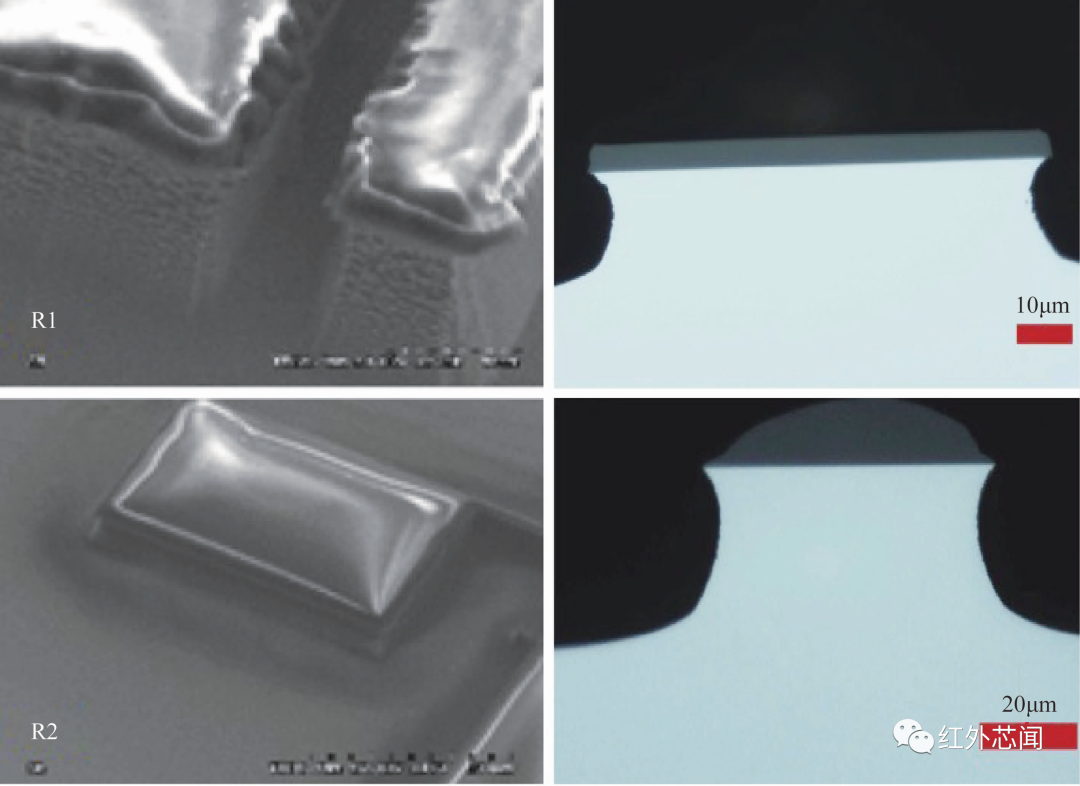

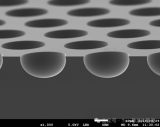

通過優(yōu)化光刻膠掩膜回流方法,研究人員改善了光刻膠掩膜在回流后的形貌。2014年,Porkolab G A等人針對光刻膠掩膜回流時出現(xiàn)的坍塌變性問題,采用等離子體輔助回流方法改善了傳統(tǒng)加熱回流法的坍塌現(xiàn)象,如圖2中的掃描電子顯微鏡(SEM)圖像所示。

圖2

2015年,焦慶斌等人發(fā)現(xiàn)了光柵頂部的光刻膠掩膜“頂角平臺”現(xiàn)象(出現(xiàn)光刻膠掩模占寬比過大的情況)。針對這一問題,他們采用了改變光刻過程中的曝光時間和提高倒置熱熔溫度的方法。結(jié)果表明,通過增加曝光時間和提高倒置熱熔溫度,可明顯減小占寬比以及光刻膠掩模線條寬度。

2016年,喬輝等人針對在電感耦合等離子體(ICP)干法刻蝕后光刻膠掩膜出現(xiàn)凸起和孔洞的異常現(xiàn)象,采用探針式表面輪廓儀和激光共聚焦顯微鏡對其進行了分析。他們認為,刻蝕時等離子體中的紫外線對掩膜的光刻膠進行曝光作用而釋放出一定雖的氮氣,在光刻膠內(nèi)外形成了壓強差,使光刻膠局部表面微凸起。當光刻膠的強度無法阻止內(nèi)部氮氣膨脹時,則會產(chǎn)生類似的孔洞狀缺陷,導致掩膜保護作用失效。

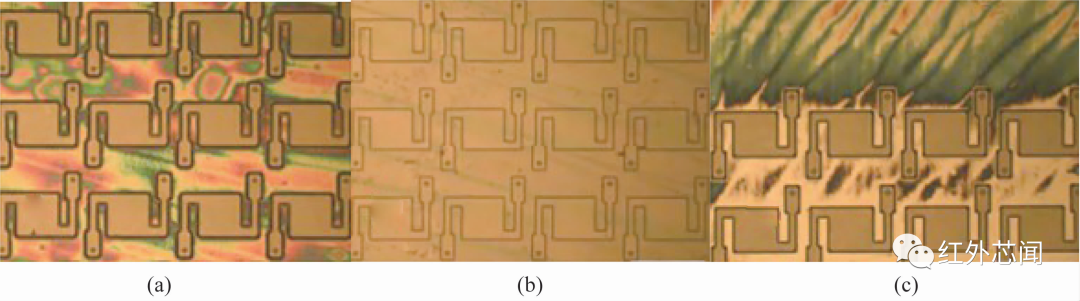

隨著刻蝕技術(shù)的發(fā)展,工藝精度不斷提高。2016年,艾駿等人針對光刻膠掩膜的光刻線條精度問題展開研究。他們分析了光刻時曝光時間長短(見圖3(a))、顯影時顯影液的濃度(見圖3(b))以及顯影時顯影的時間(見圖3(c))對光刻膠掩膜的光刻線條精度的影響,探究了各種不良形貌出現(xiàn)的原因,為今后光刻技術(shù)在復雜環(huán)境下的應用和發(fā)展打下了基礎(chǔ)。

圖3

2018年,Vigneron P B等人發(fā)現(xiàn)刻蝕GaAs時光刻膠掩膜出現(xiàn)了“微掩蔽”現(xiàn)象。光刻膠掩膜的四角出現(xiàn)坍塌和波紋,如圖4(a)所示。在刻蝕過程中會將這些波紋轉(zhuǎn)移到下方的基片上,造成粗糙的側(cè)壁,引起散射損傷。他們在BCl?/Cl?/Ar刻蝕氣體組合中加入極少量N?后,微掩蔽現(xiàn)象消失,如圖4(b)所示。

圖4

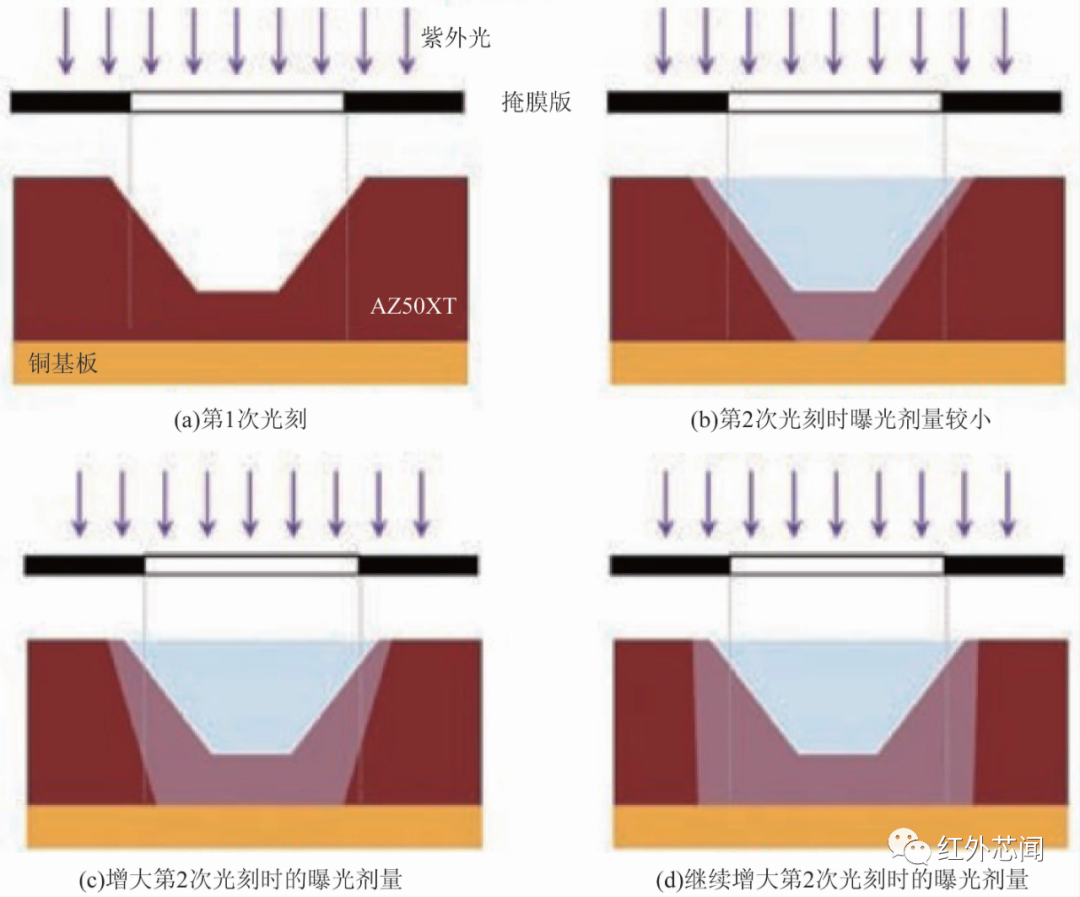

2018年,杜立群等人針對較厚的光刻膠掩膜在曝光過程中膠膜內(nèi)部曝光劑量分布不均勻使得光刻膠掩膜厚度過大的情況,嘗試采用分次曝光顯影法改善無法控制光刻圖形精度的問題。通過對基準點預曝光的分次曝光顯影法調(diào)整光刻膠掩膜的厚度,對光刻膠掩模的均勻性以及光刻膠掩模內(nèi)部的曝光劑量進行調(diào)節(jié)(原理見圖5)。

圖5 分次曝光顯影法的原理圖

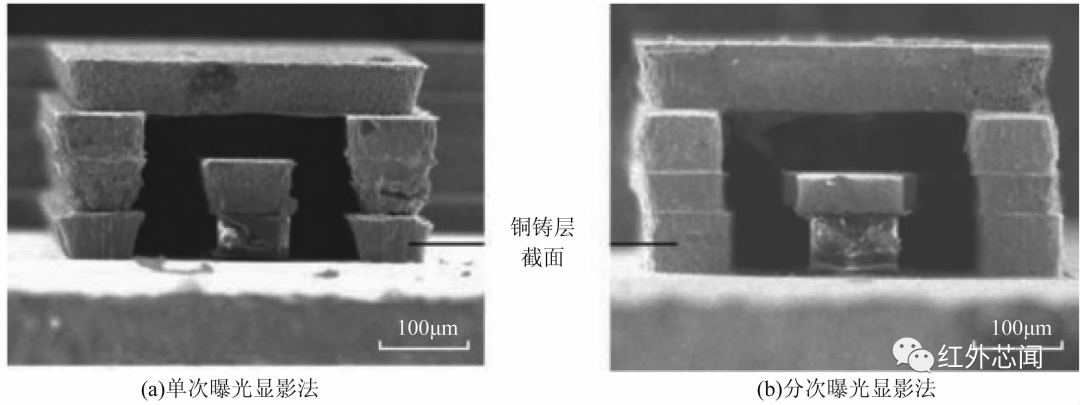

分次曝光顯影法的原理如下:首先去掉光刻膠頂部的掩膜,使光刻膠掩膜內(nèi)部充分曝光;光刻膠掩膜頂部的線寬變小,底部掩膜的線寬變大,二者之間的差值變小。這方法可以顯著改善光刻圖形的尺寸精度,對厚膠的曝光起到了優(yōu)化的作用(見圖6)。

圖6 射頻同軸傳輸截面的SEM圖

刻蝕GaAs的研究現(xiàn)狀

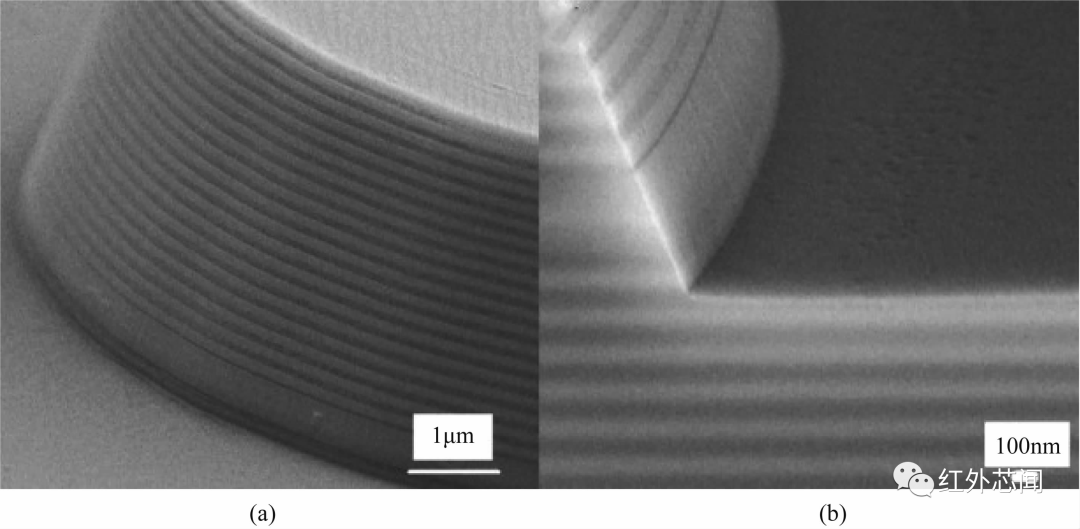

在刻蝕GaAs方面,2000年Lee J W等人針對GaAs側(cè)壁存在的鉆刻現(xiàn)象,引用BCl?/SF?/N?/He氣體刻蝕GaAs結(jié)構(gòu),并通過添加N?來增強刻蝕過程中的側(cè)壁鈍化功能。結(jié)果表明,刻蝕輪廓形貌得到了明顯的改善,增強了各向異性刻蝕(見圖7)。

圖7

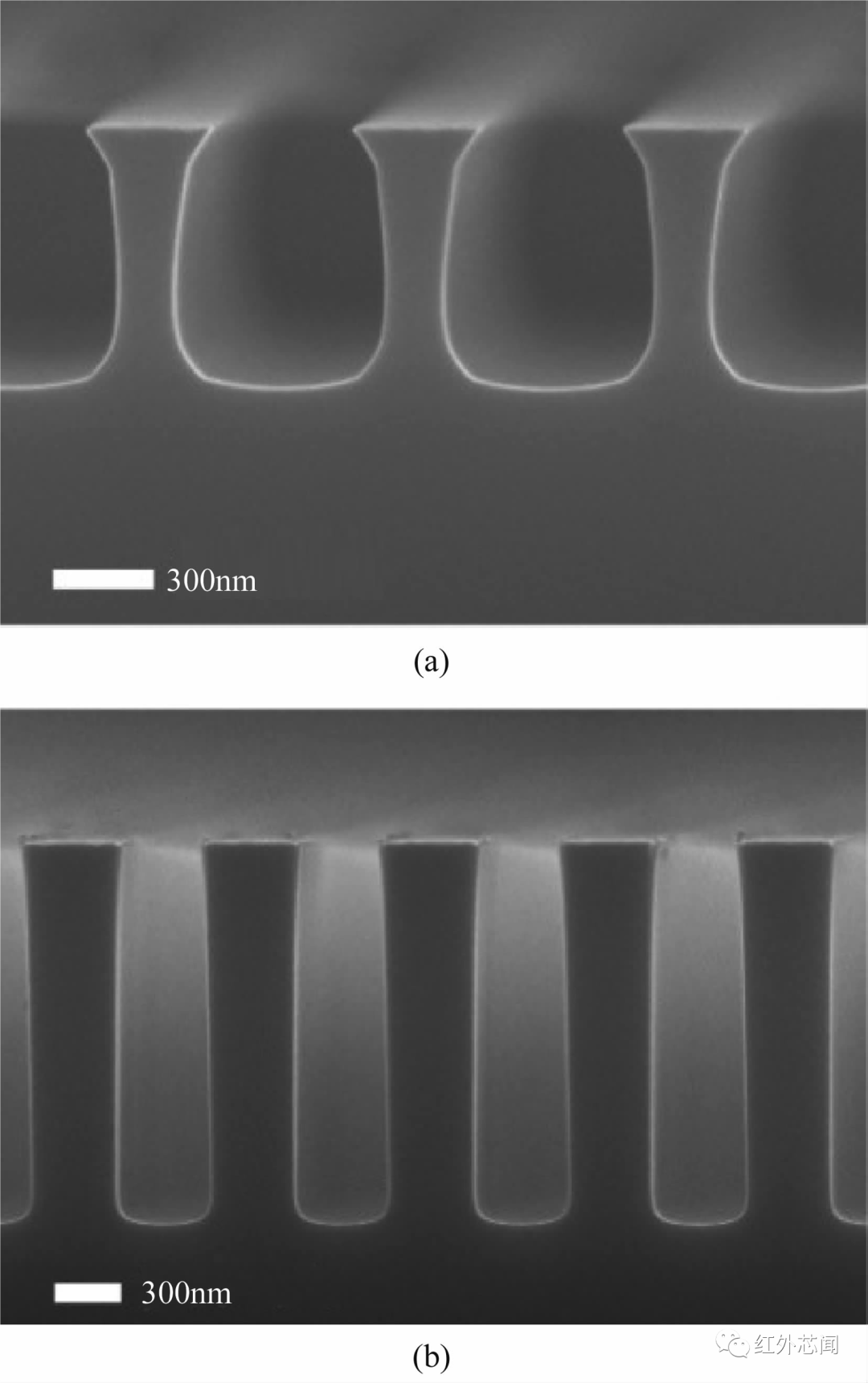

2010年,Volatier M等人針對刻蝕GaAs側(cè)壁出現(xiàn)的橫向刻蝕現(xiàn)象,在Cl?/BCl?/Ar中添加N?以增加側(cè)壁鈍化保護。首先,添加N?后增加的鈍化層可以減少過度的橫向蝕刻,從而產(chǎn)生各向異性剖面。其次,通過研究不同比例N?相關(guān)數(shù)據(jù)可知,加入10%~13%的N?時能夠獲得接近理想的各向異性結(jié)構(gòu)。一旦N?比例超過14%,GaAs的底部就會變得很粗糙。此研究改善了刻蝕GaAs側(cè)壁時出現(xiàn)橫向鉆蝕的情況,如圖8所示。

圖8

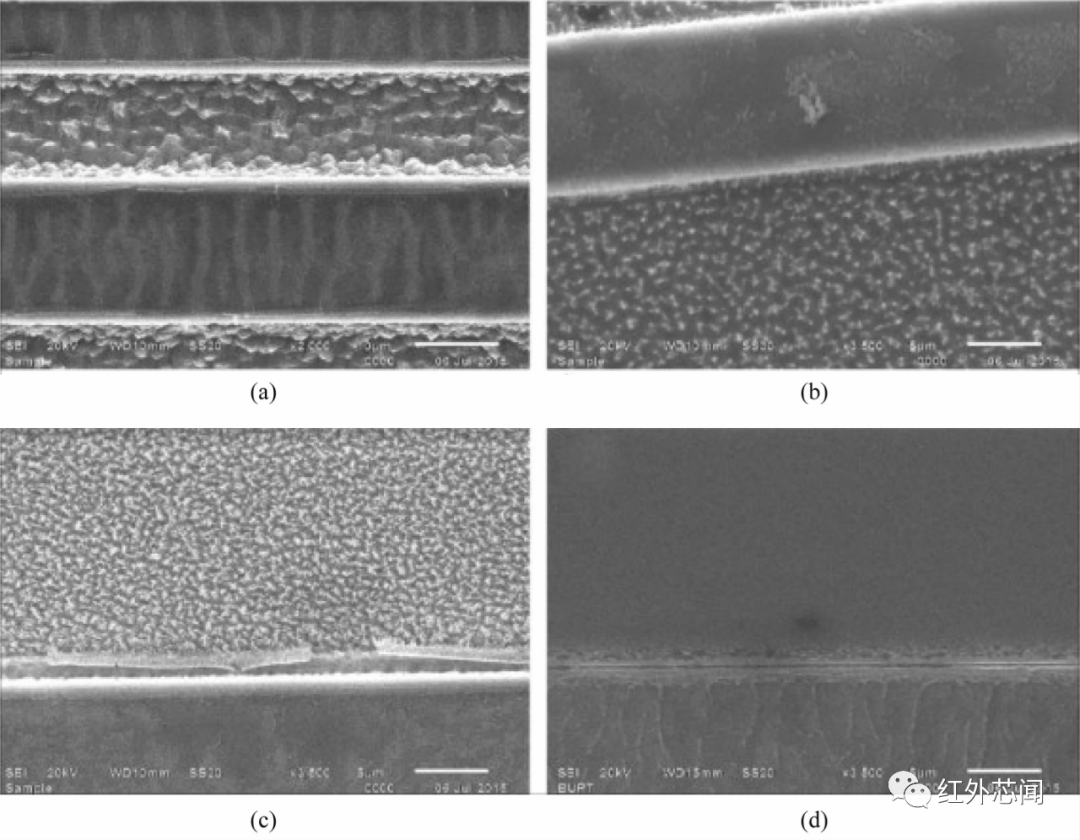

2010年,Lee J W等人針對GaAs在刻蝕后存在表面粗糙的問題,研究了BCl?/N?和BCl?/Ar兩種組合的刻蝕機理。通過調(diào)節(jié)輔助氣體N?和Ar的比例來觀察表面質(zhì)量的好壞(見圖9)。研究發(fā)現(xiàn),添加過量的輔助氣體會降低等離子體刻蝕的速率和選擇性,從而對等離子體刻蝕產(chǎn)生負面影響,最終出現(xiàn)表面粗糙的現(xiàn)象。

圖9

2015年,Liu K等人針對用Cl?/Ar刻蝕GaAs時表面粗糙的問題,通過加入不同濃度的O?來加以對比。他們分析了Cl?/Ar/O?的刻蝕機理,發(fā)現(xiàn)O?的加入使GaAs的刻蝕速率減小,但表面質(zhì)量變高,選擇比變大,改善了GaAs在Cl?/Ar刻蝕下表面粗糙的問題(見圖10)。

圖10

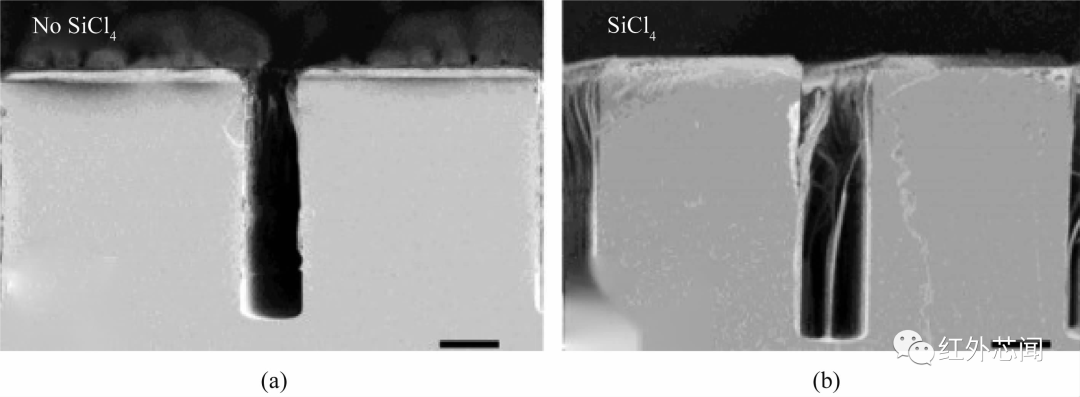

2019年,Booker K等人針對刻蝕GaAs通孔時出現(xiàn)橫向刻蝕的問題,將SiO?用作掩膜,并通過在Cl?/Ar組合中加入SiCl?,來完成刻蝕。這將促進通孔側(cè)壁上的硅基聚合物持續(xù)形成,防止橫向蝕刻再次破壞側(cè)壁,如圖11所示。

圖11

2022年,楊晶晶等人針對刻蝕以SiO?為掩膜時GaAs外延片出現(xiàn)的長草現(xiàn)象(見圖12(a)),分析了刻蝕的機理,找出了刻蝕的副產(chǎn)物。這些副產(chǎn)物會產(chǎn)生“微掩膜”效應,從而影響刻蝕的結(jié)果。通過調(diào)整射頻(RF)功率,增大了等離子體副產(chǎn)物粘附在基片的概率,減少了長草現(xiàn)象的發(fā)生,如圖12(b)所示。

圖12

刻蝕中改善GaAs/AlGaAs選擇性刻蝕的研究現(xiàn)狀

在GaAs/AlGaAs的刻蝕方面,1995年Constantine C等人針對GaAs和AlGaAs刻蝕速率有明顯差異的問題,采用1:10的BCl?/Ar氣體組合,發(fā)現(xiàn)BCl?可以去除鋁氧化物,并在反應腔室內(nèi)吸收水蒸氣,防止AlGaAs的再次氧化,獲得了更均勻的非選擇性刻蝕。

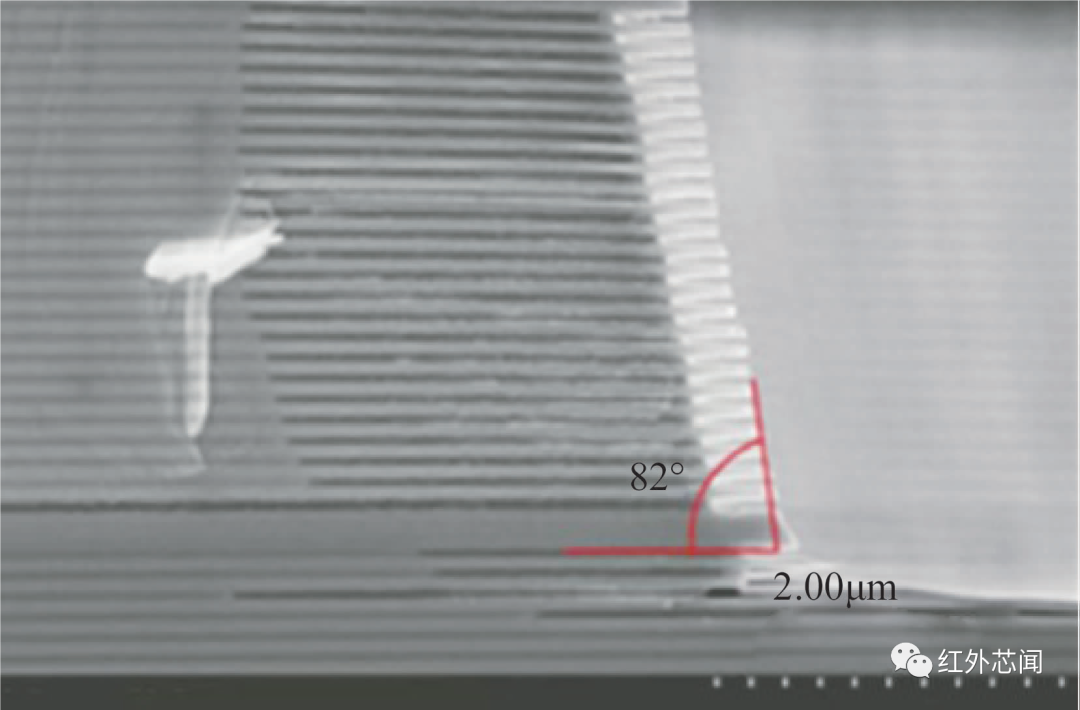

2018年,Vigneron P B等人針對GaAs/AlAs異質(zhì)結(jié)刻蝕過程中出現(xiàn)的橫向鉆蝕問題(見圖13),在BCl?/Cl?/Ar刻蝕氣體組合中加入N?誘導的鈍化層,可以防止橫向蝕刻,從而產(chǎn)生光滑且?guī)缀趵硐氲拇怪眰?cè)壁。針對金屬掩膜和光刻膠掩膜的微掩膜效應,通過加入Ar氣帶走這些反應副產(chǎn)物。為了解決損傷問題,他們加入N?作為輔助氣體,結(jié)果是微掩膜效應完全消失。等離子體中的N?濃度提高了刻蝕剖面的平滑性。接著增加BCl?,氣體以降低腐蝕速率,同時增加壓力以提高選擇性,得到了側(cè)壁垂直且光滑的形貌。

圖13 GaAs/AlAs側(cè)壁的SEM圖像

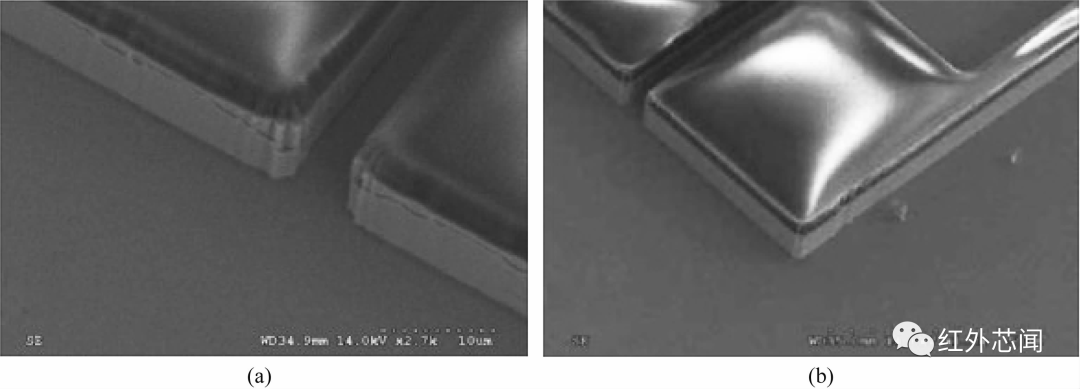

2019年,王宇等人針對GaAs/AlAs側(cè)壁的橫向鉆蝕問題和VCSEL基腳不平坦問題,采用SiO?硬掩膜并調(diào)整ICP源功率和RF功率兩個參數(shù),在保證高刻蝕速率的條件下,得到了側(cè)壁角度為60°~70°且側(cè)壁光滑的形貌。調(diào)節(jié)腔室內(nèi)壓強的大小,減少了反應的副產(chǎn)物,改善了臺面的平坦度,降低了基腳效應(見圖14)。

圖14 優(yōu)化后的側(cè)壁和基腳

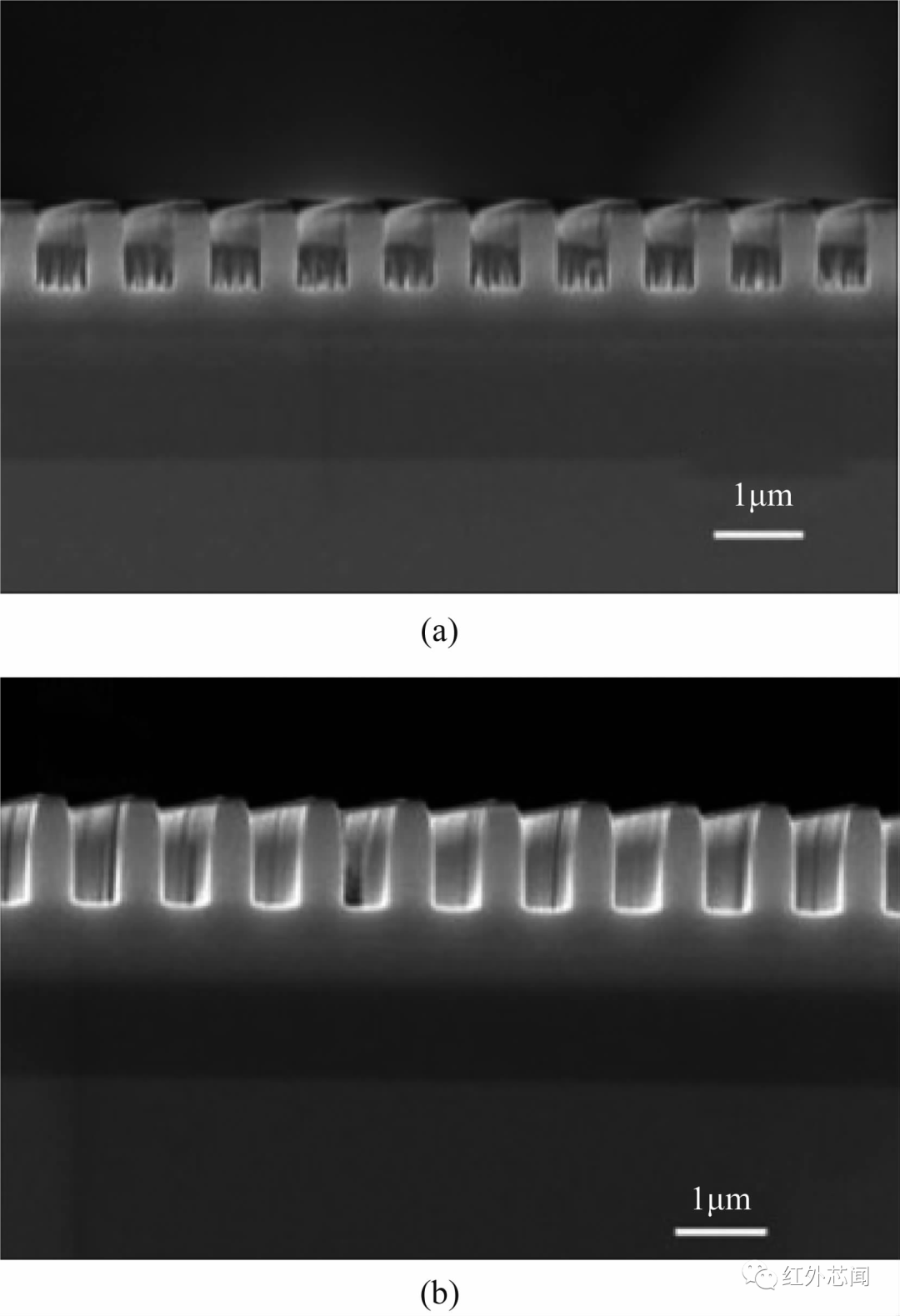

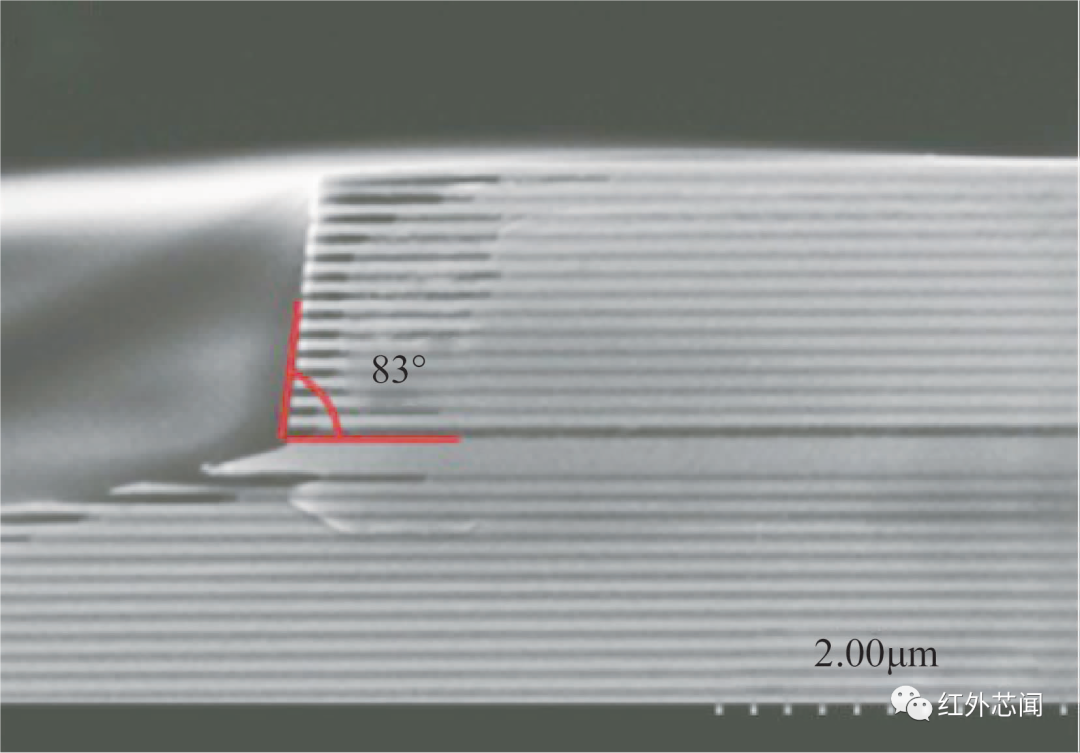

2020年,張秋波等人針對ICP刻蝕氧化限制型VCSEL時出現(xiàn)的選擇性刻蝕(鏤空)現(xiàn)象(見圖15),用SiO?掩膜刻蝕VCSEL,通過調(diào)整RF功率增強刻蝕中的物理效應;通過調(diào)整BCl?,氣體的流量組分,使VCSEL的側(cè)壁鈍化效果增強;采用ICP刻蝕時增強了RF功率,使反應腔室內(nèi)達到化學和物理效應的動態(tài)平衡;增強的物理刻蝕轟擊掉鏤空的部分,如圖16所示。

圖15和圖16

結(jié)束語

本文對VCSEL干法刻蝕關(guān)鍵技術(shù)的進展和研究現(xiàn)狀進行了綜述(主要包括刻蝕時掩膜的質(zhì)量、刻蝕GaAs后的表面質(zhì)量、VCSEL的表面和側(cè)壁形貌)。目前,國際上對VCSEL刻蝕技術(shù)進行了廣泛而深入的研究,在制備掩膜、增強GaAs的各向異性刻蝕以及實現(xiàn)多層分布式布拉格反射器(DBR)的非選擇性刻蝕方面取得了重要進展。但針對介質(zhì)掩膜的優(yōu)化和去殘膠工藝、刻蝕氣體與材料的作用機理及規(guī)律、刻蝕過程中出現(xiàn)的副產(chǎn)物問題等研究較少。隨著各個領(lǐng)域?qū)CSEL的需求增大,對VCSEL刻蝕技術(shù)的精度也會提出更高的要求。

審核編輯:劉清

-

SEM

+關(guān)注

關(guān)注

0文章

257瀏覽量

14839 -

GaAs

+關(guān)注

關(guān)注

3文章

891瀏覽量

23843 -

激光雷達

+關(guān)注

關(guān)注

971文章

4218瀏覽量

192439 -

vcsel技術(shù)

+關(guān)注

關(guān)注

0文章

6瀏覽量

939

原文標題:綜述:GaAs基VCSEL干法刻蝕技術(shù)研究

文章出處:【微信號:MEMSensor,微信公眾號:MEMS】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

一文詳解干法刻蝕工藝

半導體刻蝕工藝技術(shù)-icp介紹

干法刻蝕的概念、碳硅反應離子刻蝕以及ICP的應用

上海伯東IBE離子束刻蝕機介紹

半導體濕法和干法刻蝕

干法刻蝕時側(cè)壁為什么會彎曲

芯片制造中的濕法刻蝕和干法刻蝕

干法刻蝕側(cè)壁彎曲的原因及解決方法

晶圓表面溫度對干法刻蝕的影響

干法刻蝕工藝的不同參數(shù)

為什么干法刻蝕又叫低溫等離子體刻蝕

半導體干法刻蝕技術(shù)解析

半導體芯片制造技術(shù)之干法刻蝕工藝詳解

GaAs基VCSEL干法刻蝕技術(shù)研究

GaAs基VCSEL干法刻蝕技術(shù)研究

評論