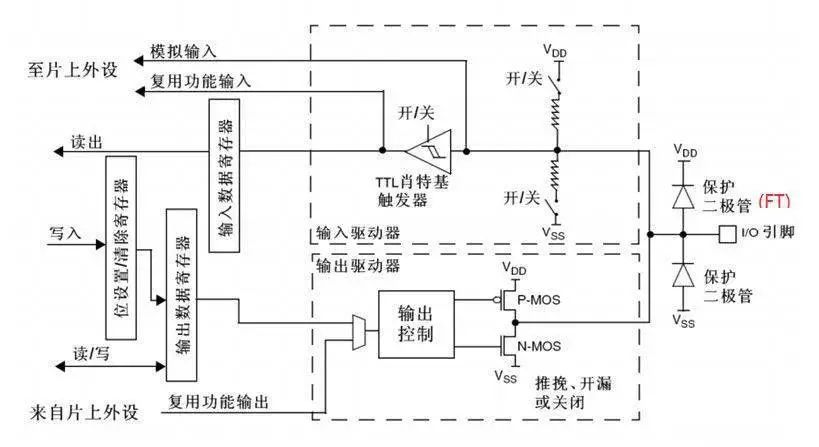

每個(gè)GPIO內(nèi)部都有這樣的一個(gè)電路結(jié)構(gòu),這個(gè)結(jié)構(gòu)在本文下面會(huì)具體介紹。

這邊的電路圖稍微提一下:

保護(hù)二極管:IO引腳上下兩邊兩個(gè)二極管用于防止引腳外部過高、過低的電壓輸入。當(dāng)引腳電壓高于VDD時(shí),上方的二極管導(dǎo)通;當(dāng)引腳電壓低于VSS時(shí),下方的二極管導(dǎo)通,防止不正常電壓引入芯片導(dǎo)致芯片燒毀。但是盡管如此,還是不能直接外接大功率器件,須加大功率及隔離電路驅(qū)動(dòng),防止燒壞芯片或者外接器件無法正常工作。

P-MOS管和N-MOS管:由P-MOS管和N-MOS管組成的單元電路使得GPIO具有“推挽輸出”和“開漏輸出”的模式。這里的電路會(huì)在下面很詳細(xì)地分析到。

TTL肖特基觸發(fā)器:信號經(jīng)過觸發(fā)器后,模擬信號轉(zhuǎn)化為0和1的數(shù)字信號。但是,當(dāng)GPIO引腳作為ADC采集電壓的輸入通道時(shí),用其“模擬輸入”功能,此時(shí)信號不再經(jīng)過觸發(fā)器進(jìn)行TTL電平轉(zhuǎn)換。ADC外設(shè)要采集到的原始的模擬信號。

下面將具體介紹GPIO的這八種工作方式:

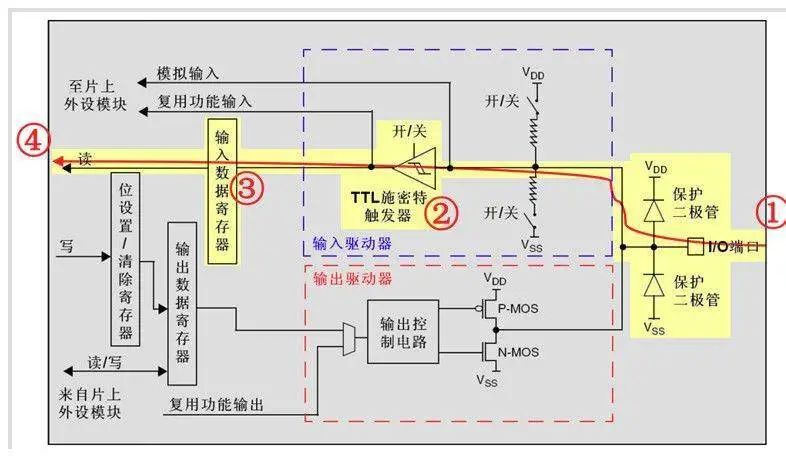

浮空輸入模式

浮空輸入模式下,I/O端口的電平信號直接進(jìn)入輸入數(shù)據(jù)寄存器。也就是說,I/O的電平狀態(tài)是不確定的,完全由外部輸入決定;如果在該引腳懸空(在無信號輸入)的情況下,讀取該端口的電平是不確定的。

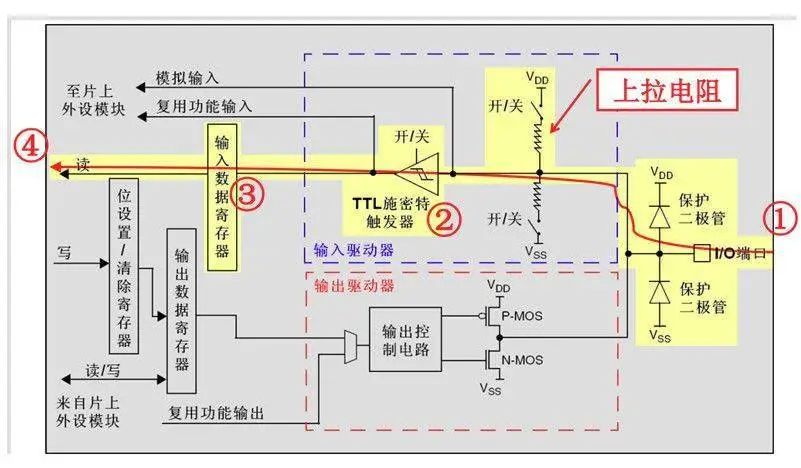

上拉輸入模式

上拉輸入模式下,I/O端口的電平信號直接進(jìn)入輸入數(shù)據(jù)寄存器。但是在I/O端口懸空(在無信號輸入)的情況下,輸入端的電平可以保持在高電平;并且在I/O端口輸入為低電平的時(shí)候,輸入端的電平也還是低電平。

下拉輸入模式

下拉輸入模式下,I/O端口的電平信號直接進(jìn)入輸入數(shù)據(jù)寄存器。但是在I/O端口懸空(在無信號輸入)的情況下,輸入端的電平可以保持在低電平;并且在I/O端口輸入為高電平的時(shí)候,輸入端的電平也還是高電平。

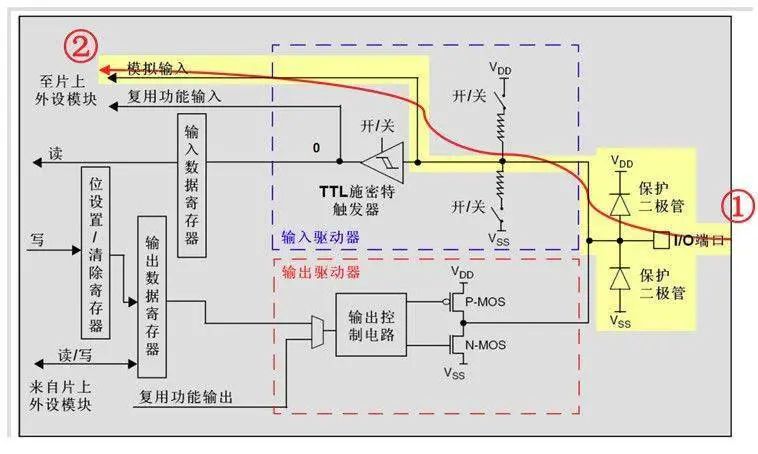

模擬輸入模式

模擬輸入模式下,I/O端口的模擬信號(電壓信號,而非電平信號)直接模擬輸入到片上外設(shè)模塊,比如ADC模塊等等。

開漏輸出模式

開漏輸出模式下,通過設(shè)置位設(shè)置/清除寄存器或者輸出數(shù)據(jù)寄存器的值,途經(jīng)N-MOS管,最終輸出到I/O端口。這里要注意N-MOS管,當(dāng)設(shè)置輸出的值為高電平的時(shí)候,N-MOS管處于關(guān)閉狀態(tài),此時(shí)I/O端口的電平就不會(huì)由輸出的高低電平?jīng)Q定,而是由I/O端口外部的上拉或者下拉決定;當(dāng)設(shè)置輸出的值為低電平的時(shí)候,N-MOS管處于開啟狀態(tài),此時(shí)I/O端口的電平就是低電平。同時(shí),I/O端口的電平也可以通過輸入電路進(jìn)行讀取;注意,I/O端口的電平不一定是輸出的電平。

開漏復(fù)用輸出模式

開漏復(fù)用輸出模式,與開漏輸出模式很是類似。只是輸出的高低電平的來源,不是讓CPU直接寫輸出數(shù)據(jù)寄存器,取而代之利用片上外設(shè)模塊的復(fù)用功能輸出來決定的。

總結(jié)與分析

1、什么是推挽結(jié)構(gòu)和推挽電路?

推挽結(jié)構(gòu)一般是指兩個(gè)參數(shù)相同的三極管或MOS管分別受兩互補(bǔ)信號的控制,總是在一個(gè)三極管或MOS管導(dǎo)通的時(shí)候另一個(gè)截止。高低電平由輸出電平?jīng)Q定。

推挽電路是兩個(gè)參數(shù)相同的三極管或MOSFET,以推挽方式存在于電路中,各負(fù)責(zé)正負(fù)半周的波形放大任務(wù)。電路工作時(shí),兩只對稱的功率開關(guān)管每次只有一個(gè)導(dǎo)通,所以導(dǎo)通損耗小、效率高。輸出既可以向負(fù)載灌電流,也可以從負(fù)載抽取電流。推拉式輸出級既提高電路的負(fù)載能力,又提高開關(guān)速度。

2、開漏輸出和推挽輸出的區(qū)別?

開漏輸出:只可以輸出強(qiáng)低電平,高電平得靠外部電阻拉高。輸出端相當(dāng)于三極管的集電極。適合于做電流型的驅(qū)動(dòng),其吸收電流的能力相對強(qiáng)(一般20ma以內(nèi));

推挽輸出:可以輸出強(qiáng)高、低電平,連接數(shù)字器件。

關(guān)于推挽輸出和開漏輸出,最后用一幅最簡單的圖形來概括:

該圖中左邊的便是推挽輸出模式,其中比較器輸出高電平時(shí)下面的PNP三極管截止,而上面NPN三極管導(dǎo)通,輸出電平VS+;當(dāng)比較器輸出低電平時(shí)則恰恰相反,PNP三極管導(dǎo)通,輸出和地相連,為低電平。右邊的則可以理解為開漏輸出形式,需要接上拉。

-

MOS管

+關(guān)注

關(guān)注

109文章

2552瀏覽量

70489 -

信號完整性

+關(guān)注

關(guān)注

68文章

1440瀏覽量

96663 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2039瀏覽量

62063 -

GPIO

+關(guān)注

關(guān)注

16文章

1280瀏覽量

53925 -

TTL電平

+關(guān)注

關(guān)注

1文章

116瀏覽量

12355

發(fā)布評論請先 登錄

信號完整性學(xué)習(xí)筆記

信號完整性與電源完整性仿真分析

信號完整性設(shè)計(jì)中的5類典型問題(于博士信號完整性)

信號完整性與電源完整性的仿真

信號完整性與電源完整性-電源完整性分析

聽懂什么是信號完整性

信號完整性學(xué)習(xí)筆記之GPIO原理

信號完整性學(xué)習(xí)筆記之GPIO原理

評論