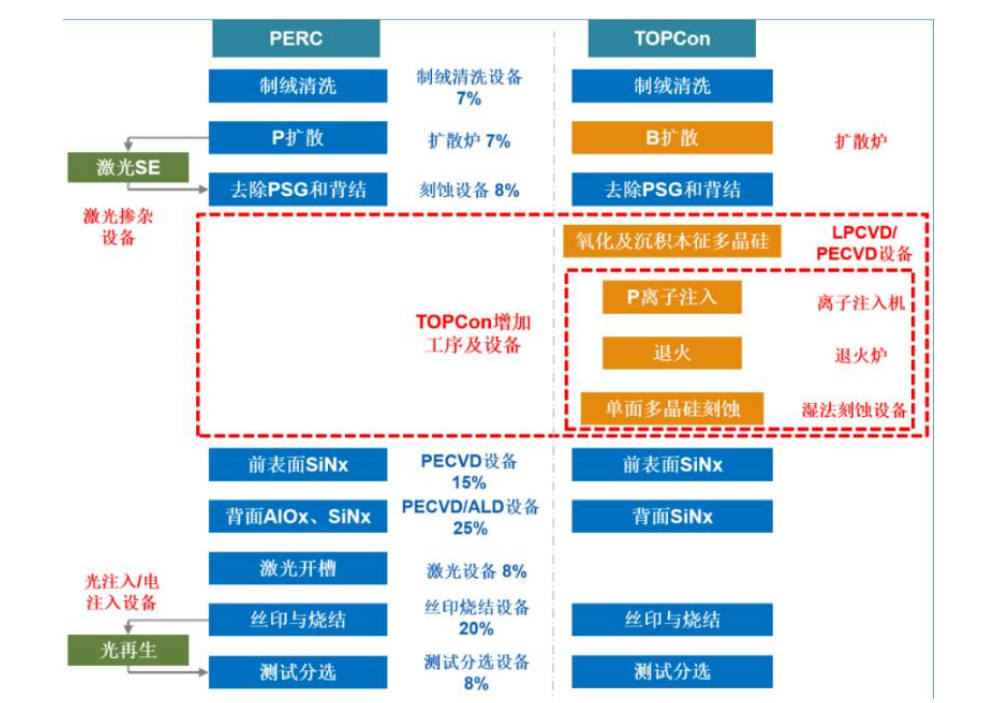

TOPCon 電池的制備工序包括清洗制絨、正面硼擴散、BSG 去除和背面刻蝕、氧化層鈍化接觸制備、正面氧化鋁沉積、正背面氮化硅沉積、絲網印刷、燒結和測試分選,約 12 步左右。從技術路徑角度:LPCVD 方式為目前量產的主流工藝,預計 PECVD 路線有望成為未來新方向。

圖片來源:浙商證券

1. SE激光摻雜工序

N型TOPCon電池生產工藝采用高效選擇性發射結(Selective Emitter,即SE)技術,這一道工序位于清潔制絨、硼擴散之后,其原理是利用激光的熱效應,熔融硅片表層,覆蓋在發射極頂部的硼硅玻璃中的B原子進入硅片表層,B原子在液態硅中的擴散系數要比在固態硅中的擴散高數個數量級,固化后摻雜B原子取代硅原子的位置,形成重摻雜層。通過激光在硅片與金屬柵線接觸部位進行高濃度摻雜,以達到降低該部位接觸電阻的目的;在電極以外的位置進行低濃度摻雜,以達到降低擴散層復合的目的。通過以上方式優化發射極,進而實現轉化效率的增加,與TOPCon電池疊加有效實現量產情況下0.2%-0.4%的轉化效率提升。

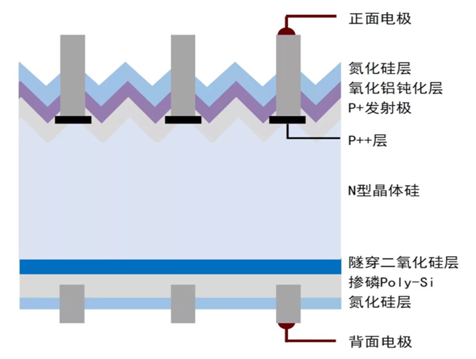

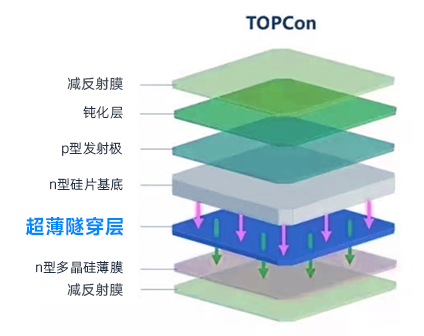

2.制備隧穿氧化層及多晶硅層工序

TOPCon電池核心流程就是制作隧穿氧化層、多晶硅層環節部分,制備隧穿氧化層與多晶硅層環節是在N型硅片的背面沉積一層1-2nm的氧化硅膜和一層100-150nm的摻雜非晶硅薄膜,非晶硅薄膜在后續退火過程中結晶性發生變化,由微晶非晶混合相轉變為多晶,激活疊層薄膜的鈍化性能,在疊層薄膜上沉積金屬,就可以得到無需開孔的鈍化接觸結構。

按兩層膜制備方式不同可以分為LPCVD、PECVD、PVD。LPCVD是把隧穿氧化層、本征非晶硅層制備完成以后增加P擴散和清洗工藝;PECVD是把隧穿氧化層原位摻雜做成非晶硅層,兩層膜制備的步驟合并到了一起,然后進行褪火、清洗;PECVD和LPCVD最根本區別就是兩層膜是分步還是合并制作。

按兩層膜制備方式不同可以分為LPCVD、PECVD、PVD。LPCVD是把隧穿氧化層、本征非晶硅層制備完成以后增加P擴散和清洗工藝;PECVD是把隧穿氧化層原位摻雜做成非晶硅層,兩層膜制備的步驟合并到了一起,然后進行褪火、清洗;PECVD和LPCVD最根本區別就是兩層膜是分步還是合并制作。

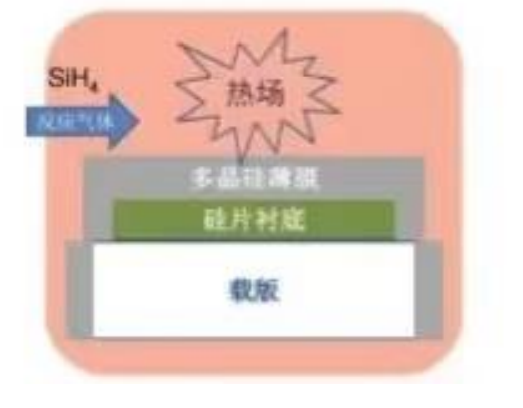

LPVCD工藝介紹:LPCVD全稱為低壓力化學氣相沉積法,利用 LPCVD 設備通過熱氧化方式生長氧化硅層并沉積多晶硅,然后在多晶硅中摻入磷制成 PN結,形成鈍化接觸結構。這一技術路線出現時間最早,工藝成熟度高,具有成膜質量高、產能高等優勢。但是,存在繞鍍問題,且沉積時使用的石英管需進行清洗維護和定期更換,耗材成本較高;針對繞度問題,目前在工藝上一些廠商已經有了比較好的解決方式。LPCVD法是目前 TOPCon 廠商選擇的主流路線,采用這一路線的主要光伏廠商有晶科能源、捷泰、一道等。LPCVD設備廠家有拉普拉斯、捷佳偉創,拉普拉斯是最主要廠商,捷佳偉創也做這塊,但不作為主推的設備。

LPVCD工藝原理圖 來源:浙商證券

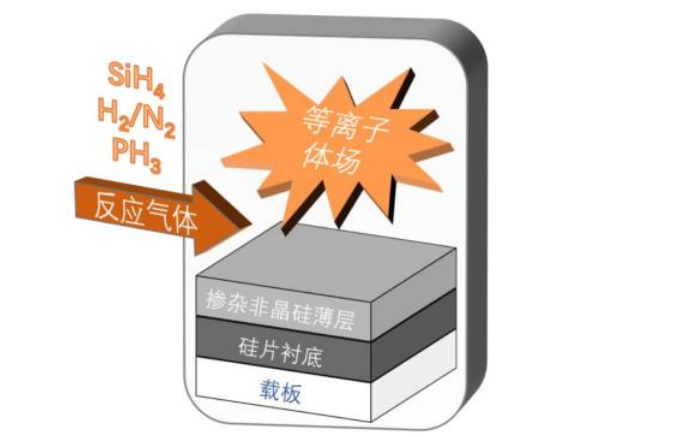

PECVD工藝介紹:PECVD 原位摻雜,又稱PE-poly工藝,全稱為等離子體增強化學氣相沉積法,原理為借助射頻將含反應氣體在局部形成等離子體,利用等離子體的強化學活性在基片表面沉積出薄膜。PECVD 可實現成本的大幅下降,具有繞鍍輕微、成品率高,成膜速度快,摻雜效率高,無石英管,耗材成本低等優勢,但存在成膜厚度均勻性差、膜層致密度不高、易爆膜等問題,原因在于其中有氫氣參與反應。

PECVD工藝原理圖 來源:浙商證券

3.制備減反射膜工序

采用多層介質膜結構技術進行電池片兩面減反射膜的制備,減反射膜由氧化硅(SiOx)/氮氧化硅(SiONx)/氮化硅(SiNx)多層薄膜共同組成,顧名思義減反射膜具有幫助電池片提升對太陽光的吸收,減少光學損失提高光生電流,進而提高轉換效率的效果。更為重要的是,減反射膜還具有鈍化作用,在薄膜形成過程中產生的氫原子對電池表面的鈍化降低了發射結的表面復合速率,促進光電轉換效率提升的同時延長電池的使用壽命。

正面的減反射膜還能對前序步驟沉積的氧化鋁層(4-5nm)起到一定的保護作用,氮化硅薄膜的高致密性可以保護氧化鋁不受損傷及污染。而背面減反膜同樣也可用于背部膜層的保護,避免poly層受到破壞及污染。多層結構共同作用,達到良好的體鈍化和表面鈍化效果,實現更佳的鈍化接觸。

4.激光誘導燒結工序

在電池制造中全新引入了激光輔助燒結工序,在完成絲印、燒結及光注入工序后,采用激光誘導燒結技術(Laser Induced Firing,簡稱“LIF”)。

通過激光輔助快速燒結對硅片正面的金屬漿料進行處理,使硅片正面的漿料和硅片形成較好的歐姆接觸。同時,利用荷電效應來優化柵線電極、改善接觸電阻并實現高效率太陽能光伏電池的輸出,從而顯著提升TOPCon電池光電效率。

在TOPCon電池的工藝驗證結果顯示,LIF技術可以有效提升電池片的光電轉換效率,增益在0.2%以上。

TOPCon產線成本分析

TOPCon電池可在PERC產線基礎上升級改造,單GW初始投資額為1.5-1.7億左右,基于PERC產線升級成本為4,000-5,000萬/GW。

與P型電池相比,TOPCon將磷擴散改為了硼擴散,增加了隧穿層、POLY層的制備,取消了激光開槽步驟。

初始設備投資中,清洗制絨設備800萬元,占比約5%;硼擴散爐成本約2,000萬,占比約12%;刻蝕設備成本1,200萬,占比約7%;背面隧穿氧化及多晶硅摻雜相關設備約4,500萬(lpcvd)和3,500萬(pecvd);雙面減反膜設備成本約3,200萬,占比20%;絲印設備成本約3,500萬,占比22%。此外,2020年后的PERC產能在預留機位的情況下,能進行改造升級,升級成本約為4,000-5,000萬/GW,主要是氧化隧穿、磷摻雜設備成本。2024新型光伏電池及組件技術論壇將重點討論TOPCon產業技術突破以及裝備創新,屆時將有通威太陽能、正泰新能科技股份有限公司、深圳市捷佳偉創新能源裝備股份有限公司、華晟新能源科技有限公司、西安寶馨光能科技有限公司、廣東脈絡能源科技有限公司等知名企業齊聚共論鈣鈦礦產業化議題。

審核編輯:黃飛

-

原理圖

+關注

關注

1325文章

6414瀏覽量

240041 -

光伏電池

+關注

關注

5文章

268瀏覽量

33059 -

激光

+關注

關注

20文章

3456瀏覽量

66095

原文標題:TOPCon核心工藝技術路線盤點與產線成本分析

文章出處:【微信號:DT-Semiconductor,微信公眾號:DT半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Sic mesfet工藝技術研究與器件研究

晶圓凸起封裝工藝技術簡介

半導體工藝技術的發展趨勢

半導體工藝技術的發展趨勢是什么?

0.16微米CMOS工藝技術

IGBT核心技術及人才缺失 工藝技術缺乏

什么是CPU的生產工藝技術/向下兼容?

曝光成像與顯影工藝技術的原理及特點

SONNET中的工藝技術層介紹

ALD和ALE核心工藝技術對比

TOPCon核心工藝技術路線盤點

TOPCon核心工藝技術路線盤點

評論