CMOS是一種常見的邏輯門電路,它使用CMOS技術來實現數字邏輯功能。在CMOS電路中,輸入端接電阻后接地的情況下,一般情況下是低電平。

首先,讓我們先了解一下CMOS電路的基本原理。CMOS(互補金屬氧化物半導體)技術利用了兩種類型的晶體管:NMOS(負極性金屬氧化物半導體)晶體管和PMOS(正極性金屬氧化物半導體)晶體管。NMOS晶體管只有有源端施加高電平時才能導通,而PMOS晶體管只有有源端施加低電平時才能導通。這種互補配置使得CMOS電路能夠實現高噪聲容忍性、低功耗和寬電源電壓范圍等優點。

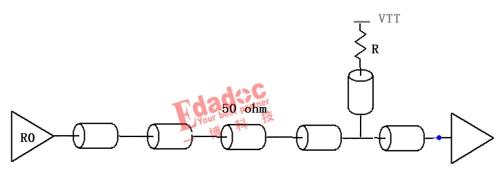

在CMOS電路中,輸入端接電阻后接地時,電阻和接地構成了一個電路路徑。由于接地是一個恒定的低電平,根據CMOS的工作原理,當輸入信號不受到其他因素干擾時,輸入端將會是低電平。

接下來,讓我們更詳細地探討一下為什么輸入端會是低電平。

首先,輸入端接地是指將輸入信號通過電阻連接到接地點。由于接地被視為電路的參考點,其電位為零。因此,在沒有任何干擾的情況下,輸入端引腳處于接地電位,也就是低電平。另外,由于CMOS電路的輸入電阻很高,電流通過電阻非常小,可以近似認為為零。

第二,由于CMOS電路采用了互補設計,NMOS和PMOS晶體管在輸入信號的不同電平下有不同的導通狀態。在輸入端接地的情況下,輸入信號為低電平時,NMOS晶體管導通,PMOS晶體管斷開。此時,由于NMOS晶體管導通,電流會通過電阻流向接地,從而使得電源電壓迫使輸入端維持在地電平。因此,輸入端接地的情況下,CMOS電路實現了低電平輸入。

總結來說,當CMOS電路的輸入端接電阻后接地時,一般情況下是低電平。這是因為接地作為電路的參考點,電勢為零,而CMOS電路的輸入電阻較高,電流通過電阻非常小,可以近似為零。另外,由于互補設計,NMOS晶體管在低電平輸入時導通,PMOS晶體管斷開,使得電源電壓迫使輸入端維持在地電平。

然而,需要注意的是,以上是在理想條件下的情況。實際上,電路中會存在一些因素,如電源噪聲、母線電阻等,可能導致輸入端不完全維持在地電平,因此在設計和實際應用中需要考慮這些因素。

-

CMOS

+關注

關注

58文章

6001瀏覽量

238351 -

電阻

+關注

關注

87文章

5614瀏覽量

174536 -

晶體管

+關注

關注

77文章

9995瀏覽量

140994 -

低電平

+關注

關注

1文章

176瀏覽量

13625

發布評論請先 登錄

cmos輸入端接電阻后接地是低電平嗎

cmos輸入端接電阻后接地是低電平嗎

評論