隨著聯(lián)網(wǎng)設(shè)備數(shù)量的不斷增加,安全設(shè)計不再只是一個附加優(yōu)勢,更是所有數(shù)字化產(chǎn)品的必備要素。

工業(yè)、汽車、醫(yī)療、航空電子和政府等眾多領(lǐng)域早已確立了安全標(biāo)準(zhǔn)。現(xiàn)今,安全重點轉(zhuǎn)向了所有聯(lián)網(wǎng)產(chǎn)品。歐盟在 2024 年底通過的《網(wǎng)絡(luò)彈性法案》 (Cyber Resilience Act) 便是這一趨勢的例證。設(shè)計工程師不得不花費更多的時間來學(xué)習(xí)如何增強產(chǎn)品安全性,而無法完全專注于設(shè)計本身。

幸運的是,對于 FPGA 用戶而言,Altera 早在十多年前就已在其產(chǎn)品中內(nèi)置了出色的安全功能,客戶只需啟用這些功能,即可實現(xiàn)高水平的安全性。而對于那些正在為其新設(shè)計尋求 FPGA 的設(shè)計工程師來說,即便是小型的 Altera 設(shè)備,亦可幫助他們有力地抵御常見威脅。

如今的安全需求不再局限于加密支持,而可大致劃分為三大類:設(shè)計安全、數(shù)據(jù)安全和供應(yīng)鏈安全。

設(shè)計安全需求

此需求須確保在產(chǎn)品的整個生命周期內(nèi)都擁有全面的控制能力,這可通過精心設(shè)計的系統(tǒng)安全方案來達成,通常側(cè)重于系統(tǒng)中智能化水平最高的設(shè)備。在系統(tǒng)開機時,智能設(shè)備必須能夠安全啟動,并為設(shè)備自身及其周圍的系統(tǒng)建立信任根 (ROT)。

Altera 設(shè)備具備多項設(shè)計安全功能,這些功能在 ROT 建立后即可使用。例如,Agilex 設(shè)備內(nèi)置了最新版安全設(shè)備管理器 (SDM)。SDM 是一種靈活的安全子系統(tǒng),它會先啟動并建立 ROT,然后為整個系統(tǒng)提供安全服務(wù)。

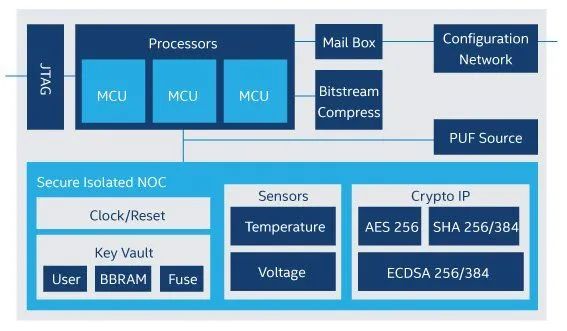

圖 1 展示了 Agilex 7 家族所含 SDM 的高級框圖。這一功能強大的子系統(tǒng)可以利用冗余處理器,自開機起即運行 FPGA 的安全功能。SDM 負責(zé)執(zhí)行多種任務(wù),包括 FPGA 和 HPS 的安全配置、加密密鑰和操作的安全處理、篡改檢測、單粒子翻轉(zhuǎn) (SEU) 監(jiān)控等。

圖 1:Agilex 7 設(shè)備中的安全設(shè)備管理器 (SDM)

系統(tǒng)部署完成后,如何確保其未被入侵呢?這就需要利用 SDM 的另一項獨特功能:認證功能 (Attestation)。驗證 (authentication) 環(huán)節(jié)負責(zé)驗證并批準(zhǔn) FPGA 或軟件映像啟動,而認證 (attestation) 功能則提供與之相關(guān)的功能,要求系統(tǒng)必須證明其身份和狀態(tài),以證實其未被篡改。這項功能可隨時調(diào)用,作為系統(tǒng)所有者進行系統(tǒng)增強的一道“關(guān)口”,或是在認證失敗時啟用緩解措施的一項測試。

數(shù)據(jù)安全需求

作為第二大類需求,旨在保護系統(tǒng)處理或傳輸?shù)乃袛?shù)據(jù)。如前所述,SDM 擁有一個具備多種算法的加密引擎,可以幫助保護 FPGA 邏輯結(jié)構(gòu)或 FPGA 嵌入式 ARM 硬核處理器系統(tǒng) (HPS) 所觸及的“敏感”數(shù)據(jù)。這些加密服務(wù)不僅包括可為數(shù)據(jù)存儲提供加密的安全數(shù)據(jù)對象存儲 (SDOS),還包括基于 HMAC 的簽名生成和驗證,可助力確保數(shù)據(jù)的完整性和真實性。SDM 還提供其他類似功能,可用于 HPS 或 FPGA 邏輯結(jié)構(gòu)所處理的各種數(shù)據(jù),并可在密碼、完整性和身份驗證等多種所需功能中使用 AES、HMAC、SHA-2 和 ECDSA 算法。

部分 Agilex 7 設(shè)備[1] 還提供 MACsec IP 解決方案,每個實例的運行速度高達 200 Gbps(半雙工)。該功能采用了現(xiàn)有的 AES 硬核加速器模塊,而該模塊也可用于其他 IP 解決方案。Agilex 7 設(shè)備提供多達 4 個實例,支持高達 800 Gbps 的 MACsec 帶寬。

供應(yīng)鏈安全需求

覆蓋產(chǎn)品的整個生命周期,從為設(shè)計選擇組件開始,貫穿于產(chǎn)品的制造、交付、維護,直至生命周期終結(jié)。為應(yīng)對電子制造生態(tài)系統(tǒng)中的不足,Altera 擴展了安全功能。

例如,在與負責(zé)設(shè)備密鑰編程的第三方原始設(shè)計制造商 (ODM) 合作時,機密性是一個普遍關(guān)注的問題。為解決這一問題,Altera 提供了黑密鑰 (black key) 預(yù)配支持。該功能與 SDM 結(jié)合使用,可讓您無論在何處編程都能安全隱藏設(shè)備密鑰。

另一項能夠從設(shè)備本身增強安全性的功能是物理不可克隆功能 (PUF),類似于數(shù)字指紋。Altera 采用高度安全的制造工藝,可防止內(nèi)部 PUF 密鑰從設(shè)備中外泄,從而增強安全性,以保護重要資產(chǎn)。另外,PUF 密鑰還能證明您購買的是真正的 Altera 產(chǎn)品,而非假冒設(shè)備。

其他供應(yīng)鏈安全功能還包括:

- 安全遠程更新:這一 IP 技術(shù)可讓您在系統(tǒng)部署到客戶方后,仍能對 FPGA 和軟件映像進行安全更新;

- 安全調(diào)試:在無需訪問內(nèi)部 IP、數(shù)據(jù)或系統(tǒng)控制的情況下,從系統(tǒng)中收集調(diào)試所需的數(shù)據(jù);

- 所有權(quán)轉(zhuǎn)讓:設(shè)置多租戶所有權(quán),或?qū)⑺袡?quán)轉(zhuǎn)讓給另一方;

- 報廢處理:以加密方式清除設(shè)備中的獨特機密信息,防止設(shè)備被重新配置。

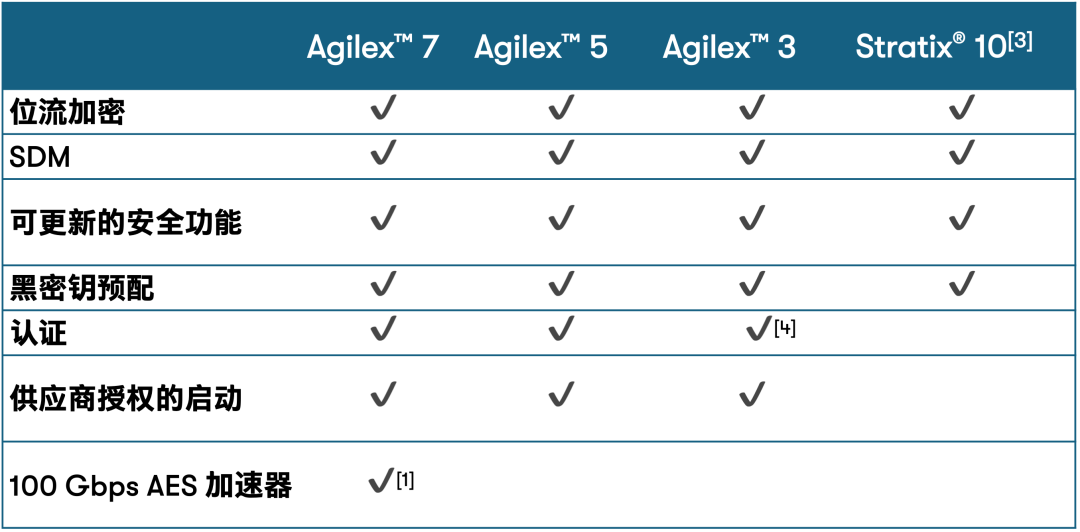

Altera 設(shè)備內(nèi)置安全功能已有十余年。自 2016 年推出安全設(shè)備管理器 (SDM) 以來,Altera 始終致力于為其新添更為先進的功能[2]。憑借其靈活性、穩(wěn)健性和可更新性,SDM 可以幫助客戶構(gòu)建更安全的產(chǎn)品。表 1 概述了本文重點介紹的安全功能。

表 1:近期推出的 Altera 產(chǎn)品家族安全功能矩陣

注:

[1] 僅適用于部分 Agilex 7 設(shè)備系列。

[2] Altera 的安全方法用戶指南 (RDC ID# 724441) 中涵蓋更多其他機密功能。這些內(nèi)容需要簽訂保密協(xié)議 (NDA) 方可披露。該指南還包括關(guān)于如何充分利用這些功能來應(yīng)對威脅環(huán)境。請聯(lián)系 Altera 銷售人員,以獲取該文件以及與安全相關(guān)的其他機密文件。

[3] 安全設(shè)備管理器電路和 IP 在這一產(chǎn)品架構(gòu)中首次實現(xiàn)。

[4] 僅適用于部分 Agilex 3 設(shè)備系列。

-

處理器

+關(guān)注

關(guān)注

68文章

19852瀏覽量

234205 -

FPGA

+關(guān)注

關(guān)注

1644文章

22009瀏覽量

616590 -

Altera

+關(guān)注

關(guān)注

37文章

803瀏覽量

155747

原文標(biāo)題:利用 Altera FPGA 實現(xiàn)更加可靠的全生命周期安全性

文章出處:【微信號:英特爾FPGA,微信公眾號:英特爾FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Altera Agilex 3 FPGA和SoC產(chǎn)品介紹

Intel-Altera FPGA:通信行業(yè)的加速引擎,開啟高速互聯(lián)新時代

Altera發(fā)布最新FPGA產(chǎn)品和開發(fā)工具套件

電子電器產(chǎn)品安全性與針焰試驗的重要性

Altera正式獨立運營:FPGA行業(yè)格局將迎來新變局

如何實現(xiàn) HTTP 協(xié)議的安全性

Altera FPGA為創(chuàng)新設(shè)計提供先進的安全特征

在電氣安裝中通過負載箱實現(xiàn)最大效率和安全性

UWB模塊的安全性評估

智能系統(tǒng)的安全性分析

恒訊科技分析:IPSec與SSL/TLS相比,安全性如何?

固態(tài)電池安全性怎么樣

利用JTAGLOCK特性增強設(shè)備安全性

利用Altera FPGA實現(xiàn)高水平產(chǎn)品安全性

利用Altera FPGA實現(xiàn)高水平產(chǎn)品安全性

評論