文章來源:Tom聊芯片智造

原文作者:Tom

本文主要講述為什么芯片制造常用P型硅。

從早期的平面 CMOS 工藝到先進的 FinFET,p 型襯底在集成電路設(shè)計中持續(xù)被廣泛采用。為什么集成電路的制造更偏向于P型硅?

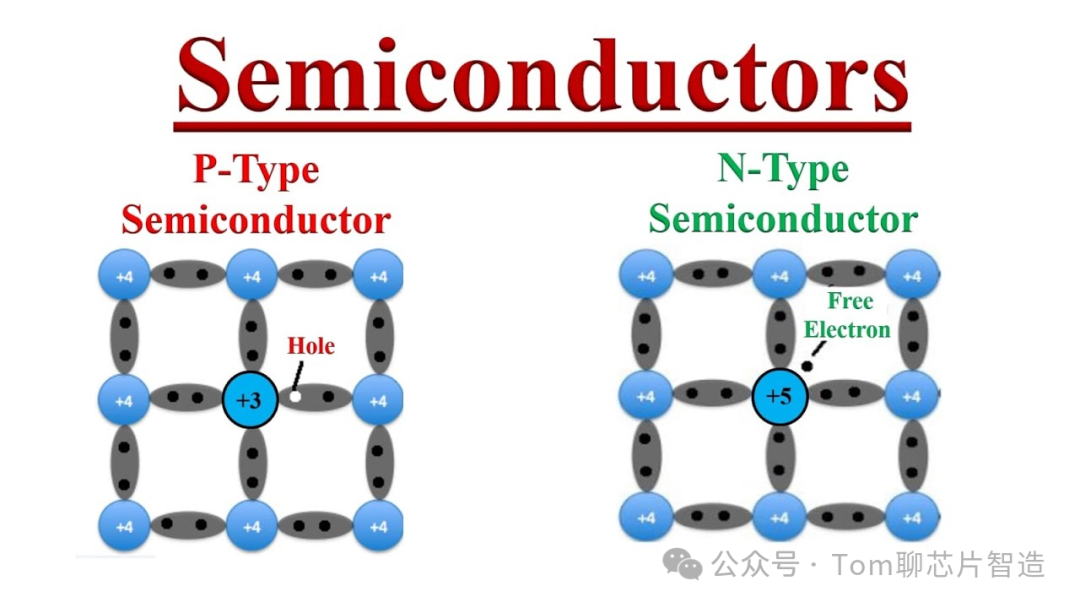

什么是P型硅與N型硅?

在本征硅中,導(dǎo)電能力很差;向其中摻入五價元素(如磷 P、砷 As、銻 Sb)后,會多出一個“自由電子”;這些自由電子能自由移動 → 形成電子導(dǎo)電為主的半導(dǎo)體,稱為N型硅。

摻雜三價元素(如硼 B),由于硼原子比硅少一個價電子 → 會在晶格中形成“空穴”;這些空穴可以自由移動,成為多數(shù)載流子,用于構(gòu)建NMOS器件。

采用P型硅的歷史和實用原因?

1, NMOS器件早期主導(dǎo)

在70~80年代,早期數(shù)字電路多采用NMOS-only 邏輯電路。

NMOS結(jié)構(gòu)速度快、易于制作,直接構(gòu)建在P型襯底上即可,不需要額外的阱(well)結(jié)構(gòu);

所以:P型襯底就是天然支持NMOS器件的基底。

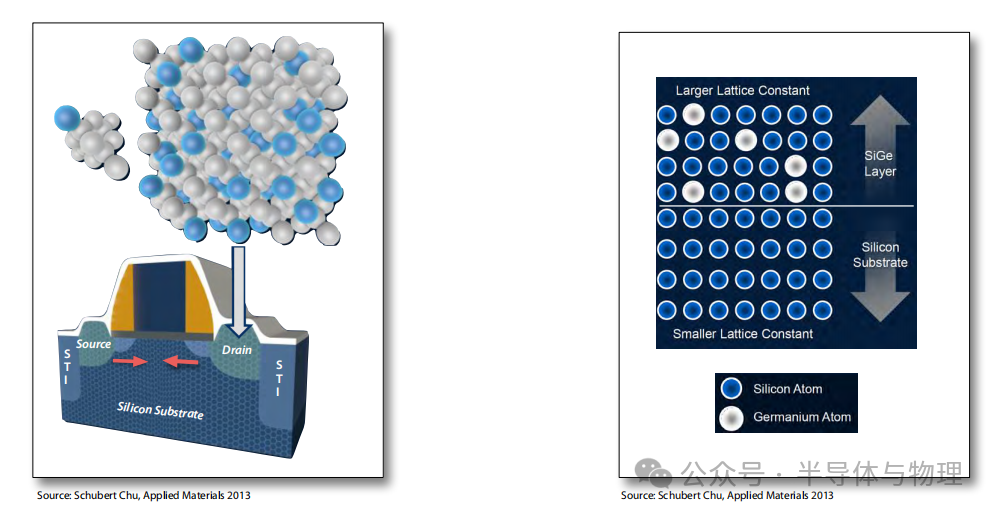

2,CMOS技術(shù)延續(xù)了P型晶圓結(jié)構(gòu)

CMOS技術(shù)出現(xiàn)后,要同時集成 NMOS 和 PMOS:

NMOS:仍建在 P型 substrate 上(與之前NMOS流程兼容)

PMOS:在 P型 substrate 上構(gòu)建 N-well 來容納PMOS

這意味著只需增加一個摻雜步驟,就能在已有的P型襯底上完成CMOS制造。

3,工藝兼容與良率控制

使用P型襯底更易控制 latch-up問題;

電子作為少子(在P型中),擴散距離短,寄生效應(yīng)易抑制;

襯底接地設(shè)計、阱隔離結(jié)構(gòu)也圍繞P型硅工藝進行優(yōu)化。

4,襯底電位固定(簡化偏置)

P型襯底直接接地(GND)即可,作為統(tǒng)一參考電位;若為N型襯底,襯底要接VDD,會因負載變化引入電位波動,造成PMOS VT偏移和噪聲問題。

-

集成電路

+關(guān)注

關(guān)注

5422文章

12025瀏覽量

368124 -

芯片制造

+關(guān)注

關(guān)注

10文章

684瀏覽量

29673

原文標題:為什么芯片制造常用P型硅?

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

硅襯底LED芯片主要制造工藝

【「大話芯片制造」閱讀體驗】+ 芯片制造過程和生產(chǎn)工藝

半導(dǎo)體制造

芯片是如何制造的?

led可控硅調(diào)光方案芯片SM7700P

N型與P型半導(dǎo)體

太陽電池的制造程序

芯片的制造流程

常用flash IC芯片廠商及型號制造商

為什么硅仍然主導(dǎo)著集成電路產(chǎn)業(yè)?

太陽能硅片中N型和P型的區(qū)別

N型和P型TOPCON區(qū)別在哪里

深入解析硅基光子芯片制造流程,揭秘科技奇跡!

為什么芯片制造常用P型硅

為什么芯片制造常用P型硅

評論