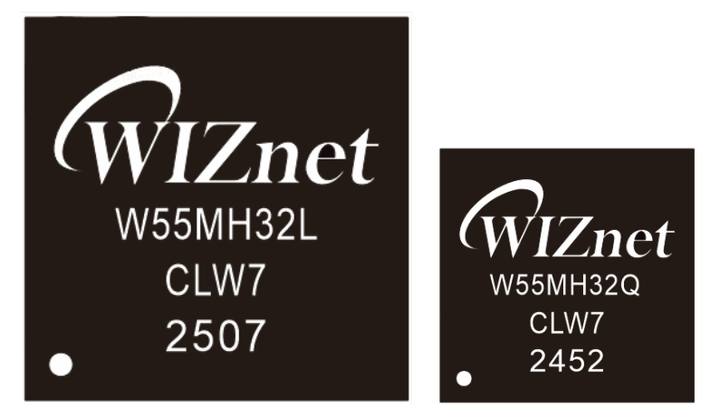

單芯片解決方案,開(kāi)啟全新體驗(yàn)——W55MH32 高性能以太網(wǎng)單片機(jī)

W55MH32是WIZnet重磅推出的高性能以太網(wǎng)單片機(jī),它為用戶帶來(lái)前所未有的集成化體驗(yàn)。這顆芯片將強(qiáng)大的組件集于一身,具體來(lái)說(shuō),一顆W55MH32內(nèi)置高性能Arm? Cortex-M3核心,其主頻最高可達(dá)216MHz;配備1024KB FLASH與96KB SRAM,滿足存儲(chǔ)與數(shù)據(jù)處理需求;集成TOE引擎,包含WIZnet全硬件TCP/IP協(xié)議棧、內(nèi)置MAC以及PHY,擁有獨(dú)立的32KB以太網(wǎng)收發(fā)緩存,可供8個(gè)獨(dú)立硬件socket使用。如此配置,真正實(shí)現(xiàn)了All-in-One解決方案,為開(kāi)發(fā)者提供極大便利。

在封裝規(guī)格上,W55MH32 提供了兩種選擇:QFN68和QFN100。

W55MH32Q采用QFN68封裝版本,尺寸為8x8mm,它擁有36個(gè)GPIO、3個(gè)ADC、12通道DMA、17個(gè)定時(shí)器、2個(gè)I2C、3個(gè)串口、2個(gè)SPI接口(其中1個(gè)帶I2S接口復(fù)用)、1個(gè)CAN以及1個(gè)USB2.0。在保持與同系列其他版本一致的核心性能基礎(chǔ)上,僅減少了部分GPIO以及SDIO接口,其他參數(shù)保持一致,性價(jià)比優(yōu)勢(shì)顯著,尤其適合網(wǎng)關(guān)模組等對(duì)空間布局要求較高的場(chǎng)景。緊湊的尺寸和精簡(jiǎn)化外設(shè)配置,使其能夠在有限空間內(nèi)實(shí)現(xiàn)高效的網(wǎng)絡(luò)連接與數(shù)據(jù)交互,成為物聯(lián)網(wǎng)網(wǎng)關(guān)、邊緣計(jì)算節(jié)點(diǎn)等緊湊型設(shè)備的理想選擇。 同系列還有QFN100封裝的W55MH32L版本,該版本擁有更豐富的外設(shè)資源,適用于需要多接口擴(kuò)展的復(fù)雜工控場(chǎng)景,軟件使用方法一致。

此外,本W(wǎng)55MH32支持硬件加密算法單元,WIZnet還推出TOE+SSL應(yīng)用,涵蓋TCP SSL、HTTP SSL以及MQTT SSL等,為網(wǎng)絡(luò)通信安全再添保障。

為助力開(kāi)發(fā)者快速上手與深入開(kāi)發(fā),基于W55MH32Q這顆芯片,WIZnet精心打造了配套開(kāi)發(fā)板。開(kāi)發(fā)板集成WIZ-Link芯片,借助一根USB C口數(shù)據(jù)線,就能輕松實(shí)現(xiàn)調(diào)試、下載以及串口打印日志等功能。開(kāi)發(fā)板將所有外設(shè)全部引出,拓展功能也大幅提升,便于開(kāi)發(fā)者全面評(píng)估芯片性能。

第十四章 ADC(上篇)

1ADC簡(jiǎn)介

12 位 ADC 是一種逐次逼近型模擬數(shù)字轉(zhuǎn)換器。它有多達(dá) 18 個(gè)通道,可測(cè)量 16 個(gè)外部和 2 個(gè)內(nèi)部信號(hào)源。各通道的 A/D 轉(zhuǎn)換可以單次、連續(xù)、掃描或間斷模式執(zhí)行。ADC 的結(jié)果可以左對(duì)齊或右對(duì)齊方式存儲(chǔ)在 16 位數(shù)據(jù)寄存器中。

模擬看門狗特性允許應(yīng)用程序檢測(cè)輸入電壓是否超出用戶定義的高/低閥值。ADC 的輸入時(shí)鐘不得超過(guò) 14MHz,它是由 PCLK2 經(jīng)分頻產(chǎn)生。

1.1 ADC主要特征

W55MH32的ADC的主要特征如下:

12 位分辨率

- ?轉(zhuǎn)換結(jié)束、注入轉(zhuǎn)換結(jié)束和發(fā)生模擬看門狗事件時(shí)產(chǎn)生中斷

- ?單次和連續(xù)轉(zhuǎn)換模式

- ?從通道 0 到通道 n 的自動(dòng)掃描模式

- ?自校準(zhǔn)

- ?帶內(nèi)嵌數(shù)據(jù)一致性的數(shù)據(jù)對(duì)齊

- ?采樣間隔可以按通道分別編程

- ?規(guī)則轉(zhuǎn)換和注入轉(zhuǎn)換均有外部觸發(fā)選項(xiàng)

- ?間斷模式

- ?雙重模式(帶 2 個(gè)或以上 ADC 的器件)

- ?ADC 轉(zhuǎn)換時(shí)間:時(shí)鐘為 56MHz 時(shí)為 1μs(時(shí)鐘為 72MHz 為 1.17μs)

- ?ADC 供電要求:2.4V 到 3.6V

- ?ADC 輸入范圍:VREF-≤VIN≤VREF+

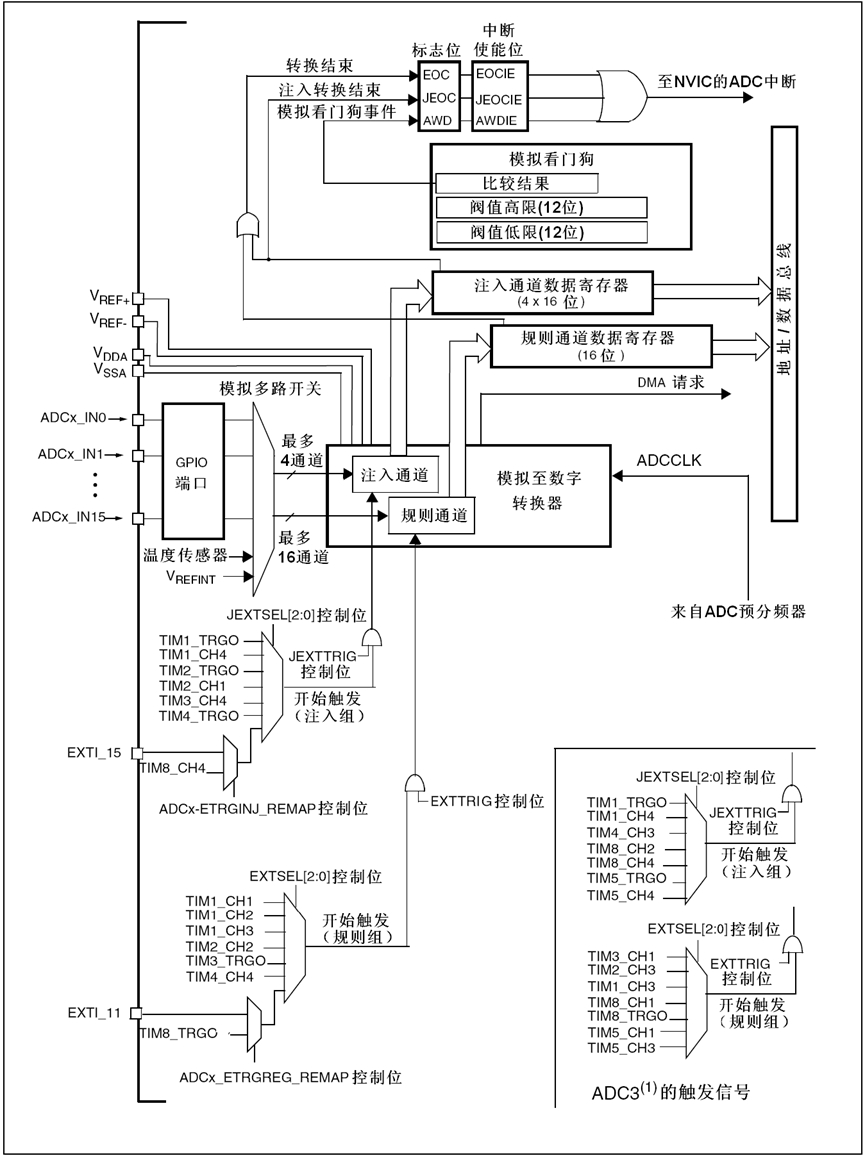

- ?規(guī)則通道轉(zhuǎn)換期間有 DMA 請(qǐng)求產(chǎn)生。下圖是 ADC 模塊的方框圖。

注意: 如果有 VREF-引腳,必須和 VSSA 相連接

1.2 ADC功能描述

ADC功能框圖如下:

單個(gè) ADC 框圖

1.ADC3 的規(guī)則轉(zhuǎn)換和注入轉(zhuǎn)換觸發(fā)與 ADC1 和 ADC2 的不同。

| 名稱 | 信號(hào)類型 | 注解 |

| VREF+ | 輸入,模擬參考正極 | ADC 使用的高端 / 正極參考電壓,2.4V ≤ VREF+ ≤ VDDA |

| VDDA(*) | 輸入,模擬電源 | 等效于 VDO 的模擬電源:2.4V ≤ VDDA ≤ VDD (3.6V) |

| VREF- | 輸入,模擬參考負(fù)極 | ADC 使用的低端 / 負(fù)極參考電壓,VREF- ≈ VSSA |

| VSSA(*) | 輸入,模擬電源地 | 等效于 VSS 的模擬電源地 |

| ADC_IN[15:0] | 模擬輸入 | 16 個(gè) ADC 模擬通道 |

1.VDDA 和 VSSA 應(yīng)該分別連接到 VDD 和 VSS。

1.3 ADC開(kāi)關(guān)控制

通過(guò)設(shè)置 ADC_CR2 寄存器的 ADON 位可給 ADC 上電。當(dāng)?shù)谝淮卧O(shè)置 ADON 位時(shí),它將 ADC 從斷電狀態(tài)下喚醒。ADC 上電延遲一段時(shí)間后(tSTAB),再次設(shè)置 ADON 位時(shí)開(kāi)始進(jìn)行轉(zhuǎn)換。

通過(guò)清除 ADON 位可以停止轉(zhuǎn)換,并將 ADC 置于斷電模式。在這個(gè)模式中,ADC 幾乎不耗電(僅幾個(gè)μA)。

1.4 ADC時(shí)鐘

由時(shí)鐘控制器提供的 ADCCLK 時(shí)鐘和 PCLK2(APB2 時(shí)鐘)同步。RCC 控制器為 ADC 時(shí)鐘提供一個(gè)專用的可編程預(yù)分頻器,詳見(jiàn)第 6 節(jié)-復(fù)位和時(shí)鐘控制(RCC)。

2 模式選擇

2.1 通道選擇

有 16 個(gè)多路通道。可以把轉(zhuǎn)換組織成兩組:規(guī)則組和注入組。在任意多個(gè)通道上以任意順序進(jìn)行的一系列轉(zhuǎn)換構(gòu)成成組轉(zhuǎn)換。例如,可以如下順序完成轉(zhuǎn)換:通道 3、通道 8、通道 2、通道 2、通道 0、通道 2、通道 2、通道 15。

規(guī)則組由多達(dá) 16 個(gè)轉(zhuǎn)換組成。規(guī)則通道和它們的轉(zhuǎn)換順序在 ADC_SQRx 寄存器中選擇。規(guī)則組中轉(zhuǎn)換的總數(shù)應(yīng)寫入 ADC_SQR1 寄存器的 L[3:0]位中。

注入組由多達(dá) 4 個(gè)轉(zhuǎn)換組成。注入通道和它們的轉(zhuǎn)換順序在 ADC_JSQR 寄存器中選擇。注入組里的轉(zhuǎn)換總數(shù)目應(yīng)寫入 ADC_JSQR 寄存器的 L[1:0]位中。

如果 ADC_SQRx 或 ADC_JSQR 寄存器在轉(zhuǎn)換期間被更改,當(dāng)前的轉(zhuǎn)換被清除,一個(gè)新的啟動(dòng)脈沖將發(fā)送到 ADC 以轉(zhuǎn)換新選擇的組。

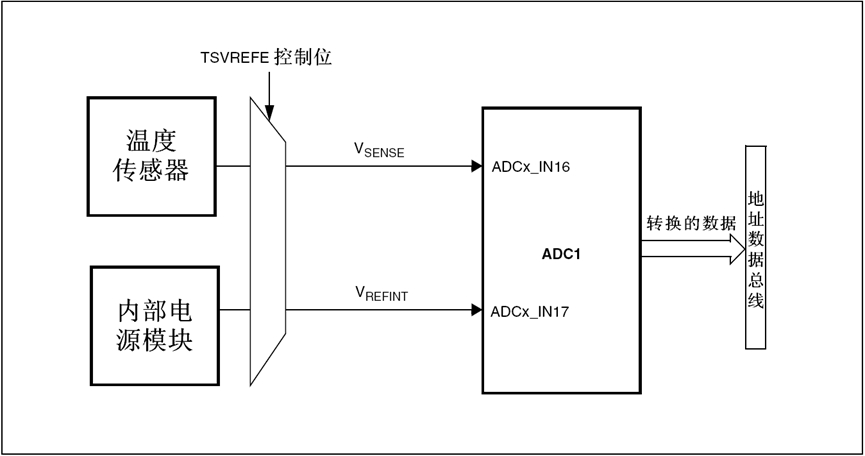

溫度傳感器/VREFINT 內(nèi)部通道

溫度傳感器和通道 ADC1_IN16 相連接,內(nèi)部參照電壓 VREFINT 和 ADC1_IN17 相連接。可以按注入或規(guī)則通道對(duì)這兩個(gè)內(nèi)部通道進(jìn)行轉(zhuǎn)換。

注意:溫度傳感器和 VREFINT 只能出現(xiàn)在主 ADC1 中。

2.2 單次轉(zhuǎn)換模式

單次轉(zhuǎn)換模式下,ADC 只執(zhí)行一次轉(zhuǎn)換。該模式既可通過(guò)設(shè)置 ADC_CR2 寄存器的 ADON 位(只適用于規(guī)則通道)啟動(dòng)也可通過(guò)外部觸發(fā)啟動(dòng)(適用于規(guī)則通道或注入通道),這時(shí) CONT 位為 0。一旦選擇通道的轉(zhuǎn)換完成:

如果一個(gè)規(guī)則通道被轉(zhuǎn)換:轉(zhuǎn)換數(shù)據(jù)被儲(chǔ)存在 16 位 ADC_DR 寄存器中EOC(轉(zhuǎn)換結(jié)束)標(biāo)志被設(shè)置如果設(shè)置了 EOCIE,則產(chǎn)生中斷。

如果一個(gè)注入通道被轉(zhuǎn)換:轉(zhuǎn)換數(shù)據(jù)被儲(chǔ)存在 16 位的 ADC_DRJ1 寄存器中JEOC(注入轉(zhuǎn)換結(jié)束)標(biāo)志被設(shè)置如果設(shè)置了 JEOCIE 位,則產(chǎn)生中斷。然后 ADC 停止。

2.3 連續(xù)轉(zhuǎn)換模式

在連續(xù)轉(zhuǎn)換模式中,當(dāng)前面 ADC 轉(zhuǎn)換一結(jié)束馬上就啟動(dòng)另一次轉(zhuǎn)換。此模式可通過(guò)外部觸發(fā)啟動(dòng)或通過(guò)設(shè)置 ADC_CR2 寄存器上的 ADON 位啟動(dòng),此時(shí) CONT 位是 1。

每個(gè)轉(zhuǎn)換后:如果一個(gè)規(guī)則通道被轉(zhuǎn)換:轉(zhuǎn)換數(shù)據(jù)被儲(chǔ)存在 16 位的 ADC_DR 寄存器中EOC(轉(zhuǎn)換結(jié)束)標(biāo)志被設(shè)置如果設(shè)置了 EOCIE,則產(chǎn)生中斷。

如果設(shè)置了 JEOCIE 位,則產(chǎn)生中斷。

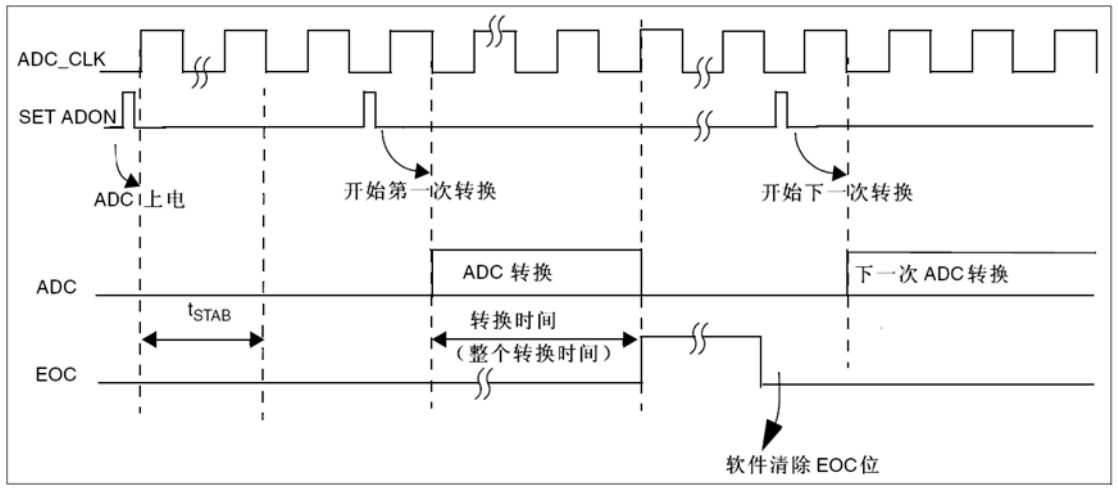

2.4 時(shí)序圖

如下圖所示,ADC 在開(kāi)始精確轉(zhuǎn)換前需要一個(gè)穩(wěn)定時(shí)間 tSTAB。在開(kāi)始 ADC 轉(zhuǎn)換和 14 個(gè)時(shí)鐘周期后,EOC 標(biāo)志被設(shè)置,16 位 ADC 數(shù)據(jù)寄存器包含轉(zhuǎn)換的結(jié)果。

時(shí)序圖

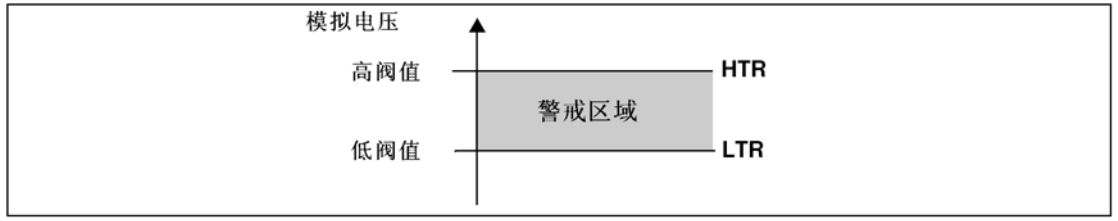

2.5 模擬看門狗

如果被 ADC 轉(zhuǎn)換的模擬電壓低于低閥值或高于高閥值,AWD 模擬看門狗狀態(tài)位被設(shè)置。閥值位于ADC_HTR 和 ADC_LTR 寄存器的最低 12 個(gè)有效位中。通過(guò)設(shè)置 ADC_CR1 寄存器的 AWDIE 位以允許產(chǎn)生相應(yīng)中斷。

閥值獨(dú)立于由 ADC_CR2 寄存器上的 ALIGN 位選擇的數(shù)據(jù)對(duì)齊模式。通過(guò)配置 ADC_CR1 寄存器,模擬看門狗可以作用于 1 個(gè)或多個(gè)通道。

模擬看門狗警戒區(qū)

模擬看門狗通道選擇

| 模擬看門狗警戒的通道 | ADC_CR1 寄存器控制位 | ||

| AWDSGL 位 | AWDEN 位 | JAWDEN 位 | |

| 無(wú) | 任意值 | 0 | 0 |

| 所有注入通道 | 0 | 0 | 1 |

| 所有規(guī)則通道 | 0 | 1 | 0 |

| 所有注入和規(guī)則通道 | 0 | 1 | 1 |

| 單一的 (1) 注入通道 | 1 | 0 | 1 |

| 單一的 (1) 規(guī)則通道 | 1 | 1 | 0 |

| 單一的 (1) 注入或規(guī)則通道 | 1 | 1 | 1 |

2.6 掃描模式

此模式用來(lái)掃描一組模擬通道。

掃描模式可通過(guò)設(shè)置 ADC_CR1 寄存器的 SCAN 位來(lái)選擇。一旦這個(gè)位被設(shè)置,ADC 掃描所有被ADC_SQRX 寄存器(對(duì)規(guī)則通道)或 ADC_JSQR(對(duì)注入通道)選中的所有通道。在每個(gè)組的每個(gè)通道上執(zhí)行單次轉(zhuǎn)換。在每個(gè)轉(zhuǎn)換結(jié)束時(shí),同一組的下一個(gè)通道被自動(dòng)轉(zhuǎn)換。如果設(shè)置了 CONT 位,轉(zhuǎn)換不會(huì)在選擇組的最后一個(gè)通道上停止,而是再次從選擇組的第一個(gè)通道繼續(xù)轉(zhuǎn)換。

如果設(shè)置了 DMA 位,在每次 EOC 后,DMA 控制器把規(guī)則組通道的轉(zhuǎn)換數(shù)據(jù)傳輸?shù)?SRAM 中。而注入通道轉(zhuǎn)換的數(shù)據(jù)總是存儲(chǔ)在 ADC_JDRx 寄存器中。

2.7 注入通道管理

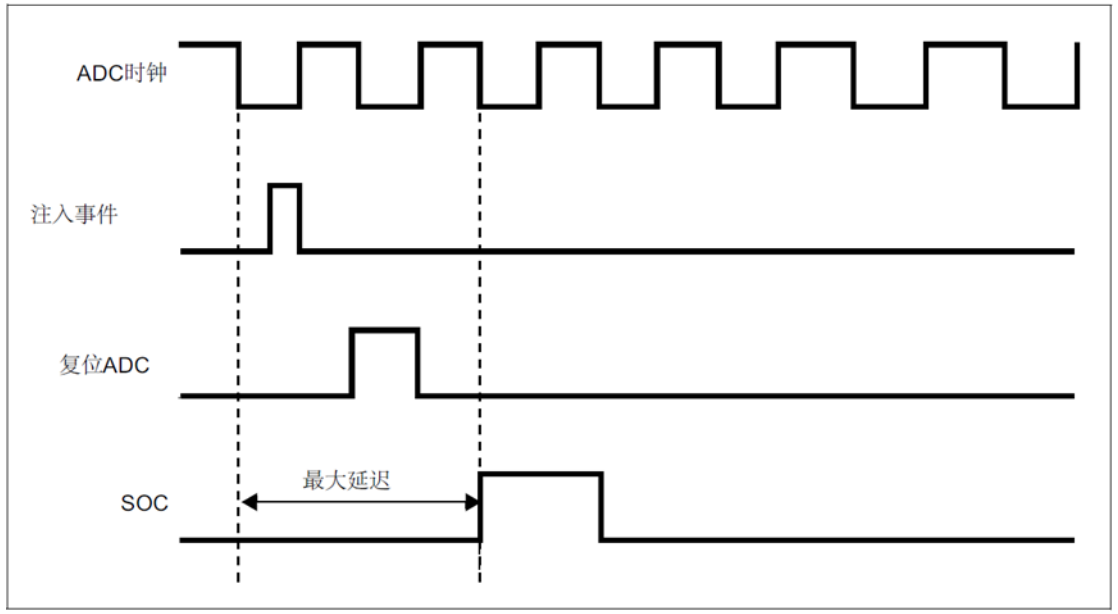

觸發(fā)注入

清除 ADC_CR1 寄存器的 JAUTO 位,并且設(shè)置 SCAN 位,即可使用觸發(fā)注入功能。

1. 利用外部觸發(fā)或通過(guò)設(shè)置 ADC_CR2 寄存器的 ADON 位,啟動(dòng)一組規(guī)則通道的轉(zhuǎn)換。

2. 如果在規(guī)則通道轉(zhuǎn)換期間產(chǎn)生一外部注入觸發(fā),當(dāng)前轉(zhuǎn)換被復(fù)位,注入通道序列被以單次掃描方式進(jìn)行轉(zhuǎn)換。

3. 然后,恢復(fù)上次被中斷的規(guī)則組通道轉(zhuǎn)換。如果在注入轉(zhuǎn)換期間產(chǎn)生一規(guī)則事件,注入轉(zhuǎn)換不會(huì)被中斷,但是規(guī)則序列將在注入序列結(jié)束后被執(zhí)行。

注: 當(dāng)使用觸發(fā)的注入轉(zhuǎn)換時(shí),必須保證觸發(fā)事件的間隔長(zhǎng)于注入序列。例如:序列長(zhǎng)度為 28 個(gè)ADC 時(shí)鐘周期(即 2 個(gè)具有 1.5 個(gè)時(shí)鐘間隔采樣時(shí)間的轉(zhuǎn)換),觸發(fā)之間最小的間隔必須是 29 個(gè)ADC 時(shí)鐘周期。

自動(dòng)注入

如果設(shè)置了 JAUTO 位,在規(guī)則組通道之后,注入組通道被自動(dòng)轉(zhuǎn)換。這可以用來(lái)轉(zhuǎn)換在ADC_SQRx 和 ADC_JSQR 寄存器中設(shè)置的多至 20 個(gè)轉(zhuǎn)換序列。

在此模式里,必須禁止注入通道的外部觸發(fā)。

如果除 JAUTO 位外還設(shè)置了 CONT 位,規(guī)則通道至注入通道的轉(zhuǎn)換序列被連續(xù)執(zhí)行。對(duì)于 ADC 時(shí)鐘預(yù)分頻系數(shù)為 4 至 8 時(shí),當(dāng)從規(guī)則轉(zhuǎn)換切換到注入序列或從注入轉(zhuǎn)換切換到規(guī)則序列時(shí),會(huì)自動(dòng)插入 1 個(gè) ADC 時(shí)鐘間隔;當(dāng) ADC 時(shí)鐘預(yù)分頻系數(shù)為 2 時(shí),則有 2 個(gè) ADC 時(shí)鐘間隔的延遲。

注意: 不可能同時(shí)使用自動(dòng)注入和間斷模式。

注入轉(zhuǎn)換延時(shí)

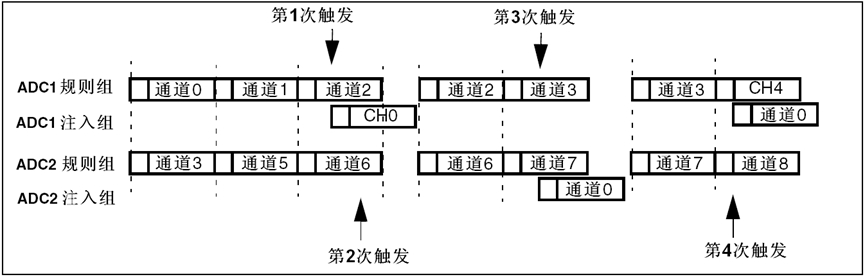

2.8 間斷模式

規(guī)則組

此模式通過(guò)設(shè)置 ADC_CR1 寄存器上的 DISCEN 位激活。它可以用來(lái)執(zhí)行一個(gè)短序列的 n 次轉(zhuǎn)換(n<=8),此轉(zhuǎn)換是 ADC_SQRx 寄存器所選擇的轉(zhuǎn)換序列的一部分。數(shù)值 n 由 ADC_CR1 寄存器的DISCNUM[2:0]位給出。

一個(gè)外部觸發(fā)信號(hào)可以啟動(dòng) ADC_SQRx 寄存器中描述的下一輪 n 次轉(zhuǎn)換,直到此序列所有的轉(zhuǎn)換完成為止。總的序列長(zhǎng)度由 ADC_SQR1 寄存器的 L[3:0]定義。

舉例:

n=3,被轉(zhuǎn)換的通道=0、1、2、3、6、7、9、10

第一次觸發(fā):轉(zhuǎn)換的序列為 0、1、2

第二次觸發(fā):轉(zhuǎn)換的序列為 3、6、7

第三次觸發(fā):轉(zhuǎn)換的序列為 9、10,并產(chǎn)生 EOC 事件

第四次觸發(fā):轉(zhuǎn)換的序列 0、1、2

注意: 當(dāng)以間斷模式轉(zhuǎn)換一個(gè)規(guī)則組時(shí),轉(zhuǎn)換序列結(jié)束后不自動(dòng)從頭開(kāi)始。當(dāng)所有子組被轉(zhuǎn)換完成,下一次觸發(fā)啟動(dòng)第一個(gè)子組的轉(zhuǎn)換。在上面的例子中,第四次觸發(fā)重新轉(zhuǎn)換第一子組的通道 0、1 和 2。

注入組

此模式通過(guò)設(shè)置 ADC_CR1 寄存器的 JDISCEN 位激活。在一個(gè)外部觸發(fā)事件后,該模式按通道順序逐個(gè)轉(zhuǎn)換 ADC_JSQR 寄存器中選擇的序列。一個(gè)外部觸發(fā)信號(hào)可以啟動(dòng) ADC_JSQR 寄存器選擇的下一個(gè)通道序列的轉(zhuǎn)換,直到序列中所有的轉(zhuǎn)換完成為止。總的序列長(zhǎng)度由 ADC_JSQR 寄存器的 JL[1:0]位定義。

舉例:

n=1,被轉(zhuǎn)換的通道=1、2、3

第一次觸發(fā):通道 1 被轉(zhuǎn)換

第二次觸發(fā):通道 2 被轉(zhuǎn)換

第三次觸發(fā):通道 3 被轉(zhuǎn)換,并且產(chǎn)生 EOC 和 JEOC 事件

第四次觸發(fā):通道 1 被轉(zhuǎn)換

注意: 1.當(dāng)完成所有注入通道轉(zhuǎn)換,下個(gè)觸發(fā)啟動(dòng)第 1 個(gè)注入通道的轉(zhuǎn)換。在上述例子中,第四個(gè)觸發(fā)重新轉(zhuǎn)換第 1 個(gè)注入通道 1。

2.不能同時(shí)使用自動(dòng)注入和間斷模式。

3.必須避免同時(shí)為規(guī)則和注入組設(shè)置間斷模式。間斷模式只能作用于一組轉(zhuǎn)換。

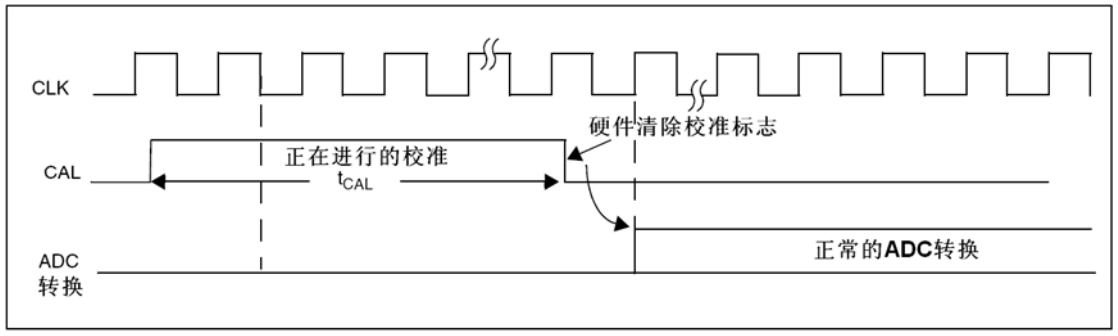

3 校準(zhǔn)

ADC 有一個(gè)內(nèi)置自校準(zhǔn)模式。校準(zhǔn)可大幅減小因內(nèi)部電容器組的變化而造成的準(zhǔn)精度誤差。在校準(zhǔn)期間,在每個(gè)電容器上都會(huì)計(jì)算出一個(gè)誤差修正碼(數(shù)字值),這個(gè)碼用于消除在隨后的轉(zhuǎn)換中每個(gè)電容器上產(chǎn)生的誤差。

通過(guò)設(shè)置 ADC_CR2 寄存器的 CAL 位啟動(dòng)校準(zhǔn)。一旦校準(zhǔn)結(jié)束,CAL 位被硬件復(fù)位,可以開(kāi)始正常轉(zhuǎn)換。建議在上電時(shí)執(zhí)行一次 ADC 校準(zhǔn)。校準(zhǔn)階段結(jié)束后,校準(zhǔn)碼儲(chǔ)存在 ADC_DR 中。

注意:1.建議在每次上電后執(zhí)行一次校準(zhǔn)。

2.啟動(dòng)校準(zhǔn)前,ADC 必須處于關(guān)電狀態(tài)(ADON='0')超過(guò)至少兩個(gè) ADC 時(shí)鐘周期。

校準(zhǔn)時(shí)序圖

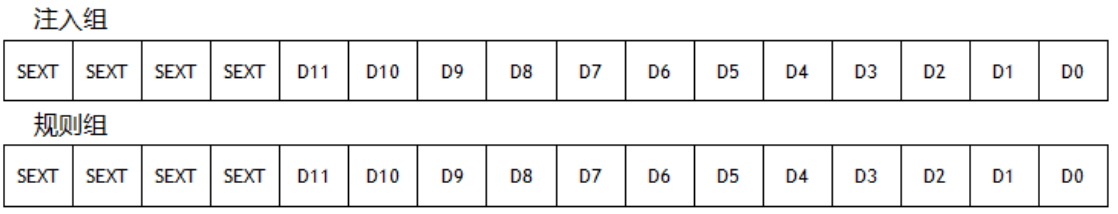

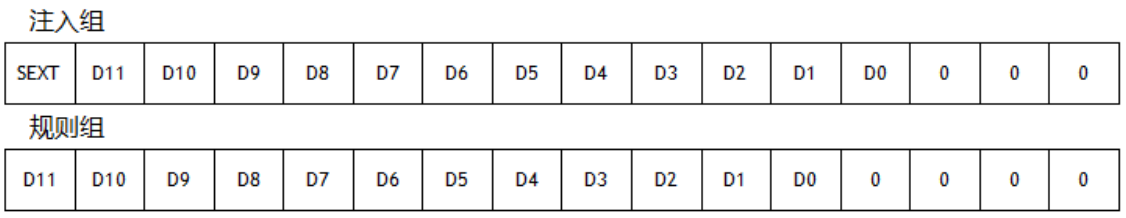

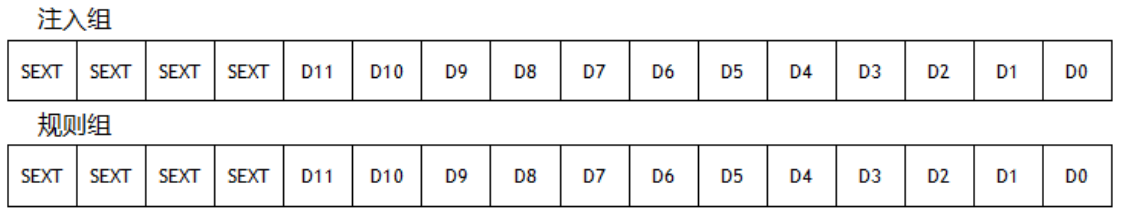

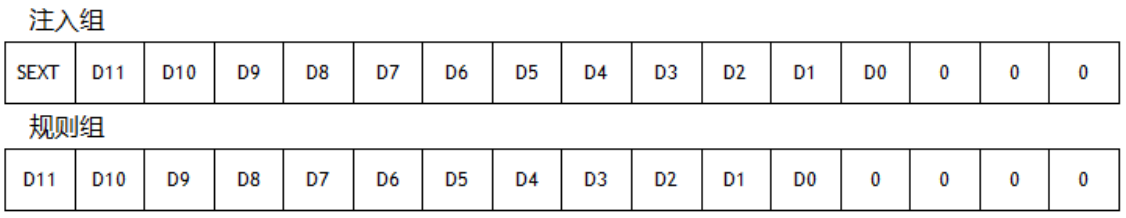

3.1 數(shù)據(jù)對(duì)齊

ADC_CR2 寄存器中的 ALIGN 位選擇轉(zhuǎn)換后數(shù)據(jù)儲(chǔ)存的對(duì)齊方式。數(shù)據(jù)可以左對(duì)齊或右對(duì)齊,如

注入組通道轉(zhuǎn)換的數(shù)據(jù)值已經(jīng)減去了在 ADC_JOFRx 寄存器中定義的偏移量,因此結(jié)果可以是一個(gè)負(fù)值。SEXT 位是擴(kuò)展的符號(hào)值。

對(duì)于規(guī)則組通道,不需減去偏移值,因此只有 12 個(gè)位有效。

數(shù)據(jù)右對(duì)齊

數(shù)據(jù)左對(duì)齊

3.2 可編程的通道采樣時(shí)間

ADC 使用若干個(gè) ADC_CLK 周期對(duì)輸入電壓采樣,采樣周期數(shù)目可以通過(guò) ADC_SMPR1 和ADC_SMPR2 寄存器SMP[2:0]位更改。每個(gè)通道可以分別用不同的時(shí)間采樣。

總轉(zhuǎn)換時(shí)間如下計(jì)算:

TCONV=采樣時(shí)間+12.5 個(gè)周期

例如:

當(dāng) ADCCLK=14MHz,采樣時(shí)間為 1.5 周期

TCONV=1.5+12.5=14 周期=1μs

3.3 外部觸發(fā)轉(zhuǎn)換

轉(zhuǎn)換可以由外部事件觸發(fā)(例如定時(shí)器捕獲,EXTI 線)。如果設(shè)置了 EXTTRIG 控制位,則外部事件就能夠觸發(fā)轉(zhuǎn)換。EXTSEL[2:0]和 JEXTSEL2:0]控制位允許應(yīng)用程序選擇 8 個(gè)可能的事件中的某一個(gè),可以觸發(fā)規(guī)則和注入組的采樣。

注意: 當(dāng)外部觸發(fā)信號(hào)被選為 ADC 規(guī)則或注入轉(zhuǎn)換時(shí),只有它的上升沿可以啟動(dòng)轉(zhuǎn)換。

表 ADC1 和 ADC2 用于規(guī)則通道的外部觸發(fā)

| 觸發(fā)源 | 類型 | EXTSSEL[2:0] |

| TIM1_CC1 事件 | 來(lái)自片上定時(shí)器的內(nèi)部信號(hào) | 000 |

| TIM1_CC2 事件 | 001 | |

| TIM1_CC3 事件 | 010 | |

| TIM2_CC2 事件 | 011 | |

| TIM3_TRGO 事件 | 100 | |

| TIM4_CC4 事件 | 101 | |

| EXTI 線 11/TIM8_TRGO事件(1) | 外部引腳/來(lái)自片上定時(shí)器的內(nèi)部信號(hào) | 110 |

| SWSTART | 軟件控制位 | 111 |

(1)對(duì)于規(guī)則通道,選中 EXTI 線路 11 或 TIM8_TRGO 作為外部觸發(fā)事件,可以分別通過(guò)設(shè)置 ADC1和 ADC2 的 ADC1_ETRGREG_REMAP 位和 ADC2_ETRGREG_REMAP 位實(shí)現(xiàn)。

表 ADC1 和 ADC2 用于注入通道的外部觸發(fā)

| 觸發(fā)源 | 連接類型 | JEXTSE[2:0] |

| TIM1_TRGO 事件 | 來(lái)自片上定時(shí)器的內(nèi)部信號(hào) | 000 |

| TIM1_CC4 事件 | 001 | |

| TIM2_TRGO 事件 | 010 | |

| TIM2_CC1 事件 | 011 | |

| TIM3_CC4 事件 | 100 | |

| TIM4_TRGO 事件 | 101 | |

| EXTI 線 15/TIM8_CC4 事件(1) | 外部引腳 / 來(lái)自片上定時(shí)器的內(nèi)部信號(hào) | 110 |

| SWSTART | 軟件控制位 | 111 |

(2)為注入信道選擇外部觸發(fā)器 EXTIline15 或 TIM8-CC4 事件是通過(guò)分別為 ADC1 和 ADC2 配置ADC1ETRGINJREMAP 和 ADC2 ETRGINJ·REMAP 來(lái)完成的。

表 ADC3 用于規(guī)則通道的外部觸發(fā)

| 觸發(fā)源 | 連接類型 | EXTSSEL[2:0] |

| TIM3_CC1 事件 | 來(lái)自片上定時(shí)器的內(nèi)部信號(hào) | 000 |

| TIM2_CC3 事件 | 001 | |

| TIM1_CC3 事件 | 010 | |

| TIM8_CC1 事件 | 011 | |

| TIM8_TRGO 事件 | 100 | |

| TIM5_CC1 事件 | 101 | |

| TIM5_CC3 事件 | 110 | |

| SWSTART | 軟件控制位 | 111 |

表 ADC3 用于注入通道的外部觸發(fā)

| 觸發(fā)源 | 連接類型 | JEXTSE[2:0] |

| TIM1_TRGO 事件 | 來(lái)自片上定時(shí)器的內(nèi)部信號(hào) | 000 |

| TIM1_CC4 事件 | 001 | |

| TIM4_CC3 事件 | 010 | |

| TIM8_CC2 事件 | 011 | |

| TIM8_CC4 事件 | 100 | |

| TIM5_TRGO 事件 | 101 | |

| TIM5_CC4 事件 | 110 | |

| JSWSTART | 軟件控制位 | 111 |

軟件觸發(fā)事件可以通過(guò)對(duì)寄存器 ADC_CR2 的 SWSTART 或 JSWSTART 位置'1'產(chǎn)生。規(guī)則組的轉(zhuǎn)換可以被注入觸發(fā)打斷。

3.4 DMA請(qǐng)求

因?yàn)橐?guī)則通道轉(zhuǎn)換的值儲(chǔ)存在一個(gè)僅有的數(shù)據(jù)寄存器中,所以當(dāng)轉(zhuǎn)換多個(gè)規(guī)則通道時(shí)需要使用DMA,這可以避免丟失已經(jīng)存儲(chǔ)在 ADC_DR 寄存器中的數(shù)據(jù)。只有在規(guī)則通道的轉(zhuǎn)換結(jié)束時(shí)才產(chǎn)生 DMA 請(qǐng)求,并將轉(zhuǎn)換的數(shù)據(jù)從 ADC_DR 寄存器傳輸?shù)接脩糁付ǖ哪康牡刂贰?/p>

注: 只有 ADC1 和 ADC3 擁有 DMA 功能。由 ADC2 轉(zhuǎn)化的數(shù)據(jù)可以通過(guò)雙 ADC 模式,利用 ADC1 的DMA 功能傳輸。

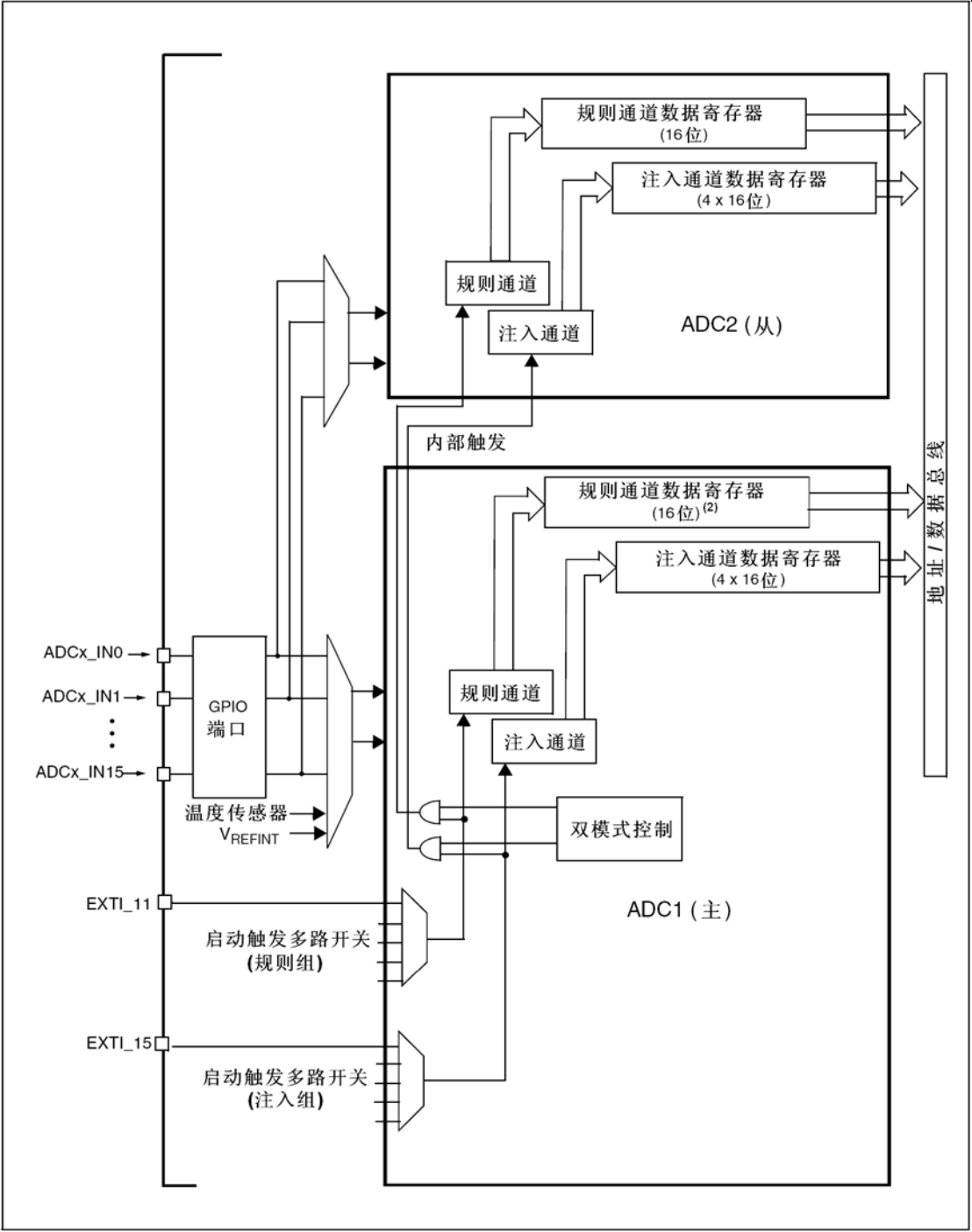

4 雙ADC模式

在有 2 個(gè)或以上 ADC 模塊的產(chǎn)品中,可以使用雙 ADC 模式。在雙 ADC 模式里,根據(jù) ADC1_CR1 寄存器中 DUALMOD[2:0]位所選的模式,轉(zhuǎn)換的啟動(dòng)可以是ADC1 主和 ADC2 從的交替觸發(fā)或同步觸發(fā)。

注意: 在雙 ADC 模式里,當(dāng)轉(zhuǎn)換配置成由外部事件觸發(fā)時(shí),用戶必須將其設(shè)置成僅觸發(fā)主 ADC,從 ADC設(shè)置成軟件觸發(fā),這樣可以防止意外的觸發(fā)從轉(zhuǎn)換。但是,主和從 ADC 的外部觸發(fā)必須同時(shí)被激活。

共有 6 種可能的模式:

- ?同步注入模式

- ?同步規(guī)則模式

- ?快速交叉模式

- ?慢速交叉模式

- ?交替觸發(fā)模式

- ?獨(dú)立模式

還有可以用下列方式組合使用上面的模式:

- ?同步注入模式+同步規(guī)則模式

- ?同步規(guī)則模式+交替觸發(fā)模式

- ?同步注入模式+交叉模式

注意: 在雙 ADC 模式里,為了在主數(shù)據(jù)寄存器上讀取從轉(zhuǎn)換數(shù)據(jù),必須使能 DMA 位,即使不使用 DMA傳輸規(guī)則通道數(shù)據(jù)。

雙 ADC 框圖

1.外部觸發(fā)信號(hào)作用于 ADC2,但在本圖中沒(méi)有顯示。

2.在某些雙 ADC 模式中,在完整的 ADC1 數(shù)據(jù)寄存器(ADC1_DR)中包含了 ADC1 和 ADC2 的規(guī)則轉(zhuǎn)換數(shù)據(jù)。

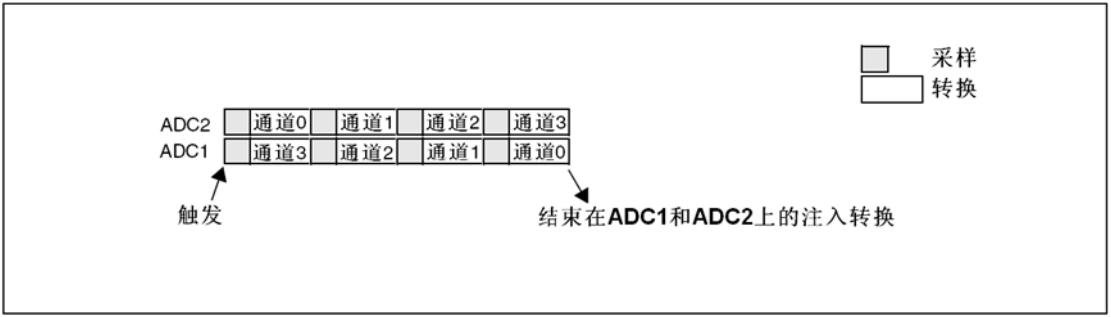

4.1 同步注入模式

此模式轉(zhuǎn)換一個(gè)注入通道組。外部觸發(fā)來(lái)自 ADC1 的注入組多路開(kāi)關(guān)(由 ADC1_CR2 寄存器的JEXTSEL[2:0]選擇),它同時(shí)給 ADC2 提供同步觸發(fā)。

注意: 不要在 2 個(gè) ADC 上轉(zhuǎn)換相同的通道(兩個(gè) ADC 在同一個(gè)通道上的采樣時(shí)間不能重疊)。在 ADC1 或 ADC2 的轉(zhuǎn)換結(jié)束時(shí):

轉(zhuǎn)換的數(shù)據(jù)存儲(chǔ)在每個(gè) ADC 接口的 ADC_JDRx 寄存器中。

當(dāng)所有 ADC1/ADC2 注入通道都被轉(zhuǎn)換時(shí),產(chǎn)生 JEOC 中斷(若任一 ADC 接口開(kāi)放了中斷)。

注: 在同步模式中,必須轉(zhuǎn)換具有相同時(shí)間長(zhǎng)度的序列,或保證觸發(fā)的間隔比 2 個(gè)序列中較長(zhǎng)的序列長(zhǎng),否則當(dāng)較長(zhǎng)序列的轉(zhuǎn)換還未完成時(shí),具有較短序列的 ADC 轉(zhuǎn)換可能會(huì)被重啟。

在 4 個(gè)通道上的同步注入模式

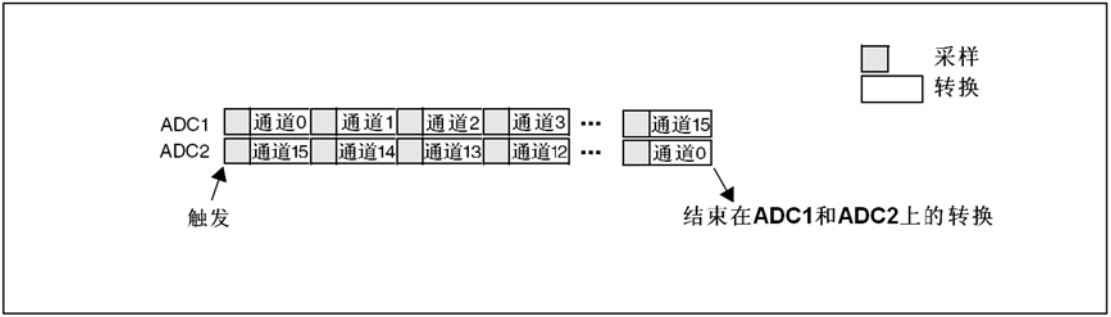

4.2 同步規(guī)則模式

此模式在規(guī)則通道組上執(zhí)行。外部觸發(fā)來(lái)自 ADC1 的規(guī)則組多路開(kāi)關(guān)(由 ADC1_CR2 寄存器的EXTSEL[2:0]選擇),它同時(shí)給 ADC2 提供同步觸發(fā)。

注意: 不要在 2 個(gè) ADC 上轉(zhuǎn)換相同的通道((兩個(gè) ADC 在同一個(gè)通道上的采樣時(shí)間不能重疊)。在 ADC1 或 ADC2 的轉(zhuǎn)換結(jié)束時(shí):

產(chǎn)生一個(gè) 32 位 DMA 傳輸請(qǐng)求(如果設(shè)置了 DMA 位),32 位的 ADC1_DR 寄存器內(nèi)容傳輸?shù)絊RAM 中,它上半個(gè)字包含 ADC2 的轉(zhuǎn)換數(shù)據(jù),低半個(gè)字包含 ADC1 的轉(zhuǎn)換數(shù)據(jù)。

當(dāng)所有 ADC1/ADC2 規(guī)則通道都被轉(zhuǎn)換完時(shí),產(chǎn)生 EOC 中斷(若任一 ADC 接口開(kāi)放了中斷)。

注: 在同步規(guī)則模式中,必須轉(zhuǎn)換具有相同時(shí)間長(zhǎng)度的序列,或保證觸發(fā)的間隔比 2 個(gè)序列中較長(zhǎng)的序列長(zhǎng),否則當(dāng)較長(zhǎng)序列的轉(zhuǎn)換還未完成時(shí),具有較短序列的 ADC 轉(zhuǎn)換可能會(huì)被重啟。

在 16 個(gè)通道上的同步規(guī)則模式

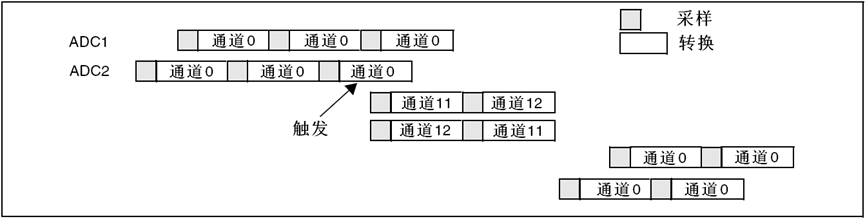

4.3 快速交叉模式

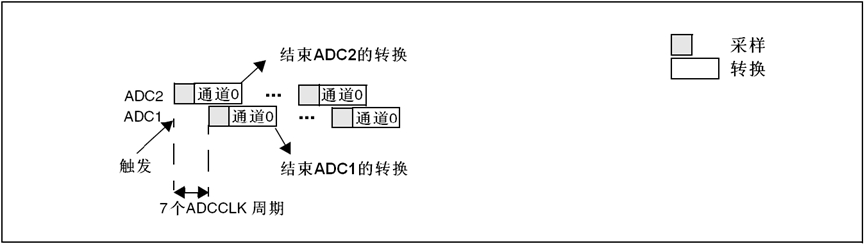

此模式只適用于規(guī)則通道組(通常為一個(gè)通道)。外部觸發(fā)來(lái)自 ADC1 的規(guī)則通道多路開(kāi)關(guān)。外部觸發(fā)產(chǎn)生后:

ADC2 立即啟動(dòng)并且ADC1 在延遲 7 個(gè) ADC 時(shí)鐘周期后啟動(dòng)如果同時(shí)設(shè)置了 ADC1 和 ADC2 的 CONT 位,所選的兩個(gè) ADC 規(guī)則通道將被連續(xù)地轉(zhuǎn)換。ADC1產(chǎn)生一個(gè)EOC中斷后(由EOCIE使能),產(chǎn)生一個(gè)32位的DMA傳輸請(qǐng)求(如果設(shè)置了DMA位),ADC1_DR 寄存器的 32 位數(shù)據(jù)被傳輸?shù)?SRAM,ADC1_DR 的上半個(gè)字包含 ADC2 的轉(zhuǎn)換數(shù)據(jù),低半個(gè)字包含 ADC1 的轉(zhuǎn)換數(shù)據(jù)。

注意: 最大允許采樣時(shí)間<7 個(gè) ADCCLK 周期,避免 ADC1 和 ADC2 轉(zhuǎn)換相同通道時(shí)發(fā)生兩個(gè)采樣周期的重疊。

在 1 個(gè)通道上連續(xù)轉(zhuǎn)換模式下的快速交叉模式

4.4 慢速交叉模式

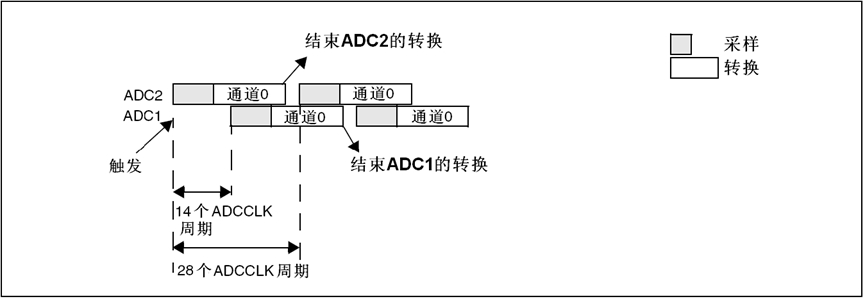

此模式只適用于規(guī)則通道組(只能為一個(gè)通道)。外部觸發(fā)來(lái)自 ADC1 的規(guī)則通道多路開(kāi)關(guān)。外部觸發(fā)產(chǎn)生后:

ADC2 立即啟動(dòng)并且 ADC1 在延遲 14 個(gè) ADC 時(shí)鐘周期后啟動(dòng)在延遲第二次 14 個(gè) ADC 周期后 ADC2 再次啟動(dòng),如此循環(huán)。

注意: 最大允許采樣時(shí)間<14 個(gè) ADCCLK 周期,以避免和下個(gè)轉(zhuǎn)換重疊。ADC1產(chǎn)生一個(gè)EOC中斷后(由EOCIE使能),產(chǎn)生一個(gè)32位的DMA傳輸請(qǐng)求(如果設(shè)置了DMA位),ADC1_DR 寄存器的 32 位數(shù)據(jù)被傳輸?shù)?SRAM,ADC1_DR 的上半個(gè)字包含 ADC2 的轉(zhuǎn)換數(shù)據(jù),低半個(gè)字包含 ADC1 的轉(zhuǎn)換數(shù)據(jù)。在 28 個(gè) ADC 時(shí)鐘周期后自動(dòng)啟動(dòng)新的 ADC2 轉(zhuǎn)換。在這個(gè)模式下不能設(shè)置 CONT 位,因?yàn)樗鼘⑦B續(xù)轉(zhuǎn)換所選擇的規(guī)則通道。

注意: 應(yīng)用程序必須確保當(dāng)使用交叉模式時(shí),不能有注入通道的外部觸發(fā)產(chǎn)生。

在 1 個(gè)通道上的慢速交叉模式

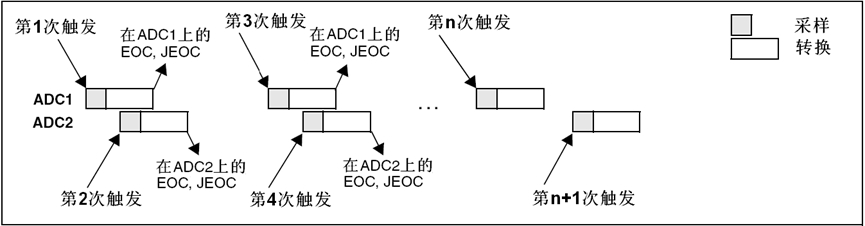

4.5 交替觸發(fā)模式

此模式只適用于注入通道組。外部觸發(fā)源來(lái)自 ADC1 的注入通道多路開(kāi)關(guān)。

當(dāng)?shù)谝粋€(gè)觸發(fā)產(chǎn)生時(shí),ADC1 上的所有注入組通道被轉(zhuǎn)換。

當(dāng)?shù)诙€(gè)觸發(fā)到達(dá)時(shí),ADC2 上的所有注入組通道被轉(zhuǎn)換。

如此循環(huán)……

如果允許產(chǎn)生 JEOC 中斷,在所有 ADC1 注入組通道轉(zhuǎn)換后產(chǎn)生一個(gè) JEOC 中斷。如果允許產(chǎn)生JEOC 中斷,在所有 ADC2 注入組通道轉(zhuǎn)換后產(chǎn)生一個(gè) JEOC 中斷。當(dāng)所有注入組通道都轉(zhuǎn)換完后,如果又有另一個(gè)外部觸發(fā),交替觸發(fā)處理從轉(zhuǎn)換 ADC1 注入組通道重新開(kāi)始。

交替觸發(fā):每個(gè) ADC1 的注入通道組

如果 ADC1 和 ADC2 上同時(shí)使用了注入間斷模式:

當(dāng)?shù)谝粋€(gè)觸發(fā)產(chǎn)生時(shí),ADC1 上的第一個(gè)注入通道被轉(zhuǎn)換。

當(dāng)?shù)诙€(gè)觸發(fā)到達(dá)時(shí),ADC2 上的第一個(gè)注入通道被轉(zhuǎn)換。

如此循環(huán)……

如果允許產(chǎn)生 JEOC 中斷,在所有 ADC1 注入組通道轉(zhuǎn)換后產(chǎn)生一個(gè) JEOC 中斷。如果允許產(chǎn)生JEOC 中斷,在所有 ADC2 注入組通道轉(zhuǎn)換后產(chǎn)生一個(gè) JEOC 中斷。

當(dāng)所有注入組通道都轉(zhuǎn)換完后,如果又有另一個(gè)外部觸發(fā),則重新開(kāi)始交替觸發(fā)過(guò)程。

交替觸發(fā):在間斷模式下每個(gè) ADC 上的 4 個(gè)注入通道

4.6 獨(dú)立模式

此模式里,雙 ADC 同步不工作,每個(gè) ADC 接口獨(dú)立工作。

5 混合的規(guī)則

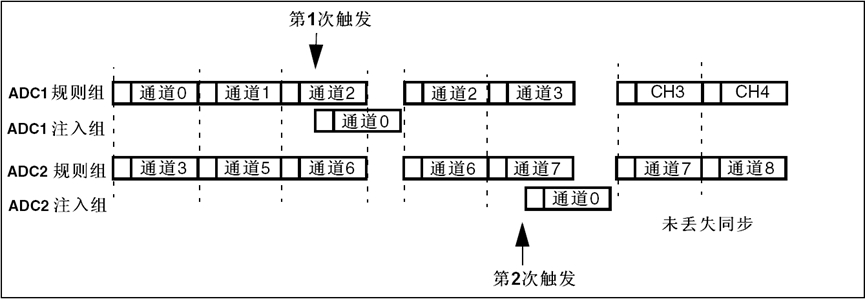

5.1 混合的規(guī)則/注入同步模式

規(guī)則組同步轉(zhuǎn)換可以被中斷,以啟動(dòng)注入組的同步轉(zhuǎn)換。

注: 在混合的規(guī)則/注入同步模式中,必須轉(zhuǎn)換具有相同時(shí)間長(zhǎng)度的序列,或保證觸發(fā)的間隔比 2 個(gè)序列中較長(zhǎng)的序列長(zhǎng),否則當(dāng)較長(zhǎng)序列的轉(zhuǎn)換還未完成時(shí),具有較短序列的 ADC 轉(zhuǎn)換可能會(huì)被重啟。

5.2 混合的同步規(guī)則+交替觸發(fā)模式

規(guī)則組同步轉(zhuǎn)換可以被中斷,以啟動(dòng)注入組交替觸發(fā)轉(zhuǎn)換。圖 顯示了一個(gè)規(guī)則同步轉(zhuǎn)換被交替觸發(fā)所中斷。注入交替轉(zhuǎn)換在注入事件到達(dá)后立即啟動(dòng)。如果規(guī)則轉(zhuǎn)換已經(jīng)在運(yùn)行,為了在注入轉(zhuǎn)換后確保同步,所有的 ADC(主和從)的規(guī)則轉(zhuǎn)換被停止,并在注入轉(zhuǎn)換結(jié)束時(shí)同步恢復(fù)。

注: 在混合的同步規(guī)則+交替觸發(fā)模式中,必須轉(zhuǎn)換具有相同時(shí)間長(zhǎng)度的序列,或保證觸發(fā)的間隔比 2個(gè)序列中較長(zhǎng)的序列長(zhǎng),否則當(dāng)較長(zhǎng)序列的轉(zhuǎn)換還未完成時(shí),具有較短序列的 ADC 轉(zhuǎn)換可能會(huì)被重啟。

交替+規(guī)則同步

如果觸發(fā)事件發(fā)生在一個(gè)中斷了規(guī)則轉(zhuǎn)換的注入轉(zhuǎn)換期間,這個(gè)觸發(fā)事件將被忽略。下圖示出了這種情況的操作(第 2 個(gè)觸發(fā)被忽略)。

觸發(fā)事件發(fā)生在注入轉(zhuǎn)換期間

5.3 混合同步注入+交叉模式

一個(gè)注入事件可以中斷一個(gè)交叉轉(zhuǎn)換。這種情況下,交叉轉(zhuǎn)換被中斷,注入轉(zhuǎn)換被啟動(dòng),在注入序列轉(zhuǎn)換結(jié)束時(shí),交叉轉(zhuǎn)換被恢復(fù)。下圖是這種情況的一個(gè)例子。

注: 當(dāng) ADC 時(shí)鐘預(yù)分頻系數(shù)設(shè)置為 4 時(shí),交叉模式恢復(fù)后不會(huì)均勻地分配采樣時(shí)間,采樣間隔是 8 個(gè)ADC 時(shí)鐘周期與 6 個(gè) ADC 時(shí)鐘周期輪替,而不是均勻的 7 個(gè) ADC 時(shí)鐘周期。

交叉的單通道轉(zhuǎn)換被注入序列 CH11 和 CH12 中斷

6 溫度傳感器

溫度傳感器可以用來(lái)測(cè)量器件周圍的溫度(TA)。

溫度傳感器在內(nèi)部和 ADC1_IN16 輸入通道相連接,此通道把傳感器輸出的電壓轉(zhuǎn)換成數(shù)字值。溫度傳感器模擬輸入推薦采樣時(shí)間是 17.1μs。當(dāng)沒(méi)有被使用時(shí),傳感器可以置于關(guān)電模式。

注意: 必須設(shè)置 TSVREFE 位激活內(nèi)部通道:ADC1_IN16(溫度傳感器)和 ADC1_IN17(VREFINT)的轉(zhuǎn)換。溫度傳感器輸出電壓隨溫度線性變化,由于生產(chǎn)過(guò)程的變化,溫度變化曲線的偏移在不同芯片上會(huì)有不同(最多相差 45°C)。

內(nèi)部溫度傳感器更適合于檢測(cè)溫度的變化,而不是測(cè)量絕對(duì)的溫度。如果需要測(cè)量精確的溫度,應(yīng)該使用一個(gè)外置的溫度傳感器。

溫度傳感器和 VREFINT 通道框圖

讀溫度

為使用傳感器:

1. 選擇 ADC1_IN16 輸入通道

2. 選擇采樣時(shí)間為 17.1μs

3. 設(shè)置 ADC 控制寄存器 2(ADC_CR2)的 TSVREFE 位,以喚醒關(guān)電模式下的溫度傳感器

4. 通過(guò)設(shè)置 ADON 位啟動(dòng) ADC 轉(zhuǎn)換(或用外部觸發(fā))

5. 讀 ADC 數(shù)據(jù)寄存器上的 VSENSE 數(shù)據(jù)結(jié)果

6. 利用下列公式得出溫度

溫度(°C)={(V25-VSENSE)/Avg_Slope}+25

這里:

V25=VSENSE 在 25°C 時(shí)的數(shù)值

Avg_Slope=溫度與 VSENSE 曲線的平均斜率(單位為 mV/°C 或μV/°C)參考數(shù)據(jù)手冊(cè)的電氣

特性章節(jié)中 V25 和 Avg_Slope 的實(shí)際值。

注意: 傳感器從關(guān)電模式喚醒后到可以輸出正確水平的 VSENSE 前,有一個(gè)建立時(shí)間。ADC 在上電后也有一個(gè)建立時(shí)間,因此為了縮短延時(shí),應(yīng)該同時(shí)設(shè)置 ADON 和 TSVREFE 位

7 ADC中斷

規(guī)則和注入組轉(zhuǎn)換結(jié)束時(shí)能產(chǎn)生中斷,當(dāng)模擬看門狗狀態(tài)位被設(shè)置時(shí)也能產(chǎn)生中斷。它們都有獨(dú)立的中斷使能位。

注: ADC1 和 ADC2 的中斷映射在同一個(gè)中斷向量上,而 ADC3 的中斷有自己的中斷向量

ADC_SR 寄存器中有 2 個(gè)其他標(biāo)志,但是它們沒(méi)有相關(guān)聯(lián)的中斷:

JSTRT(注入組通道轉(zhuǎn)換的啟動(dòng))

STRT(規(guī)則組通道轉(zhuǎn)換的啟動(dòng))

| 中斷事件 | 事件標(biāo)志 | 使能控制位 |

| 規(guī)則組轉(zhuǎn)換結(jié)束 | EOC | EOCIE |

| 注入組轉(zhuǎn)換結(jié)束 | JEOC | JEOCIE |

| 設(shè)置了模擬看門狗狀態(tài)位 | AWD | AWDIE |

8 例程設(shè)計(jì)

8.1 ADC_AnalogWatchdog例程

1.初始化部分

// 延時(shí)函數(shù)初始化(由delay.h提供)

delay_init();

// UART配置函數(shù)

void UART_Configuration(void)

{

GPIO_InitTypeDef GPIO_InitStructure;

USART_InitTypeDef USART_InitStructure;

// 使能USART1和GPIOA時(shí)鐘

RCC_APB2PeriphClockCmd(RCC_APB2Periph_USART1 | RCC_APB2Periph_GPIOA, ENABLE);

// 配置TX引腳(PA9)為復(fù)用推挽輸出

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_9;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init(GPIOA, &GPIO_InitStructure);

// 配置RX引腳(PA10)為浮空輸入

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_10;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING;

GPIO_Init(GPIOA, &GPIO_InitStructure);

// 配置串口參數(shù):115200bps, 8位數(shù)據(jù), 1位停止位, 無(wú)校驗(yàn)

USART_InitStructure.USART_BaudRate = 115200;

USART_InitStructure.USART_WordLength = USART_WordLength_8b;

USART_InitStructure.USART_StopBits = USART_StopBits_1;

USART_InitStructure.USART_Parity = USART_Parity_No;

USART_InitStructure.USART_HardwareFlowControl = USART_HardwareFlowControl_None;

USART_InitStructure.USART_Mode = USART_Mode_Rx | USART_Mode_Tx;

USART_Init(USART1, &USART_InitStructure);

USART_Cmd(USART1, ENABLE);

}

// ADC配置函數(shù)

void ADC_Configuration(void)

{

ADC_InitTypeDef ADC_InitStructure;

NVIC_InitTypeDef NVIC_InitStructure;

// 使能GPIOA和ADC1時(shí)鐘

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA | RCC_APB2Periph_ADC1, ENABLE);

RCC_ADCCLKConfig(RCC_PCLK2_Div8); // ADC時(shí)鐘=PCLK2/8(假設(shè)PCLK2=72MHz,ADC時(shí)鐘=9MHz)

ADC_DeInit(ADC1); // 復(fù)位ADC1配置

// 配置ADC為獨(dú)立模式,單通道單次轉(zhuǎn)換

ADC_InitStructure.ADC_Mode = ADC_Mode_Independent;

ADC_InitStructure.ADC_ScanConvMode = DISABLE; // 非掃描模式

ADC_InitStructure.ADC_ContinuousConvMode = DISABLE; // 單次轉(zhuǎn)換模式

ADC_InitStructure.ADC_ExternalTrigConv = ADC_ExternalTrigConv_None; // 軟件觸發(fā)

ADC_InitStructure.ADC_DataAlign = ADC_DataAlign_Right; // 右對(duì)齊

ADC_InitStructure.ADC_NbrOfChannel = 1; // 轉(zhuǎn)換通道數(shù)1

ADC_Init(ADC1, &ADC_InitStructure);

ADC_Cmd(ADC1, ENABLE); // 使能ADC1

// 配置NVIC中斷優(yōu)先級(jí)

NVIC_InitStructure.NVIC_IRQChannel = ADC1_2_IRQn;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0; // 最高搶占優(yōu)先級(jí)

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0;

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStructure);

// 配置ADC通道10(PA0),采樣時(shí)間239.5周期

ADC_RegularChannelConfig(ADC1, ADC_Channel_10, 1, ADC_SampleTime_239Cycles5);

// 配置模擬看門狗:監(jiān)測(cè)通道10,閾值范圍1024~2048(對(duì)應(yīng)電壓0.825V~1.65V,假設(shè)VREF=3.3V)

ADC_AnalogWatchdogSingleChannelConfig(ADC1, ADC_Channel_10);

ADC_AnalogWatchdogThresholdsConfig(ADC1, 2048, 1024);

ADC_AnalogWatchdogCmd(ADC1, ADC_AnalogWatchdog_SingleRegEnable); // 使能單通道看門狗

ADC_ITConfig(ADC1, ADC_IT_AWD, ENABLE); // 使能模擬看門狗中斷

// ADC校準(zhǔn)(關(guān)鍵步驟,確保轉(zhuǎn)換精度)

ADC_ResetCalibration(ADC1);

while (ADC_GetResetCalibrationStatus(ADC1));

ADC_StartCalibration(ADC1);

while (ADC_GetCalibrationStatus(ADC1));

}

- ?延時(shí)函數(shù)初始化:調(diào)用delay_init()函數(shù),為后續(xù)的延時(shí)操作做準(zhǔn)備。

- ?UART 配置:UART_Configuration()函數(shù)用于配置 USART1,包含使能時(shí)鐘、設(shè)置 GPIO 引腳、初始化串口參數(shù)(如波特率、數(shù)據(jù)位、停止位等),并且使能串口。

- ?ADC 配置:ADC_Configuration()函數(shù)對(duì) ADC1 進(jìn)行配置,具體操作有使能時(shí)鐘、設(shè)置 ADC 時(shí)鐘分頻、初始化 ADC 參數(shù)(如工作模式、轉(zhuǎn)換模式等)、配置模擬看門狗(設(shè)定監(jiān)測(cè)通道和閾值)、使能模擬看門狗中斷以及進(jìn)行 ADC 校準(zhǔn)。

2.主循環(huán)部分

int main(void)

{

RCC_ClocksTypeDef clocks;

delay_init();

UART_Configuration();

ADC_Configuration();

RCC_GetClocksFreq(&clocks);

// 打印系統(tǒng)時(shí)鐘信息

printf("n");

printf("SYSCLK: %3.1fMhz, HCLK: %3.1fMhz, PCLK1: %3.1fMhz, PCLK2: %3.1fMhz, ADCCLK: %3.1fMhzn",

(float)clocks.SYSCLK_Frequency / 1000000, (float)clocks.HCLK_Frequency / 1000000,

(float)clocks.PCLK1_Frequency / 1000000, (float)clocks.PCLK2_Frequency / 1000000, (float)clocks.ADCCLK_Frequency / 1000000);

printf("ADC Analog Watchdog Testn");

printf("LTR: 1024, HTR: 2048n");

// 主循環(huán):周期性觸發(fā)ADC轉(zhuǎn)換

while (1)

{

ADC_SoftwareStartConvCmd(ADC1, ENABLE); // 軟件觸發(fā)ADC轉(zhuǎn)換

delay_ms(200); // 等待轉(zhuǎn)換完成并延時(shí)200ms

}

}

在main函數(shù)的無(wú)限循環(huán)里,每隔 200ms 啟動(dòng)一次 ADC 轉(zhuǎn)換。這樣做的目的是周期性地對(duì) ADC 通道進(jìn)行采樣。

3.中斷處理部分

// 模擬看門狗中斷處理函數(shù)

void ADC1_2_IRQHandler(void)

{

ADC_ITConfig(ADC1, ADC_IT_AWD, DISABLE); // 臨時(shí)禁用中斷,避免重復(fù)觸發(fā)

if (SET == ADC_GetFlagStatus(ADC1, ADC_FLAG_AWD)) // 檢查模擬看門狗標(biāo)志

{

ADC_ClearFlag(ADC1, ADC_FLAG_AWD); // 清除中斷標(biāo)志

ADC_ClearITPendingBit(ADC1, ADC_IT_AWD); // 清除中斷掛起位

// 打印觸發(fā)中斷的ADC值(12位精度,范圍0~4095)

printf("ADC Awd is Happened. Code Value = %d rn", ADC1->DR);

}

ADC_ITConfig(ADC1, ADC_IT_AWD, ENABLE); // 重新使能中斷

}

ADC1_2_IRQHandler函數(shù)作為模擬看門狗中斷的處理函數(shù)。當(dāng) ADC 值超出預(yù)設(shè)的閾值范圍時(shí),會(huì)觸發(fā)該中斷。在中斷處理過(guò)程中,先禁用中斷,接著清除中斷標(biāo)志和掛起位,然后打印出觸發(fā)中斷時(shí)的 ADC 值,最后重新使能中斷。

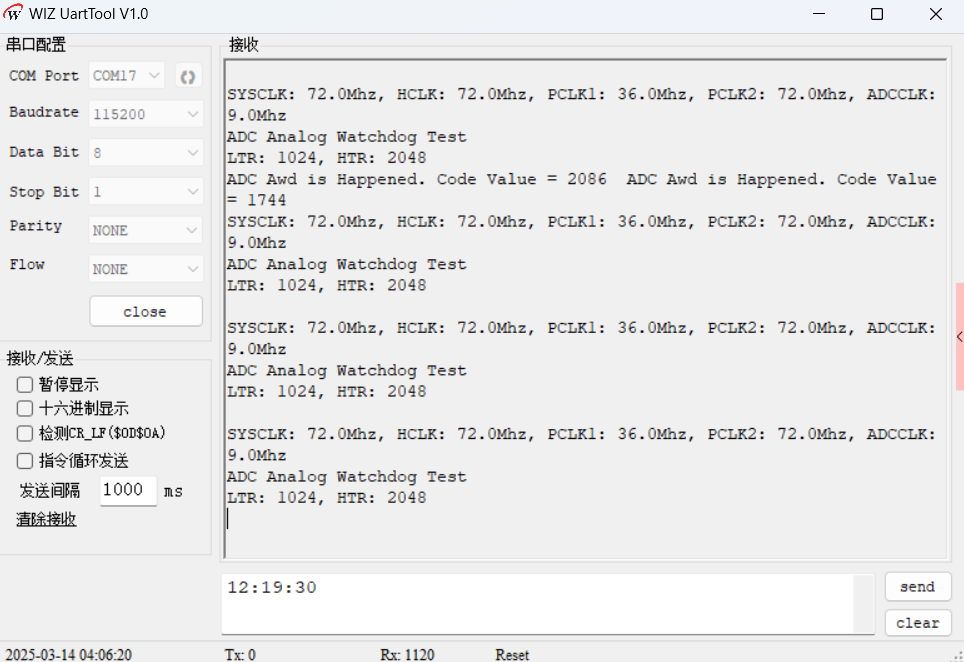

9 下載驗(yàn)證

9.1 ADC_AnalogWatchdog例程

實(shí)驗(yàn)現(xiàn)象分析

系統(tǒng)啟動(dòng)信息: 系統(tǒng)啟動(dòng)后,會(huì)在串口輸出系統(tǒng)時(shí)鐘頻率信息,同時(shí)顯示正在進(jìn)行 ADC 模擬看門狗測(cè)試以及預(yù)設(shè)的下限和上限。

ADC 轉(zhuǎn)換: 系統(tǒng)會(huì)每隔 200ms 啟動(dòng)一次 ADC 轉(zhuǎn)換。若輸入到 ADC 通道 10 的電壓值處于 1024 - 2048 的范圍內(nèi),不會(huì)有額外信息輸出。

模擬看門狗觸發(fā):當(dāng)輸入到 ADC 通道 10 的電壓值超出 1024 - 2048 的范圍時(shí),會(huì)觸發(fā)模擬看門狗中斷,在串口輸出觸發(fā)中斷時(shí)的 ADC 值。

持續(xù)運(yùn)行: 系統(tǒng)會(huì)持續(xù)運(yùn)行,不斷進(jìn)行 ADC 轉(zhuǎn)換,并在需要時(shí)觸發(fā)模擬看門狗中斷。

WIZnet 是一家無(wú)晶圓廠半導(dǎo)體公司,成立于 1998 年。產(chǎn)品包括互聯(lián)網(wǎng)處理器 iMCU?,它采用 TOE(TCP/IP 卸載引擎)技術(shù),基于獨(dú)特的專利全硬連線 TCP/IP。iMCU? 面向各種應(yīng)用中的嵌入式互聯(lián)網(wǎng)設(shè)備。

WIZnet 在全球擁有 70 多家分銷商,在香港、韓國(guó)、美國(guó)設(shè)有辦事處,提供技術(shù)支持和產(chǎn)品營(yíng)銷。

香港辦事處管理的區(qū)域包括:澳大利亞、印度、土耳其、亞洲(韓國(guó)和日本除外)。

-

傳感器

+關(guān)注

關(guān)注

2564文章

52821瀏覽量

765709 -

單片機(jī)

+關(guān)注

關(guān)注

6067文章

44967瀏覽量

649096 -

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5615瀏覽量

175428 -

adc

+關(guān)注

關(guān)注

99文章

6673瀏覽量

548781 -

數(shù)字轉(zhuǎn)換器

+關(guān)注

關(guān)注

0文章

239瀏覽量

28059

發(fā)布評(píng)論請(qǐng)先 登錄

第十章 W55MH32中斷應(yīng)用概覽

第十四章 USART——串口通訊

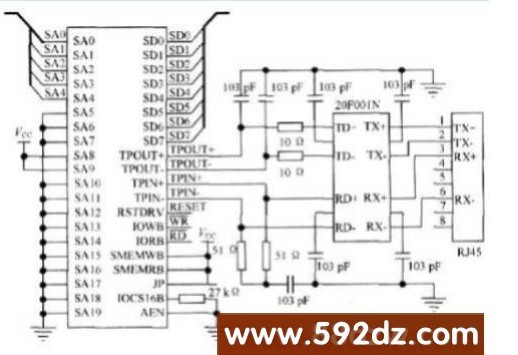

基于AVR高性能單片機(jī)的以太網(wǎng)接口設(shè)計(jì)

W5100在單片機(jī)實(shí)現(xiàn)以太網(wǎng)通信中的應(yīng)用

高性能單片機(jī)Mega64和10Mb/s以太網(wǎng)控制芯片,實(shí)現(xiàn)以太網(wǎng)接口設(shè)計(jì)方案

WIZnet高性能以太網(wǎng)單片機(jī)W55MH32重磅發(fā)布!

即刻啟程,踏上W55MH32高性能以太網(wǎng)單片機(jī)學(xué)習(xí)之路!

第一章 W55MH32 高性能以太網(wǎng)單片機(jī)的學(xué)習(xí)方法概述

第二章 開(kāi)發(fā)板與芯片介紹 詳解W55MH32芯片及開(kāi)發(fā)板

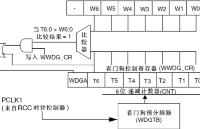

W55MH32高性能以太網(wǎng)單片機(jī)教程 第九章 窗口看門狗(WWDG)

WIZnet W55MH32以太網(wǎng)單片機(jī)開(kāi)發(fā)教程 第十一章 通用定時(shí)器(上篇)

WIZnet W55MH32以太網(wǎng)單片機(jī)開(kāi)發(fā)教程第十一章 通用定時(shí)器(下篇)

W55MH32高性能以太網(wǎng)單片機(jī)開(kāi)發(fā)課件 第十四章 ADC(上篇)

W55MH32高性能以太網(wǎng)單片機(jī)開(kāi)發(fā)課件 第十四章 ADC(上篇)

評(píng)論