基于MATLAB實現(xiàn)FM調(diào)制解調(diào)

首先FM調(diào)制時屬于非線性調(diào)制中的一種,常見的非線性調(diào)制時FM(頻率調(diào)制),PM(相位)調(diào)制。

詳解ADC電路的靜態(tài)仿真和動態(tài)仿真

ADC電路主要存在靜態(tài)仿真和動態(tài)仿真兩類仿真,針對兩種不同的仿真,我們存在不同的輸入信號和不同的數(shù)據(jù)....

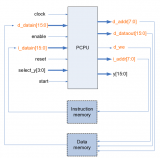

基于FPGA搭建神經(jīng)網(wǎng)絡(luò)的步驟解析

本文的目的是在一個神經(jīng)網(wǎng)絡(luò)已經(jīng)通過python或者M(jìn)ATLAB訓(xùn)練好的神經(jīng)網(wǎng)絡(luò)模型,將訓(xùn)練好的模型的....

基于FPGA的AM調(diào)制系統(tǒng)設(shè)計方案

本系統(tǒng)由FPGA、串口屏、DAC模塊和AD831組成。FPGA通過調(diào)用宏功能模塊NCO,按照輸入時鐘....

Xilinx Shift RAM IP概述和主要功能

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一個 LogiCORE IP....

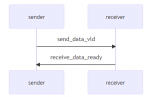

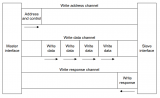

AXI協(xié)議規(guī)范總結(jié)

寫數(shù)據(jù)通道從主設(shè)備傳輸數(shù)據(jù)到從設(shè)備,在寫傳輸時,從設(shè)備使用寫響應(yīng)通道通知主設(shè)備傳輸完成。

在Vivado調(diào)用MIG產(chǎn)生DDR3的問題解析

下面是調(diào)用的DDR3模塊的,模塊的倒數(shù)第二行是,模塊的時鐘輸入,時鐘源來自PLL產(chǎn)生的系統(tǒng)時鐘的倍頻....

Xilinx Ultrascale系列FPGA的時鐘資源與架構(gòu)解析

Ultrascale是賽靈思開發(fā)的支持包含步進(jìn)功能的增強(qiáng)型FPGA架構(gòu),相比7系列的28nm工藝,U....

Vivado HLS設(shè)計流程

為了盡快把新產(chǎn)品推向市場,數(shù)字系統(tǒng)的設(shè)計者需要考慮如何加速設(shè)計開發(fā)的周期。設(shè)計加速主要可以從“設(shè)計的....

Verilog編寫規(guī)范

用最右邊的字符下劃線代表低電平有效,高電平有效的信號不得以下劃線表示,短暫的有效信號建議采用高電平有....