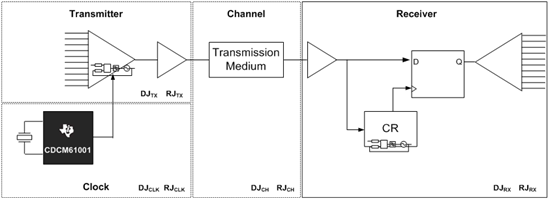

ADC 設(shè)計(jì)的最新進(jìn)展極大地?cái)U(kuò)展了可用輸入范圍,這樣系統(tǒng)設(shè)計(jì)人員便可以去掉至少一個中間頻率級,從而降低成本和功耗。在欠采樣接收機(jī)設(shè)計(jì)中必須要特別注意采樣時鐘,因?yàn)樵谝恍└咻斎腩l率下時鐘抖動會成為限制信噪比 (SNR) 的主要原因。本文章重點(diǎn)介紹如何準(zhǔn)確地估算某個時鐘源的抖動,以及如何將其與ADC 的孔徑抖動組合。

采樣過程回顧

根據(jù) Nyquist-Shannon 采樣定理,如果以至少兩倍于其最大頻率的速率來對原始輸入信號采樣,則其可以得到完全重建。假設(shè)以 100 MSPS 的速率對高達(dá) 10MHz 的輸入信號采樣,則不管該信號是位于 1 到 10MHz 的基帶(首個Nyquist 區(qū)域),還是在 100 到 110MHz 的更高 Nyquist 區(qū)域內(nèi)欠采樣,都沒關(guān)系(請參見圖 1)。

?

圖 1 100MSPS 采樣的兩個輸入信號顯示了混疊帶來的相同采樣點(diǎn)

在更高(第二個、第三個等)Nyquist 區(qū)域中采樣,一般被稱作欠采樣或次采樣。然而,在 ADC 前面要求使用抗混疊過濾,以對理想 Nyquist 區(qū)域采樣,同時避免重建原始信號過程中產(chǎn)生干擾。

時域抖動

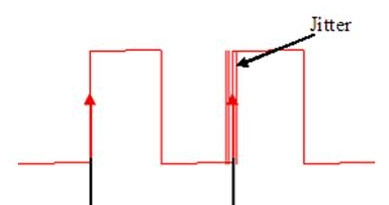

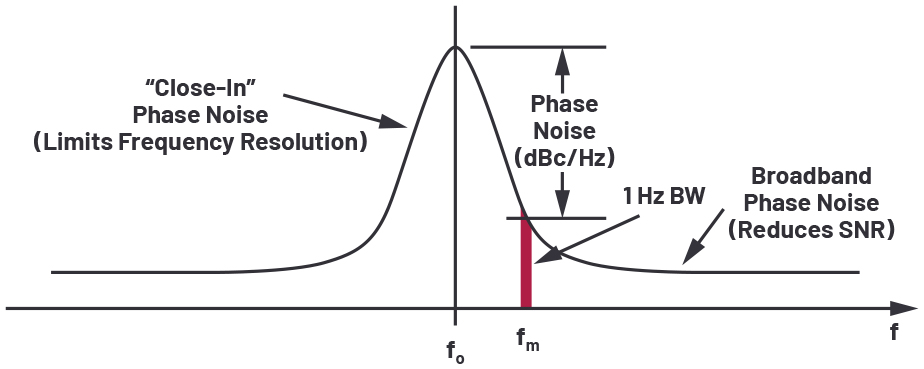

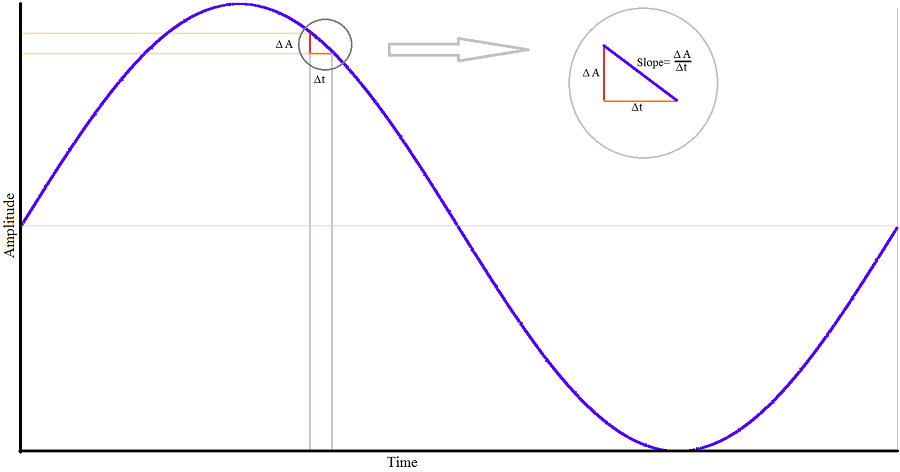

仔細(xì)觀察某個采樣點(diǎn),可以看到計(jì)時不準(zhǔn)(時鐘抖動或時鐘相位噪聲)是如何形成振幅變化的。由于高 Nyquist 區(qū)域(例如,f1 = 10 MHz 到 f2 = 110 MHz)欠采樣帶來輸入頻率的增加,固定數(shù)量的時鐘抖動自理想采樣點(diǎn)產(chǎn)生更大數(shù)量的振幅偏差(噪聲)。另外,圖 2 表明時鐘信號自身轉(zhuǎn)換速率對采樣時間的變化產(chǎn)生了影響。轉(zhuǎn)換速率決定了時鐘信號通過零交叉點(diǎn)的快慢。換句話說,轉(zhuǎn)換速率直接影響 ADC 中時鐘電路的觸發(fā)閾值。

圖 2 時鐘抖動形成更多快速輸入信號振幅誤差

如果 ADC 的內(nèi)部時鐘緩沖器上存在固定數(shù)量的熱噪聲,則轉(zhuǎn)換速率也轉(zhuǎn)換為計(jì)時不準(zhǔn),從而降低了 ADC 的固有窗口抖動。如圖 3 所示,窗口抖動與時鐘抖動(相位噪聲)沒有一點(diǎn)關(guān)系,但是這兩種抖動分量在采樣時間組合在一起。

?

圖3 ADC的窗口抖動

圖3還表明窗口抖動隨轉(zhuǎn)換速率降低而增加。轉(zhuǎn)換速率一般直接取決于時鐘振幅。

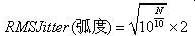

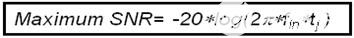

時鐘抖動導(dǎo)致的 SNR 減弱

有幾個因素會限制 ADC 的 SNR,例如:量化噪聲(管線式轉(zhuǎn)換器中一般不明顯)、熱噪聲(其在低輸入頻率下限制 SNR),以及時鐘抖動(SNRJitter)(請參見下面方程式 1)。SNRJitter 部分受到輸入頻率 fIN(取決于 Nyquist 區(qū)域)的限制,同時受總時鐘抖動量 tJitter 的限制,其計(jì)算方法如下:

?

SNRJitter[dBc]=-20×log(2π×fIN×tJitter)??(2)

正如我們預(yù)計(jì)的那樣,利用固定數(shù)量的時鐘抖動,SNR 隨輸入頻率上升而下降。圖 4 描述了這種現(xiàn)象,其顯示了 400 fs 固定時鐘抖動時一個 14 位管線式轉(zhuǎn)換器的 SNR。如果輸入頻率增加十倍,例如:從 10MHz 增加到 100MHz,則時鐘抖動帶來的最大實(shí)際 SNR 降低 20dB。

?

圖4 SNR 隨輸入頻率上升而下降

如前所述,限制 ADC SNR 的另一個主要因素是 ADC 的熱噪聲,其不隨輸入頻率變化。一個 14 位管線式轉(zhuǎn)換器一般有 ~70 到 74 dB 的熱噪聲,如圖 4 所示。我們可以在產(chǎn)品說明書中找到 ADC 的熱噪聲,其相當(dāng)于最低指定輸入頻率(本例中為 10MHz)的 SNR,其中時鐘抖動還不是一個因素。

讓我們來對一個具有 400 fs 抖動時鐘電路和 ~73 dB 熱噪聲的 14 位 ADC 進(jìn)行分析。低輸入頻率(例如:10MHz 等)下,該 ADC 的 SNR 主要由其熱噪聲定義。由于輸入頻率增加,400-fs 時鐘抖動越來越占據(jù)主導(dǎo),直到 ~300 MHz 時完全接管。盡管相比 10MHz 的 SNR,100MHz 輸入頻率下時鐘抖動帶來的 SNR 每十倍頻降低 20dB,但是總 SNR 僅降低 ~3.5 dB(降至 69.5dB),因?yàn)榇嬖?73-dB 熱噪聲(請參見圖 5):

?

圖 5 產(chǎn)生的 ADC SNR 受熱噪聲和時鐘抖動的限制

?

現(xiàn)在,很明顯,如果 ADC 的熱噪聲增加,對高輸入頻率采樣時時鐘抖動便非常重要。例如,一個 16 位 ADC 具有 ~77 到 80 dB 的熱噪聲層。根據(jù)圖 4 所示曲線圖,為了最小化 100MHz 輸入頻率 SNR 的時鐘抖動影響,時鐘抖動需為大約 150 fs 或更高。

確定采樣時鐘抖動

如前所述,采樣時鐘抖動由時鐘的計(jì)時不準(zhǔn)(相位噪聲)和 ADC 的窗口抖動組成。這兩個部分結(jié)合組成如下:

?

我們在產(chǎn)品說明書中可以找到 ADC 的孔徑口抖動 (aperture jitter)。這一值一般與時鐘振幅或轉(zhuǎn)換速率一起指定,記住這一點(diǎn)很重要。低時鐘振幅帶來低轉(zhuǎn)換速率,從而增加窗口抖動。

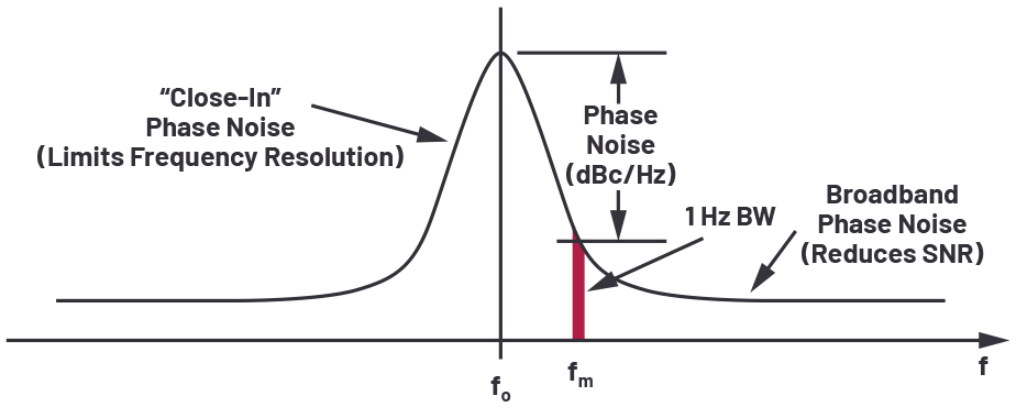

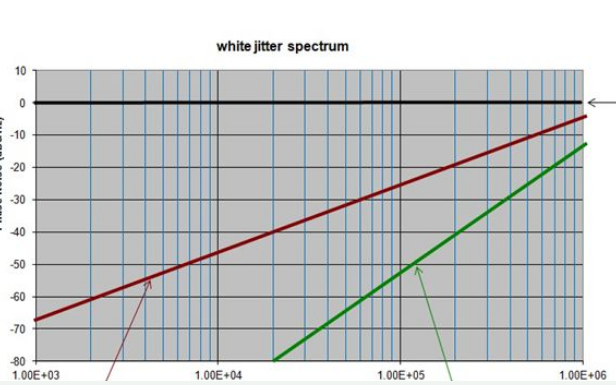

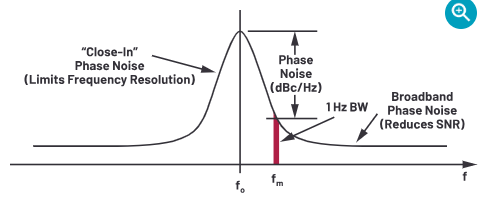

時鐘輸入抖動

時鐘鏈(振蕩器、時鐘緩沖器或 PLL)中器件的輸出抖動一般規(guī)定在某個頻率范圍內(nèi),該頻率通常偏離于基本時鐘頻率 10 kHz 到 20 MHz(單位也可以是微微秒或者繪制成相位噪聲圖),可以將其整合到一起獲取抖動信息。但是,低端的 10kHz 和高端的 20MHz 有時并非正確的使用邊界,因?yàn)樗鼈冋{(diào)試依賴于其他系統(tǒng)參數(shù),我們將在后面進(jìn)行詳細(xì)介紹。圖 6 描述了設(shè)置正確整合限制的重要性。

?

圖 6 每十倍頻計(jì)算得到的時鐘相位噪聲抖動影響

圖中的相位噪聲圖以其每十倍頻抖動內(nèi)容覆蓋。我們可以看到,如果將下限設(shè)定為 100-Hz 或 10kHz 偏移,則產(chǎn)生的抖動便極為不同。同樣地,例如,設(shè)置上整合限制為 10 或 20MHz,可得到相比 100MHz 設(shè)置極為不同的結(jié)果。

確定正確的整合下限

在采樣過程中,輸入信號與采樣時鐘信號混頻在一起,包括其相位噪聲。當(dāng)進(jìn)行輸入信號 FFT 分析時,主 FFT 容器 (bin) 集中于輸入信號。采樣信號周圍的相位噪聲(來自時鐘或輸入信號)決定了鄰近主容器的一些容器的振幅,如圖 7 所示。

?

圖 7 近區(qū)相位噪聲決定主容器附近 FFT 容器的振幅

因此,小于 1/2 容器尺寸的偏頻的所有相位噪聲都集中于輸入信號容器中,且未增加噪聲。因此,相位噪聲整合帶寬下限應(yīng)設(shè)定為 1/2 FFT 容器尺寸。 FFT 容器尺寸計(jì)算方法如下:

為了進(jìn)一步描述該點(diǎn),我們利用兩個不同的FFT尺寸—131,072 和 1,048,576 點(diǎn),使用 ADS54RF63 進(jìn)行實(shí)驗(yàn)。采樣速率設(shè)定為 122.88MSPS,而圖 8 則顯示了時鐘相位噪聲。

?

圖8 時鐘相位噪聲

我們將一個 6-MHz、寬帶通濾波器添加到時鐘輸入,以限制影響抖動的寬帶噪聲數(shù)量。選擇 1-GHz 輸入信號的目的是確保 SNR 減弱僅由于時鐘抖動。圖 8 表明兩個 FFT 尺寸的 1/2 容器尺寸到 40MHz 相位噪聲整合抖動結(jié)果都極為不同,而“表 1”的 SNR 測量情況也反映這種現(xiàn)象。

設(shè)置正確的整合上限

圖 6 所示相位噪聲圖抖動貢獻(xiàn)量為 ~360 fs,其頻率偏移為 10 到 100MHz 之間。這比 100Hz 到 10MHz 之間偏移的所有 ~194 fs 抖動貢獻(xiàn)值要大得多。因此,所選整合上限可極大地影響計(jì)算得到的時鐘抖動,以及預(yù)計(jì)SNR匹配實(shí)際測量的好壞程度。

要確定正確的限制,您必須記住采樣過程中非常重要的事情是:來自其他尼奎斯特區(qū)域的時鐘信號偽帶內(nèi)噪聲和雜散,正如其出現(xiàn)在輸入信號時表現(xiàn)的那樣。因此,如果時鐘輸入的相位噪聲不受頻帶限制,同時沒有高頻規(guī)律性衰減,則整合上限由變壓器(如果使用的話)帶寬和 ADC 自身的時鐘輸入設(shè)定。一些情況下,時鐘輸入帶寬可以非常大;例如,ADS54RF63 具有 ~2 GHz 的時鐘輸入帶寬,旨在允許高時鐘轉(zhuǎn)換速率的高階諧波。

若想要驗(yàn)證時鐘相位噪聲是否需要整合至?xí)r鐘輸入帶寬,則需建立另一個實(shí)驗(yàn)。ADS54RF63 再次工作在 122.88 MSPS,其輸入信號為 1GHz,以確保 SNR 抖動得到控制。我們利用一個 RF 放大器,生成 50MHz 到 1GHz 的寬帶白噪聲,并將其添加至采樣時鐘,如圖 9 所示。之后,我們使用幾個不同低通濾波器 (LPF) 來限制添加至?xí)r鐘信號的噪聲量。

?

圖9 加寬帶白噪聲的時鐘相位噪聲

ADS54RF63 的時鐘輸入帶寬為 ~2 GHz,但由于 RF 放大器和變壓器都具有 ~1 GHz 的 3-dB帶寬,因此有效 3-dB 時鐘輸入帶寬被降低至 ~500 MHz。“表 2”所示測得 SNR 結(jié)果證實(shí),就本裝置而言,實(shí)際時鐘輸入帶寬約為 500MHz。圖 10 所示 FFT 對比圖進(jìn)一步證實(shí)了 RF 放大器的寬帶噪聲限制了噪聲層,并降低了 SNR。

?

圖10 FFT 對比圖

該實(shí)驗(yàn)表明,時鐘相位噪聲必需非常低或者帶寬有限,較為理想的情況是通過一個很窄的帶通濾波器。否則,由系統(tǒng)時鐘帶寬設(shè)定的整合上限會極大降低 ADC 的 SNR。

結(jié)論

本文介紹了如何準(zhǔn)確地估算采樣時鐘抖動,以及如何計(jì)算正確的上下整合邊界。

電子發(fā)燒友App

電子發(fā)燒友App

評論