文章來源:學習那些事

原文作者:小陳婆婆

本文介紹了晶圓揀選測試的目標、具體過程以及核心要點。

在半導體制造流程中,晶圓揀選測試(Wafer Sort)堪稱芯片從“原材料”到“成品”的關鍵質控節點。作為集成電路制造中承上啟下的核心環節,其通過精密的電學測試,為每一顆芯片頒發“質量合格證”,同時為工藝優化提供數據支撐。

1測試目標

一、核心目標

晶圓揀選測試的核心目標可拆解為四大維度:

功能驗證的“全身體檢”

通過探針卡與芯片焊盤的物理接觸,測試系統依據DC(直流)、AC(交流)及功能規范,對芯片進行全信號通路檢測。這相當于為芯片設計了一套“體檢套餐”:

AC測試:考核信號傳輸速度、建立保持時間等動態特性

功能測試:通過向量激勵驗證數字/模擬電路功能實現

只有通過所有測試項的芯片,才能獲得進入封裝工序的“通行證”。

性能分級的“賽道劃分”

對合格芯片實施速度分級(Speed Binning),通過調整測試條件(如電壓、溫度、時鐘頻率),將芯片按工作速度劃分為不同等級。例如:

高速檔:適用于高性能計算芯片

標準檔:滿足消費級產品需求

這種分級策略可實現芯片價值的最大化利用,避免“大材小用”或“小材大用”。

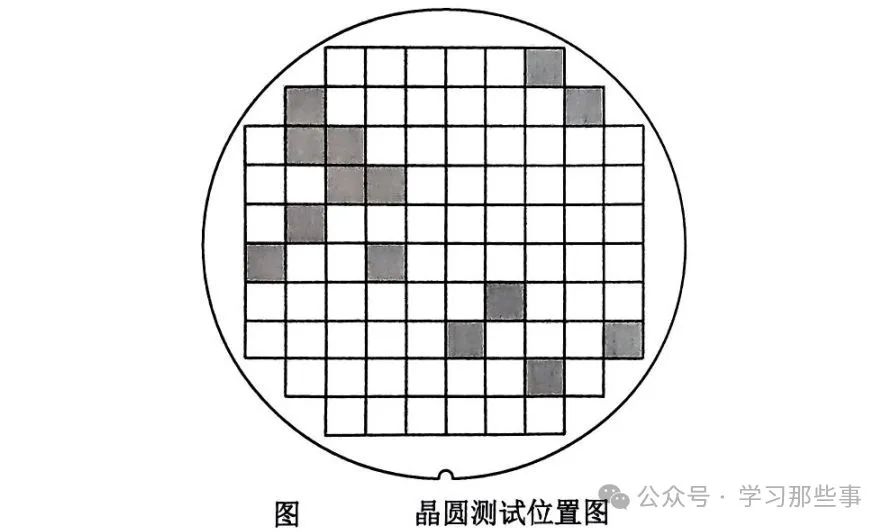

制造成品率的“健康診斷”

測試數據會生成晶圓級良率地圖(Wafer Map),通過空間分布分析可追溯失效模式:

環形失效:可能源于光刻膠涂布不均

邊緣聚集失效:需檢查研磨工藝參數

隨機點狀失效:需排查晶圓本身缺陷

這些數據為工藝工程師提供了“CT掃描”般的診斷依據。

測試覆蓋率的“成本平衡”

在測試成本與缺陷檢出率之間尋求最優解,采用:

結構化測試:通過掃描鏈(Scan Chain)檢測內部節點

邊界掃描(JTAG):驗證芯片間互連完整性

先進測試策略可使測試覆蓋率達99%以上,同時控制測試時間在秒級。

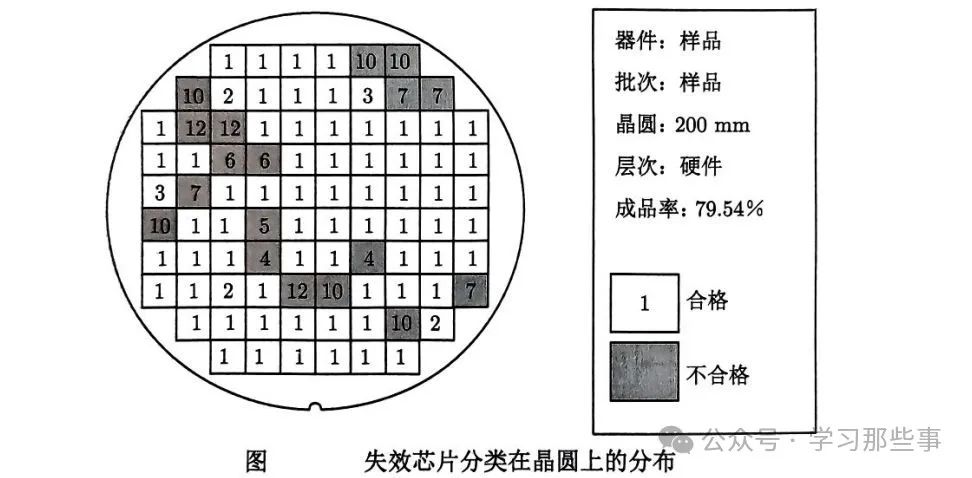

二、失效芯片的“溯源追蹤”

現代測試系統采用失效分類編碼(Binning)體系,將失效模式數字化:

Bin8/9:開路/短路失效,可能源于金屬層刻蝕殘留

Bin12:功能失效,可能涉及IP核設計缺陷

通過空間映射(Mapping)技術,可將編碼數據與晶圓坐標關聯,生成三維失效熱圖。結合制程數據(如機臺編號、批次信息),可實現:

工藝相關失效:如化學機械拋光(CMP)導致的金屬層凹陷

機臺相關失效:某光刻機臺對焦系統漂移引發的套刻偏差

材料相關失效:特定晶圓批次氧化層針孔密度超標

三、行業實踐的演進方向

當前晶圓揀選測試正呈現三大趨勢:

大數據驅動的預測性分析:通過機器學習建立測試數據與工藝參數的關聯模型,實現缺陷預測

云測試平臺:將測試數據上傳云端,進行跨工廠、跨批次的質量追溯

先進封裝適配:針對2.5D/3D封裝需求,增加TSV通孔測試、微凸點檢測等專項測試

作為半導體制造的“質量守門人”,晶圓揀選測試不僅守護著芯片良率的生命線,更通過失效數據的深度挖掘,持續推動著制造工藝的迭代進化。隨著節點向3nm及以下推進,測試技術與工藝開發的協同創新,將成為突破物理極限的關鍵路徑。

2晶圓揀選測試

晶圓揀選測試——半導體質量的“三重防火墻”

在半導體制造中,晶圓揀選測試(Wafer Sort)通過直流測試(DC Test)、輸出檢查(Output Check)和功能測試(Functional Test)構建起芯片質量的“三重防火墻”。這三類測試從電氣特性、性能參數到邏輯功能,對芯片進行全方位“體檢”,確保只有合格的芯片進入封裝階段。以下從行業實踐角度,對三類測試進行技術拆解與案例分享。

一、直流測試(DC Test):芯片的“基礎體檢”

直流測試是芯片質量的“第一道關卡”,聚焦于芯片的靜態電氣特性,核心目標包括:

1.連接性驗證(Continuity Check)

測試原理:通過探針卡與芯片壓點(Pad)的物理接觸,檢測每根探針與對應焊盤的導通性。

行業價值:避免因探針接觸不良導致的“假性失效”,例如探針微小偏移可能引發開路誤判,需通過低阻值閾值(通常<10Ω)確認接觸可靠性。

2.開路/短路檢測(Open/Short Test)

短路:端口間電阻<10Ω(閾值因工藝而異),可能由金屬層刻蝕殘留或光刻膠殘留導致。

開路:端口間電阻>1MΩ,常見于通孔未打通或金屬線斷裂。

案例:某12英寸晶圓邊緣出現規律性開路失效,經分析為化學機械拋光(CMP)工藝壓力不均導致金屬層斷裂。

3.漏電流測試(Leakage Test)

測試對象:截止態晶體管(如CMOS的PMOS/NMOS)或ESD保護電路。

行業挑戰:隨著節點推進至5nm以下,量子隧穿效應導致亞閾值漏電顯著增加,需通過IDDQ測試(靜態漏電流測試)篩選高漏電芯片。

標準參考:工業界通常要求漏電流<1μA/門(Gate),否則芯片可能因靜態功耗超標被淘汰。

二、輸出檢查(Output Check):性能的“壓力測試”

輸出檢查聚焦于芯片輸出端口的驅動能力,模擬實際工作負載條件,驗證其帶負載能力:

1.灌電流(Sink Current)與拉電流(Source Current)測試

測試方法:

灌電流:在輸出端施加低電平(如0V),測量可吸入的最大電流(如8mA),同時檢測低電平電壓(VOL)是否≤0.4V。

拉電流:在輸出端施加高電平(如VDD),測量可輸出的最大電流(如4mA),同時檢測高電平電壓(VOH)是否≥0.8VDD。

行業意義:輸出電平穩定性直接影響芯片與其他器件的信號完整性。例如,某款MCU因輸出驅動能力不足,導致I2C總線在長距離傳輸時信號失真。

2.動態負載模擬

先進實踐:通過可編程負載板模擬電容性負載(如10pF~50pF),測試輸出信號的上升/下降時間(Tr/Tf)。

案例:某高速接口芯片在50Ω負載下Tr=0.5ns達標,但接入10pF電容后Tr延遲至2ns,需優化輸出級驅動電路。

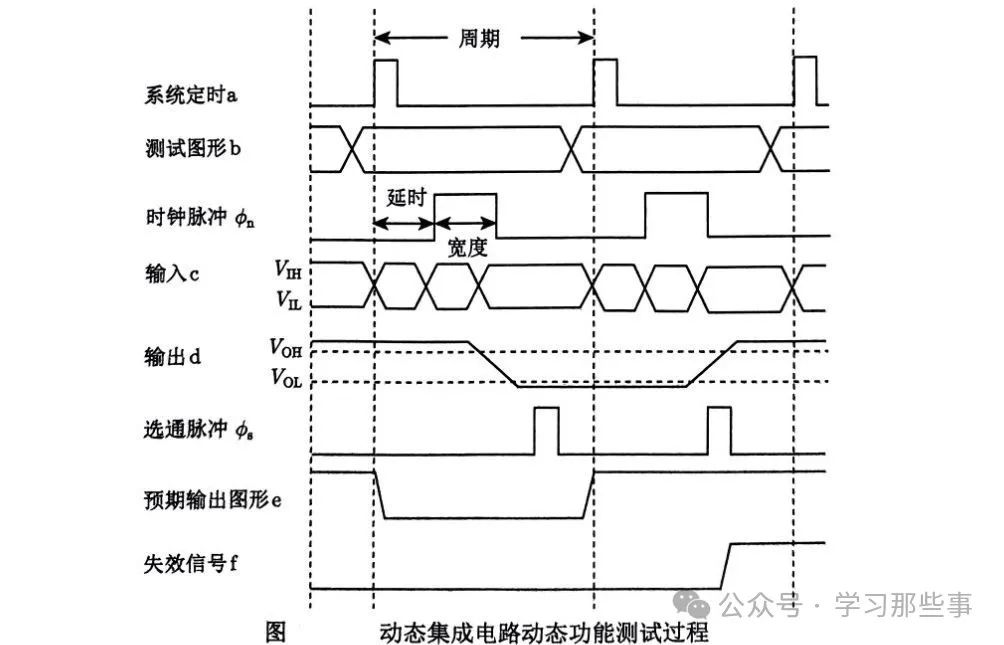

三、功能測試(Functional Test):邏輯的“全場景驗證”

功能測試是芯片質量的“終極考驗”,通過輸入測試向量(Test Pattern)驗證邏輯正確性,覆蓋數字電路與存儲器兩大領域。

1. 數字電路功能測試

測試流程:

測試向量生成:采用ATPG(自動測試模式生成)工具生成覆蓋所有故障模型的向量(如Stuck-at、Transition、Path Delay)。

動態測試:通過時鐘脈沖(CLK)驅動輸入信號,比較器(Comparator)實時檢測輸出電平(VOH/VOL)是否符合規范。

故障診斷:若輸出與預期不符,通過故障字典定位到具體門電路或節點。

行業挑戰:

測試覆蓋率:需覆蓋99.9%以上的邏輯門,但先進工藝中隨機缺陷(如橋接、開路)仍可能導致逃逸。

測試時間優化:采用壓縮算法(如CompactTest)將測試時間從數小時壓縮至分鐘級。

2. 存儲器功能測試

存儲器測試需覆蓋地址譯碼、存儲陣列、讀出放大器等模塊,常見故障包括:

硬故障(Hard Fault):

地址多重選擇:一個地址選中多個單元(如字線短路)。

存儲內容固定:無論寫入何值,讀出數據恒為“0”或“1”(如晶體管閾值電壓漂移)。

軟故障(Soft Fault):

讀后恢復時間過長:讀出放大器在連續讀取相同數據后,無法快速切換狀態(如電荷泵響應延遲)。

寫后恢復時間過長:寫操作后需等待一定時間才能讀取正確數據(如位線電容放電不充分)。

測試方法:

March算法:通過遞增/遞減地址序列,檢測相鄰單元干擾(如March C+算法可覆蓋95%以上的存儲器故障)。

IDDQ測試:檢測靜態漏電,篩查字線/位線短路等隱蔽故障。

行業趨勢:從測試到數據驅動的工藝優化

現代晶圓揀選測試已超越“質檢”范疇,成為工藝優化的數據引擎:

大數據分析:通過測試數據與機臺參數(如光刻機曝光能量、刻蝕機腔體壓力)的關聯分析,實現故障根源追溯。

AI賦能測試:采用機器學習模型預測測試逃逸率,動態調整測試向量優先級。

云測試平臺:將測試數據上傳至云端,支持跨工廠、跨批次的良率對比與缺陷共享。

3晶圓揀選測試核心要點

晶圓揀選測試核心要點:效率、精度與可靠性的三角平衡

在半導體制造中,晶圓揀選測試(Wafer Sort)是芯片從晶圓到封裝的關鍵質控環節,其核心目標是在最短測試時間內,精準篩選出合格芯片,同時為工藝優化提供數據支撐。隨著集成電路規模突破百億級晶體管,測試效率與缺陷覆蓋率的矛盾日益凸顯。以下從行業實踐角度,對晶圓揀選測試的四大核心要點進行技術解析。

一、測試消耗時間:效率與成本的博弈

測試時間直接關聯到制造成本與產能利用率。以超大規模集成電路(VLSI)為例,其測試時間可能長達數小時,成為產能瓶頸。優化測試時間需從設計源頭入手:

1.可測性設計(DFT)

內建自測試(BIST):在芯片設計中嵌入專用測試電路(如掃描鏈、MBIST控制器),繞過功能路徑直接對關鍵模塊(如存儲器、鎖相環)進行自檢。例如,某款AI芯片通過BIST將測試時間從4小時壓縮至30分鐘。

并行測試:對數字、模擬、射頻等混合信號電路實施同步測試。例如,某5G SoC芯片通過數字-模擬并行測試,將測試時間減少40%。

2.測試算法優化

壓縮技術:采用差分測試向量壓縮算法(如Golomb編碼),將測試數據量減少50%以上。

自適應測試:根據前序測試結果動態調整后續測試向量,避免冗余操作。

二、失效模式:從“癥狀”到“病因”的溯源

集成電路故障可歸納為三大類,其檢測需針對性設計測試向量:

1.固定故障(Stuck-at Fault)

表現:節點邏輯值永久固定為“0”或“1”,可能由晶體管柵氧擊穿或金屬層開路導致。

檢測:通過全“0”/全“1”測試圖形或March算法覆蓋99%以上的固定故障。

2.橋接故障(Bridging Fault)

表現:非連接節點間意外導通(如金屬層刻蝕殘留導致相鄰線短路)。

檢測:棋盤測試圖形可檢測相鄰單元干擾,但需結合電子束檢測(EBI)定位物理缺陷。

3.延遲故障(Delay Fault)

表現:信號傳輸時序違反規范(如建立/保持時間不足),可能由互連線RC延遲增大導致。

檢測:通過動態測試(At-Speed Test)在最高工作頻率下施加時序緊張的測試向量。

三、靜態漏電流測試(IDDQ Testing):缺陷的“顯微鏡”

IDDQ測試通過測量靜態漏電流(通常為nA級)檢測隱蔽缺陷,其原理基于CMOS電路的互補特性:

1.測試原理

正常CMOS電路在靜態時,PMOS與NMOS管中僅有一個導通,漏電流極小(<1μA)。

工藝缺陷(如柵氧針孔、金屬層空洞)可能導致漏電流激增至μA級甚至mA級。

2.行業價值

缺陷覆蓋率提升:可檢測傳統功能測試無法覆蓋的缺陷(如亞閾值漏電)。

工藝監控:IDDQ分布可反映光刻、刻蝕等關鍵工藝的穩定性。

3.局限性

診斷困難:IDDQ異常僅能提示缺陷存在,需結合物理失效分析(PFA)定位根源。

先進工藝挑戰:FinFET及GAA晶體管導致漏電基準降低,需升級測試設備精度。

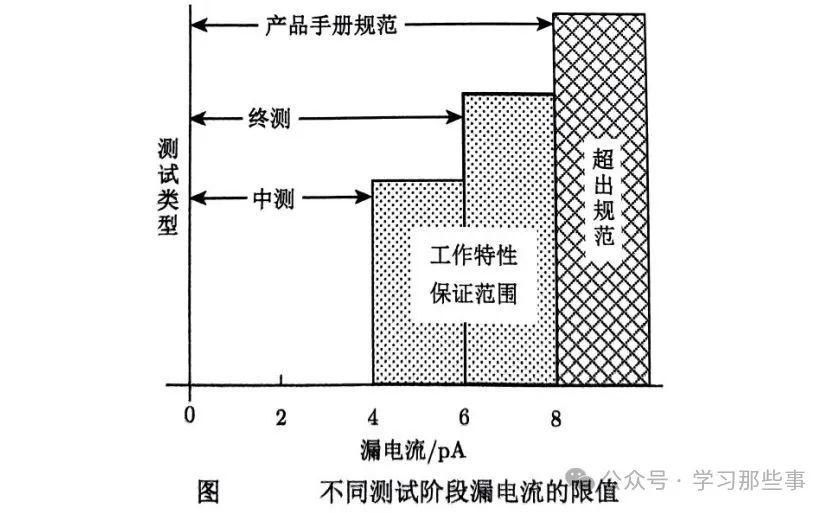

四、正常工作保障范圍測試:可靠性的“護城河”

為確保芯片在全生命周期內可靠工作,需在測試階段設置比規格更嚴苛的限值:

1.guard banding策略

漏電限值加嚴:例如,用戶規格為8pA漏電,中測階段采用4pA限值,終測階段采用6pA限值,以抵消工藝波動與測試誤差。

電壓/溫度裕量:在高溫(125℃)或低壓(VDD-10%)條件下驗證功能正確性。

行業案例

汽車電子:AEC-Q100標準要求芯片在-40℃~150℃范圍內通過動態測試,漏電流限值比消費級產品嚴格50%。

數據中心CPU:通過加速壽命測試(ALT)模擬10年使用場景,確保IDDQ在壽命末期仍低于規格。

五、行業趨勢:從“被動檢測”到“主動預防”

現代晶圓揀選測試正呈現兩大趨勢:

AI賦能測試:通過機器學習模型預測測試逃逸率,動態調整測試向量優先級。例如,某代工廠利用AI將測試時間減少30%,同時保持99.9%的故障覆蓋率。

云測試平臺:將測試數據上傳至云端,進行跨工廠、跨批次的良率對比與缺陷共享。例如,某IDM企業通過云平臺實現全球Fab數據實時分析,將缺陷定位時間從數天縮短至數小時。

晶圓揀選測試的四大要點——測試時間優化、失效模式分析、靜態漏電流檢測與保障范圍測試,構成了半導體制造的“效率-精度-可靠性”三角平衡。隨著節點向2nm及以下推進,測試技術與工藝開發的協同創新,將成為突破物理極限、保障芯片性能的關鍵路徑。

-

集成電路

+關注

關注

5422文章

12021瀏覽量

368035 -

半導體

+關注

關注

335文章

28817瀏覽量

235968 -

晶圓

+關注

關注

53文章

5140瀏覽量

129602

原文標題:半導體制造的質量守門人——晶圓揀選測試

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

晶圓制造工藝的流程是什么樣的?

晶圓測試探針臺的組成以及晶圓測試的重要性和要求

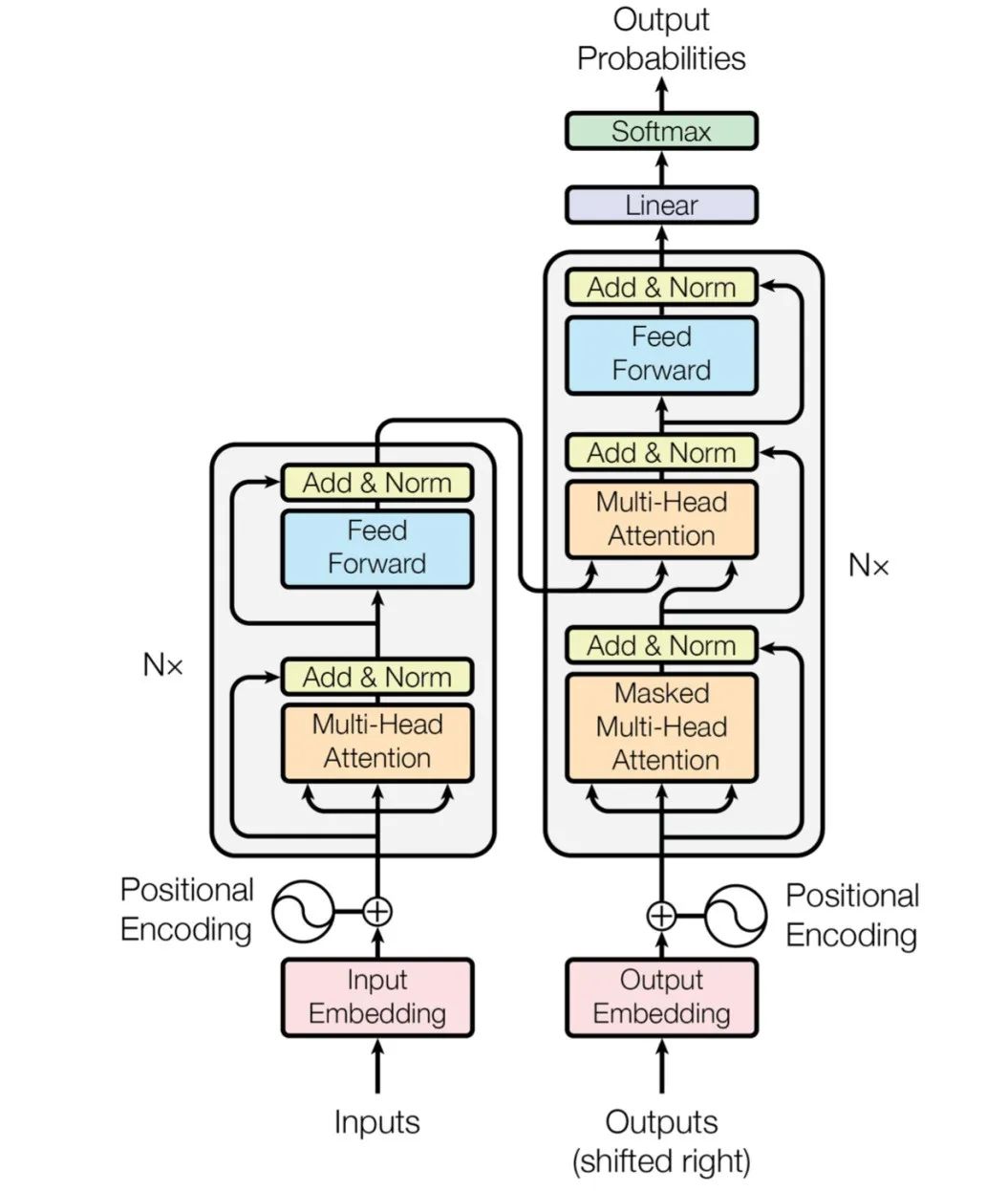

ChatGPT的核心要點

晶圓揀選測試的具體過程和核心要點

晶圓揀選測試的具體過程和核心要點

評論