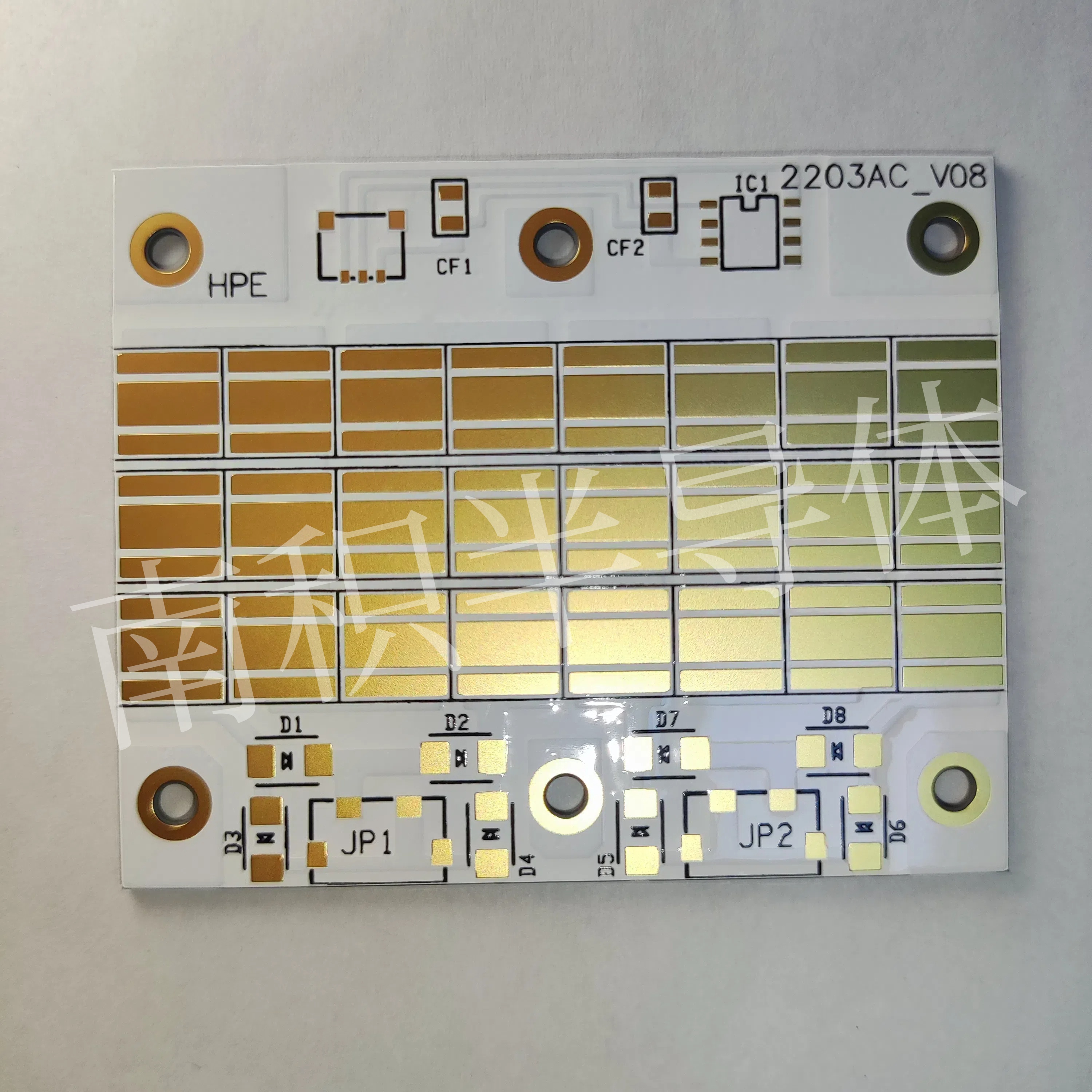

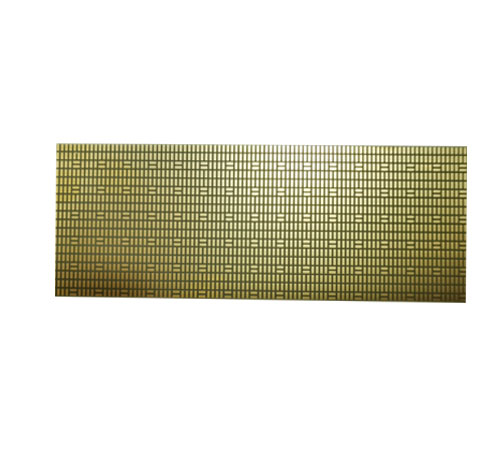

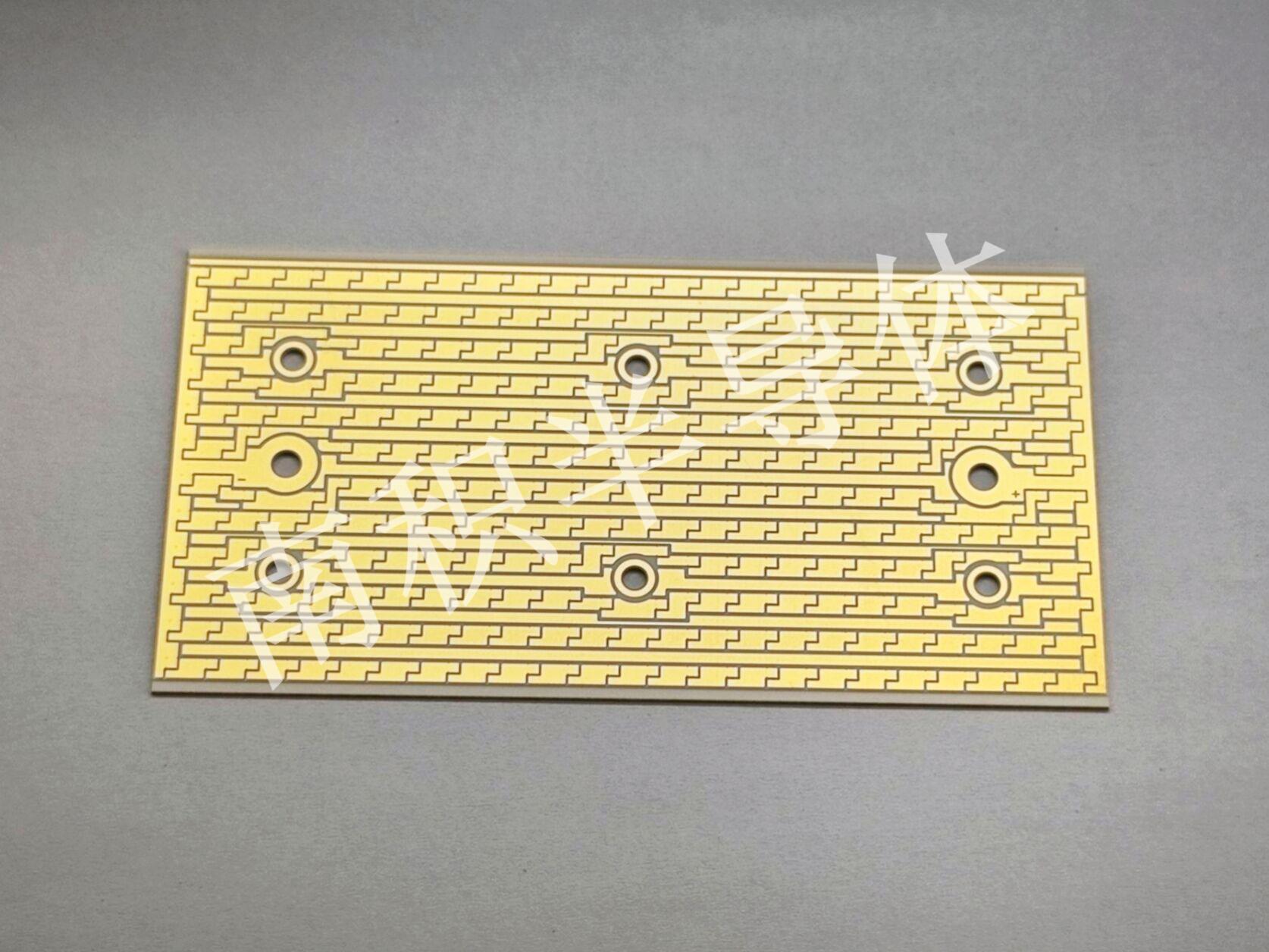

在現代電子封裝領域,氮化硅(Si?N?)AMB陶瓷覆銅基板憑借其卓越的熱導率、低熱膨脹系數以及優異的電氣絕緣性能,逐漸成為高端電子設備的關鍵材料。然而,銅/陶瓷界面的空洞率問題卻成為了制約其產品可靠性的核心瓶頸。高空洞率區域不僅會導致界面剝離強度顯著下降,還可能引發局部放電隱患,嚴重損害基板的電氣性能與長期服役可靠性,尤其是在高溫、大電流等嚴苛工況下。因此,將界面空洞率降至最低,甚至趨近于零,已成為保障基板質量的關鍵目標,下面由深圳金瑞欣小編來講解一下:

空洞成因的深度解析

1、原料表面瑕疵

陶瓷、無氧銅及焊片表面的劃痕、凹坑、氧化或有機污染等問題,猶如隱形的“陷阱”,阻礙了焊料的潤濕鋪展,為界面空洞的形成埋下了隱患。這些微小的瑕疵在焊接過程中可能會導致焊料無法充分覆蓋,從而形成空洞。

2、活性元素失活

焊料中的關鍵活性元素鈦(Ti)極為敏感,極易在氧化環境中失去活性。若真空釬焊環境的真空度不足(需優于10?3 Pa),Ti的活性將被削弱,焊料便無法有效潤濕陶瓷,進而引發大面積虛焊、漏焊現象,直接導致空洞的產生。

3、釬焊工藝失當

Ag-Cu-Ti焊料需要在800℃以上的高溫條件下才能有效潤濕Si?N?表面。若焊接溫度過低或保溫時間過短,Ti與陶瓷的反應將不充分,焊料的潤濕性也會大打折扣,從而導致空洞的形成。

4、焊膏印刷缺陷

在大面積焊膏印刷過程中,漏印、不均勻等問題時有發生。當焊料熔化后,若未能完全覆蓋這些缺陷區域,便會在基板內部形成直接空洞。

5、焊膏揮發與放氣

釬焊過程中,焊膏的揮發氣體以及助焊劑中有機酸與金屬氧化物反應產生的氣泡,可能會被助焊劑包裹,或者滯留在界面處。如果這些氣泡未能及時排出,在焊料凝固后便會形成空洞。

6、降低空洞率的有效策略

1、基礎保障:嚴格表面處理與高真空環境

對Si?N?陶瓷和銅片進行徹底的除油、除氧化處理,是確保焊接質量的前提。同時,必須提供并維持真空度優于10?3 Pa的高真空釬焊環境,以防止Ti氧化失活,從而為后續的焊接工藝奠定堅實基礎。

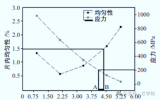

2、核心要素:優化釬焊壓力

研究表明,釬焊壓力是影響空洞率的最主要工藝參數之一。增大壓力不僅能促進母材與焊料的緊密接觸,加速接觸反應熔化,還能增強熔化焊料的流動性,有效擠出界面氣體,從而顯著減少空洞的形成。這一結論在張義政等人的AMB工藝研究以及賈耀平等人的真空共晶焊接研究中均得到了證實。

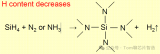

3、氣氛探索:惰性氣體輔助

在微波模塊焊接中,真空+氮氣混合氣氛相較于單純真空環境,能夠更有效地降低空洞率。這一發現對AMB工藝具有重要的啟發意義。然而,需要注意的是,在高溫條件下,氮氣可能會與Ti發生反應,因此氦氣、氬氣等惰性氣體或許會是AMB工藝中更安全的選擇。

現狀與未來方向

目前,銀銅鈦焊膏因其工藝簡單、成本低、易儲存等優點,依然是國內AMB工藝的主流選擇。然而,針對焊膏焊接過程中空洞率的降低措施,國內外文獻鮮有深入報道。這無疑也成為了未來工藝突破的重要方向之一。

總結

攻克Si?N?-AMB基板銅/陶瓷界面空洞難題,需要從原料表面質量管控、高真空環境保障、精確優化釬焊壓力(作為關鍵抓手)以及探索惰性氣體輔助等方面協同發力。唯有將界面空洞率降至最低,甚至趨近于零,才能確保基板在嚴苛工況下的高可靠運行,從而推動國產高端陶瓷基板的技術突圍,助力我國電子封裝行業邁向更高水平。

金瑞欣作為擁有十多年歷史的特陶瓷電路板廠家,始終致力于電路板的研發生產。擁有先進陶瓷生產設備和技術,以快速的交期和穩定的品質滿足客戶的研發進程和生產需要,品質優先,占領市場先機。陶瓷板交期打樣7~10天,批量10~15天,具體交期要看陶瓷電路板圖紙、加工要求及其難度,快速為您定制交期,以“品質零缺陷”為宗旨,提供優質的產品和服務。若您有相關需求,歡迎與我們聯系,我們將竭誠為您服務。

-

AMB

+關注

關注

0文章

24瀏覽量

6115 -

陶瓷基板

+關注

關注

5文章

241瀏覽量

11809 -

氮化硅

+關注

關注

0文章

82瀏覽量

498

發布評論請先 登錄

DPC陶瓷覆銅板:高性能電子封裝的關鍵技術

EAB450M12XM3全碳化硅半橋功率模塊CREE

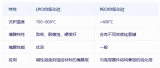

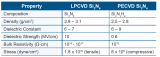

通過LPCVD制備氮化硅低應力膜

氮化硅在芯片制造中的核心作用

陶瓷基板五大工藝技術深度剖析:DPC、AMB、DBC、HTCC與LTCC的卓越表現

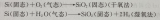

LPCVD氮化硅薄膜生長的機理

氮化硅薄膜的特性及制備方法

氮化硅薄膜制備方法及用途

氮化硅AMB陶瓷覆銅基板界面空洞率的關鍵技術與工藝探索

氮化硅AMB陶瓷覆銅基板界面空洞率的關鍵技術與工藝探索

評論